突发模式通信中MMPE位同步方法的实现

2011-03-05丁丹

丁 丹

(装备指挥技术学院光电装备系,北京 101416)

1 引 言

在突发模式通信中,信号的持续时间较短,接收端所面临的难题是既快又准地找出最佳判决点。突发模式下位同步应该基于这样的思想:收发两端的频率源工作在稳定、独立的频率上,定时误差的提取由数字信号处理算法来完成,误差信号不再反馈去控制NCO,而是用来驱动相应的算法,从接收信号中估计定时误差,获取近似最佳的判决值,但相关文献[1,2]所研究的方法往往过于复杂,难于硬件实现。本文研究的最大平均功率 (Maximum Mean Power Estimation,MMPE)位同步方法利用接收信号中平均功率最大的采样时刻来估计最佳采样点,易于硬件实现。

2 MMPE位同步方法的理论分析

应用项目中,调制方式为 PSK,数据率为256 kbit/s。接收端PSK中频信号经过下变频、成形后的基带信号为

采样信号r(k)的功率为

因为零均值高斯白噪声与符号是相互独立的,所以上式可化简为

上式说明功率的期望值与载波频偏、相位无关,只与系统的冲激响应和时延有关。当收发两端的滤波器共轭匹配且g(kT0)满足Nyquist第一准则时,最大平均功率输出时刻就对应了最佳判决时刻。所求的最佳判决时刻为

对应的最大平均功率为

3 观察区间长度L的选取

现在通过MATLAB仿真[4]来讨论如何选取合适的观察区间长度L。先产生L个0、1交替的符号,每符号10个采样点,用滚降系数为0.35的升余弦滤波器对其成形(可以通过设定固定延时来规定最佳判决点的位置),并加上高斯白噪声,来模拟接收端成形后的基带信号。在这 L(取6、10、14、18)个符号内计算平均功率分布,取平均功率最大的采样点为判决点,重复运行10000次。图1和图2分别显示了不同信噪比、不同L条件下取到最佳判决点的概率以及最大定时偏差。

图1 不同信噪比、不同L条件下取到最佳判决点的概率Fig.1 The probability of getting the best decision point under different SNR and L

图2 不同信噪比、不同L条件下的最大定时偏差Fig.2 The maximum timing difference under different SNR and L

由仿真结果可看出:L越长,位同步精度越高,但同时也会导致软、硬件资源的消耗越大,所以需折衷选择L。仿真结果显示,若取L=10,则在信噪比不小于10dB时,取到最佳判决点的概率不小于80%,定时偏差不大于符号周期的10%,满足一般工程实践的要求,而且经过下变频、滤波抽取、成形滤波后,噪声功率已大为减弱,所以这里选择L=10。

4 MMPE位同步方法的实现

用FPGA和DSP配合实现MMPE算法,如图3所示。FPGA选用Altera公司Cyclone IV系列中的EP4CE30,DSP选用TI公司的TMS320VC6416。符号时钟和判决脉冲都由采样时钟10分频得到,10分频器是可编程的,它根据DSP写入的最佳判决位置来调整判决脉冲的相位,使得判决脉冲的上升沿对应最佳判决点。I、Q两路的内插结果在采样时钟的触发下进行I2+Q2运算,得到当前采样点的功率,此功率值在采样时钟的触发下依次经过10级延迟器,这样在每符号周期末,10级延迟器就分别记录了该符号周期内10个采样点的功率值。这时由10个累加器分别对10个采样点的功率值进行一次累加,累加器的触发时钟为符号时钟,每帧开始时由DSP对累加器清零,10个符号的前导信息接收完毕时所有的累加器都进行了10次累加,其结果P1~P10分别为各采样点平均功率的10倍。这时DSP往FPGA中的多任务器写相应的选择控制字,来顺序读取P1~P10,并比较它们的大小,最大值点即为最佳判决点,最后将最佳判决位置写入10分频器。

图3 MMPE算法的FPGA+DSP实现Fig.3 The implementation ofmmPE based on FPGA and DSP

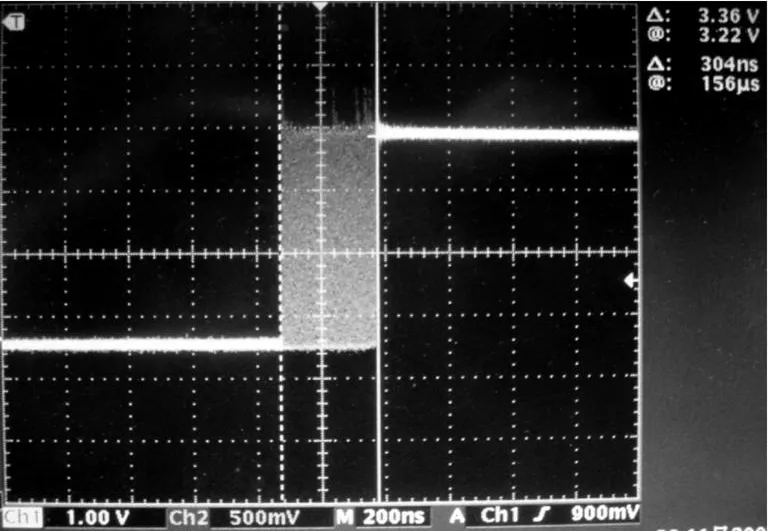

图4 判决脉冲上升沿抖动范围实测图Fig.4 The measured dithering range of decision pulse high event

用示波器观测位同步的精度,对判决脉冲上升沿处进行局部放大并显示其包络,如图4所示。两条垂直光标间的范围代表上升沿的抖动轨迹,示波器显示上升沿抖动范围在304 ns以内,而符号周期为1/256=3.9 μ s,所以时钟抖动小于符号周期的8%,与仿真结果吻合,完全满足正确判决的要求。

5 结 语

最大平均功率位同步方法以平均功率最大的采样点为判决点,利用一定长度的前导信息可以一次性找到最佳判决点,锁定速度快,且实现方法简单、易于数字化硬件实现。此方法适用于各种突发模式通信系统,已成功应用于某型战场单兵侦察系统,获得了良好效果。其缺点是位同步的精度同软、硬件资源的消耗成正比,需折衷考虑。

[1]王勇,屈晨阳.一种适用于全数字接收机的位同步系统的设计[J].微计算机信息,2010(23):164-165.WANG Yong,QU Chen-yang.The Design of a Symbol Timing Synchronization System for All Digital Receiver[J].Microcomputer Information,2010(23):164-165.(in Chinese)

[2]陈寅芳,朱勇,曹彦武.基于FPGA的突发误码测试仪的设计[J].光通信技术,2010,34(4):45-48.CHEN Yin-fang,ZHU Yong,CAO Yan-wu.The design of burst error detector based on FPGA[J].Optical Communication Technology,2010,34(4):45-48.(in Chinese)

[3]樊昌信,曹丽娜.通信原理[M].北京:国防工业出版社,2009:51.FAN Chang-xin,CAO Li-na.Communication Theory[M].Beijing:National Defense Industry Press,2009:51.(in Chinese)

[4]赵刚.扩频通信系统实用仿真技术[M].北京:国防工业出版社,2009:11-27.ZHAO Gang.The simulation technology of spread spectrum communication system[M].Beijing:National Defense Industry Press,2009:11-27.(in Chinese)