基于AD9954的多模式调制器的设计

2011-01-27雷求胜

雷求胜,唐 宁,陈 科

(桂林电子科技大学 信息与通信学院,广西 桂林 541004)

软件无线电是近年来提出的一种新的无线通信体系结构。它最初起源于军事通信,是以开放的、可扩展的、结构最简的硬件为通用平台,把尽可能多的功能用可升级、可替换的软件来实现。软件无线电的出现大大减小了硬件对通信系统的束缚,通过加载软件就可以实现各种无线通信功能。

如何产生多种调制信号,一直是大家讨论和关注的热点。本文提出的方案就是基于超高速、先进DDS技术的数字中频处理技术的方法,利用美AD公司推出的AD9954构建一个硬件平台,结合相应的数字处理软件和控制软件,获得多种调制信号。一方面由于体积变小,使用起来很方便,另一方面也大大降低了成本[1]。

1 DDS的原理介绍

直接数字频率合成器DDS是近年来发展起来的一种新的基于查找表的频率合成技术。典型的DDS由相位累加器、ROM波形存储表、D/A转换器(Digital-to-Analog Converter,DAC)和低通滤波器(Low Passed Filter,LPF)组成,如图1所示。

图1 可编程DDS的系统原理框图Fig.1 System principle block diagram of DDS

相位累加器由N位加法器与N位累加寄存器级联构成。每来一个时钟脉冲fs,加法器将频率控制字FTW与累加寄存器输出的累加相位数据相加,把相加后的结果送至累加寄存器的数据输入端。累加寄存器将加法器在上一个时钟脉冲作用后所产生的新相位数据反馈到加法器的输入端,使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。由此可以看出,相位累加器在每一个时钟脉冲输入时,把频率控制字累加1次,相位累加器输出的数据就是合成信号的相位,相位累加器的溢出频率就是DDS输出的信号频率[2]。

用相位累加器输出的数据作为波形存储(ROM)的相位取样地址,这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完成相位到幅值转换。波形存储器的输出送到D/A转换器,D/A转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号。低通滤波器用于滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。

若相位累加器的位数为N,改变频率控制字FTW或参考时钟fs,就可以改变输出频率fo:

DDS在相对带宽、频率转换时间、高分辨率、相位连续性、正交输出以及集成化等一系列性能指标方面远远超过了传统频率合成技术所能达到的水平,为系统提供了优于模拟信号源的性能。

2 AD9954芯片的介绍

2.1 AD9954的主要性能特性[3]

1)DDS 采样率可达 400 MSPS;2)内置 14 位 DAC;3)32位相位累加器;4)波特率达 25 M 的 SPI接口;5)内置 1 024×32位RAM,可实现内部调制;6)内部采用1.8 V供电,超低功耗;7)可自动线性和非线性扫频。

2.2 AD9954的原理及工作过程

AD9954是采用先进的DDS技术开发的高集成度DDS器件。该芯片的速度是业界第一个时钟达到400 MHz,合成技术高达160 MHz,功耗200 mW。以前产品的合成频率只有120 MHz且功耗却有2 W。它能使设计者采用DDS在功率敏感的应用中在更高频率输出进行快速跳频[4]。

AD9954作为新型DDS系列的旗舰产品,内置高速、高性能14位DAC,它内含1 024×32静态RAM,可实现高速调制,并支持几种快速扫频模式和精细的调谐分辨率(32位频率调谐字)。可提供自定义的线性扫频操作模式,采用自动线性和非线性扫描功能来控制频率调谐和相位,其中频率调谐和控制字通过串行I/O口加载到AD9954,可实现多片同步。

3 系统设计原理框图

多种调制信号平台由 TI的430单片机、Altera公司的FPGA、AD公司的AD9954、外围的滤波和整形电路搭建而成。其中以AD9954为核心元器件来产生原始的所需波形,如图2所示。

图2 系统设计原理框图Fig.2 Principle block diagram of system design

通过MCU控制FPGA的调制类型状态和DDS调制芯片的寄存器数值,完成利用人机界面对整体电路的控制和配置过程。FPGA将A/D转换过后的基带信号通过确定的调制方式再经相应的转换送入DDS调制IC中。DDS的输出信号经功率放大后再进行输出。

AD9954的串口与FPGA相连,FPGA通过 AD9954的CS、SCLK、SDIO和SDO管脚向AD9954写入数据和控制字。首先设置特定的寄存器控制字,允许RAM工作,接着将RAM输出作为相位累加器的输入给芯片提供频率转换字,然后写好RAM段控制寄存器的值,定义起始地址、终止地址并选择工作模式。例如,在RAM地址256~511中写入计算好的频率值,主要操作过程如下:

1)允许RAM操作,清除CFR<30>;2)选择模式5即连续循环模式;3)选择 RAM 段 1,PS0=1,PS1=0;4)指令字节为00001001;5)定义通信阶段的通信周期数为256,把数据写入RAM存储器地址256~511中;6)改变I/O UPDATE启动模式工作。

本系统可由地址的变化速率来计算调制速度,地址变化速率RAM段控制寄存器中的地址变化率控制字决定,其值的范围是1~65 535,定义的时间是SYNC_CLK的周期数。由于SYNC_CLK最大为100 MHz,从而决定了地址变化率控制字为1时能定义的最快速度为100 MHz,假设一个波形要采集256个点,那么调制速度为100 MHz/256=400 kHz;如果采样点为100个,则调制速度可达100 MHz/100=1 MHz。由于AD9954产生的调制波形采样点多,采样时间精确,因此波形性能较好。

4 输出信号介绍及设置AD9954中的寄存器

4.1 正弦信号

正弦波信号广泛地应用于通信系统中,它可以作为载波信号来进行数字系统的调制,这不仅仅是因为它容易产生,最主要的是它便于接收并且形式简单。其数学表达式为:

平台上的实现:AD9954首先通过关闭RAM模式和线性扫频模式来实现单频模式,然后设置频率字设置寄存器1来实现要获得的频率。它的频率计算公式如下:[3-6]

4.2 线性调频信号

线性调频信号是一种发射脉冲信号在信息脉冲持续时间T内作线性变化,其瞬时频率随时间线性变化。这种信号的产生可以由一个锯齿波控制压控振荡器实现,振荡频率随锯齿波而变化,因此脉冲信号的载频从原来单一频率展宽为一个频带。可以用以下表达式来说明这个过程:

式中ω0为载波频率的初始值,u为一个常数,因此线性调频信号的瞬时相位声φ(t)和线性调频信号在信息脉冲持续时间T内的表达式 s(t)分别为:

平台上的实现:在AD9954中通过设置控制寄存器CFR1的21位为1来实现这一功能,分别向两个频率字设置寄存器FTWl和FTW2写入扫频的起始频率和结束频率,指定频差。对线性扫频每次的步长通过线性扫频控制字来设定,同时值得指出的是,可以选择从低频率到高频率的扫频,也可以选择从高频率到低频率的扫频。

4.3 FSK调制信号

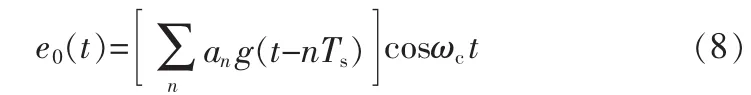

FSK信号也可以分为2FSK信号和多进制数字频率调制。2FSK信号是由信息源符号1和0对应于不同的两个载频来实现调制的一种方式。其数学表达式为[5]:

其中,g(t)为单个矩形脉冲,脉宽为 Ts,

由于AD9954具有4个不同的RAM区,因此也可以实现四进制的频率调制,其实现方式与相位调制类似。

4.4 BPSK,QPSK调制信号

BPSK,QPSK信号是载波相位按照基带脉冲而改变的一种数字调制方式。BPSK和QPSK信号的表达式分别为:

g(t)是脉冲为Ts的单个矩形脉冲,其中:

g(t)是脉冲为 L 的单个矩形脉冲,其中:ak=cosψk,bk=sinψk(ψk为受调相位)[5]

在这里实现的只是绝对移相方式,对于BPSK而言,是按照1对应相位π,0对应相位0的方式来实现的;对于QPSK信号,则是由2 bit脉冲信号的4种不同状态来选择4种不同的相位,4 种相位有 2 组形式, 可选择 0,π/2,3π/2,7π/2 和π/4,3π/4,5π/4,7π/4 中的任意一组作为参考相位。

要实现上述调制信号,必须使AD9954工作在RAM模式下,通过设置控制寄存器CFR1的21位为0,同时配合外部片选信号PS0,PSl来实现4个RAM区的转换。每个RAM区的首地址中存储的是相位信息。在这种模式下,RAM中存储的数据就会作为相位累加器的相位输人。选择不同的RAM区,就会选择不同的初始参考相位,从而达到相位调制的目的。

5 软件系统设计

5.1 单片机编程

采用中断的方式对AD9954写入控制字,在每写完一个控制字命令周期后,主机向AD9954发送一个更新信号,进入下一个控制命令字周期的写入。在每写完8 bit数据后就进行一次中断,每中断一次后设置标志位,等待下一次中断[7]。

主程序根据键盘选择调制方式,按确定后选择需要的调制信号,流程图如图3所示。

图3 系统主程序设计框图Fig.3 Flow chart of system main programme design

5.2 FPGA的编程设计

首先利用FPGA制作1个ROM表,该表中存入的是一组相位信息或者频率信息,然后通过时钟的分频及译码电路获得信息表的地址,将对应地址的内容作为输出,最后通过1个判决电路(二选一电路)来控制输出模式。ROM表中的地址内容可以控制AD9954对实际相位值或实际频率值的选择。

图4 调制信号设计框图Fig.4 Flow chart of modulated signal design

由于FPGA的内部时钟存在一定的不稳定性,因此在这里选用外部稳定的晶振作为输入,一方面提供了稳定的时钟输人,另一方面又可以减小FPGA内部宝贵资源的使用。

6 实验输出波形的时域和频域分析图

6.1 AM信号测试分析

AM系统频域频谱结构和时域解调波形测试结果分别如图5、图6所示。

AM载波频率设置为52.5 MHz,实际测得的中心频率为52.500 663 MHz,频率误差为 0.000 663/52.5=1.263×10-5,误差在系统规定的范围内。

图5 AM调制信号频谱图Fig.5 Frequency spectrum of AM modulating signal

图6 AM解调后的时域波形图Fig.6 Time domain waveform of AM demodulated signal

6.2 2FSK和4PSK信号测试分析

在该平台下生成的FSK和QPSK频谱如图7、图8所示。

图7 2FSK调制信号频谱Fig.7 Frequency spectrogram of 2FSK modulating signal

图8 4PSK调制信号频谱Fig.8 Frequency spectrogram of 4PSK modulating signal

2FSK信号是设置AD9954在Direct Switch模式下进行测试的,AD9954的系统时钟为200 MHz,RAM0和 RAM1设置的频率值分别为9.7 MHz和9.9 MHz。设PS0=0,根据基带信号0或1改变PS1的值为0或1即可产生2FSK信号。将2FSK信号波形数据采集并存储后对其做FFT变换,画出其频谱图如图6所示,可见在9.69 MHz和9.88 MHz有两根谱线,证明采集到的为2FSK信号。

4PSK信号是设置AD9954在Direct Switch模式下进行测试的,AD9954的系统时钟为200 MHz,RAM0、RAM1、RAM2和RAM3设置的频率值分别为 9.7 MHz、10.3 MHz、10 MHz和10.9 MHz。根据基带信号的0或1或2或3改变PS1和PS0的值即可产生4FSK信号。

7 结束语

本文介绍了采用先进DDS技术的AD9954性能特点和工作原理及过程,利用其可编程幅度、频率、相位给出了AD9954在高速调制信号系统中的应用方案,从而较方便地实现基于软件无线电技术的各种调制信号。采用超高速、先进DDS技术的数字中频处理技术的方法,构建AD9954硬件实现平台,结合相应的数字处理软件和控制软件,可获得调幅、噪声调频、FSK、PSK等多种调制信号。本文提出的硬件实现方案,为产生多模式信号提供了硬件平台,具有较好的应用价值。

[1]扬小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001:1-3.

[2]许加枫.高性能DDS芯片AD9954及其应用[J].电子设计工程,2004(11):14-16.XU Jia-feng.The application of high performance DDS of AD9954[J].Electronic design engineering,2004(11):14-16.

[3]Analog Devices lnc.400 MSPS 14-Bit,1.8V CMOS Direct digital synthesizer AD9954 data sheet[EB/OL][2003].http://www.datasheet 5.com/view-3CDEF4D81BFFA4E 2.html.

[4]Srikanteswara S,Reed J H, Athanas P,et al.A soft radio architecture for reconfigurable platform[J].Communications Magazine,IEEE, 2000,38(2):140-147.

[5]樊昌信,张甫诩,徐炳译,等.通信原理[J].5版.北京:国防工业出版社,2001.

[6]谭浩强.C程序设计[M].武汉:华中科技大学出版社,2002.

[7]秦龙.MSP430单片机常用模块与综合系统实例设计[M].北京:电子工业出版社,2007.