一种高速MaskROM的设计研究

2011-01-27冒国均

徐 睿,冒国均

(中国电子科技集团公司第五十八研究所,江苏 无锡 214035)

一种高速MaskROM的设计研究

徐 睿,冒国均

(中国电子科技集团公司第五十八研究所,江苏 无锡 214035)

文章分析讨论了掩模只读存储器的工作原理和结构,并结合实际工作,详细论述了一个高速的576k位MaskROM的设计与实现。针对字线负载大、速度慢的问题,从选择合适的译码方案和减少字线上RC负载两个方面,提高字线的响应速度,从而使MaskROM的读取时间有较大提高。该款MaskROM采用0.5μm CMOS工艺,电源电压5V,读取时间约为12ns,单位功耗约为1.06 mW/MHz。

掩模只读存储器;CMOS;译码;字线;速度

1 引言

只读存储器是各种计算机硬件存储部件中的重要芯片,存人数据以后,不能用简单的方法更改,即在工作时它的存储内容是固定不变的,并且其所存储的信息在断电后仍能保持,常用于存放固定不变的二进制数码。只读存储器分为掩模只读存储器(MaskROM)、可编程只读存储器(PROM)和可擦除可编程只读存储器(EPROM)等几大类。掩模只读存储器由于其高可靠性和低廉的成本,广泛应用于各个数字技术领域。

本文所述的MaskROM设计中,速度是最主要的优化目标,同时兼顾功耗和面积的优化。该ROM容量为576k位,可以通过CE、OE及三态驱动实现存储,要求读取时间在12ns以内,采用基于0.5μm的高性能CMOS工艺,正向完成全部设计工作。

2 ROM基本结构分析

2.1 存储阵列结构选择

MaskROM主要由存储陈列、参考电压产生模块、译码模块和逻辑控制等模块组成,功能框图见图1。在大容量MaskROM的设计中,存储阵列占了绝大部分芯片面积,基本存储单元的大小直接决定了MaskROM的成本。常见的存储单元结构主要有NAND和NOR两种:NAND类型结构的MOS管串行连接,由晶体管的增强或耗尽模式来确定存储数据的值,尺寸较小,但较大的寄生电阻和寄生电容严重制约了速度;传统的NOR类型结构中的MOS管并行连接,由晶体管金属到扩散区接触孔的有无来确定存储数据的值,存储速度较快,但尺寸较大。

本文所述的MaskROM的单元阵列由字线、位线、上拉管、单元管组成。ROM单元采用NMOS管、NOR结构。用NMOS管作单元的优点在于不需要通过字线对位线直接充电,减小了字线负载。实际设计中,版图上预留出所有MOS管单元的位置,通过是否将MOS管漏极接到位线上来控制是否有MOS管单元,通过软件编程将指定的ROM码点内容转成版图上相应的连接。

2.2 整体功能结构设计

在存储阵列中,字线和位线都是较长的金属连线,具有较大的负载和延迟。对于大容量的存储器,如果采用传统的全局布线结构,构建单一的整块存储阵列结构,必然导致非常大的数据读取延时和连线负载,从而严重制约整个存储器的读取速度,所以必须对存储阵列进行分体、分模块处理。现将整个64k×9 bit阵列划分为32×128×16×9 bit阵列,即32个容量为18k bit的子存储体,每个子存储体又包含128行×16列的9 bit存储单元,整体结构图见图2。子存储体的选择由高5位地址信号(Addl5~Addl1)来控制,而行、列选择信号则由中7位的地址信号(Add10~Add4)与低4位的地址信号(Add3~Add0)译码产生。这样的分体、分块方式,可以有效提高存储器的访问效率并缩短寻址时间,同时缩短字线和位线的连线长度而减小延迟,从而提高ROM的整体运作速度。

3 译码部分的优化设计

ROM的读出时间主要由四部分组成,分别是输入缓冲器延时、地址译码时间、位线充放电时间和输出缓冲器延时。其中缓冲器延时主要由电路保护和驱动的要求决定;为使ROM面积尽量小,ROM单元总是取最小尺寸,所以位线充放电时间主要由位线负载决定;由于译码方案不同,而且字线较长、负载大,所以这部分的设计对整个ROM的速度影响较大。本文主要从选择合适的译码方案和减少字线上的RC负载两个方面来优化设计,从而提高字线响应速度。

3.1 地址探测

本设计采用静态逻辑电路结构,无外部时钟控制,由地址码的变动探测电路产生一定宽度的脉冲信号,作为选择性预充电模块的输入信号、字线启动的控制信号和灵敏放大器模块的使能控制信号。脉冲信号的宽度须满足所选中的存储器阵列模块预充电所需的足够时间,同时在预充电结束后控制字线信号的启动和灵敏放大器的使能,在降低动态功耗的前提下正确地完成存储数据的读取操作。地址探测模块主要由延时单元和异或逻辑单元组成。

3.2 三级译码结构

为减小字线位线延时、降低译码器功耗,译码器模块采用三级译码结构:块选择、字线选择和位线选择。对应于前面提到的存储阵列分体分块处理,地址A15~A11译出32根块选择线,A10~A4译出128根字线,A3~A0译出16根位线。译码模块由CMOS静态逻辑门实现,译出的数据通过灵敏放大器后经过驱动电路输出,送到内部数据总线。

最初的译码设计是32块阵列的block线、word线和bit线整体译码,这样在版图布局中就出现几十根长的互连线并列走线,对速度的影响很大。因此根据实际版图布局对逻辑进行相应调整,把32块阵列分成四大组,每组八块,四大组独立译码,这样大大减少了长的并列互连线的根数,同时也减少了布线面积。

3.3 减少字线负载

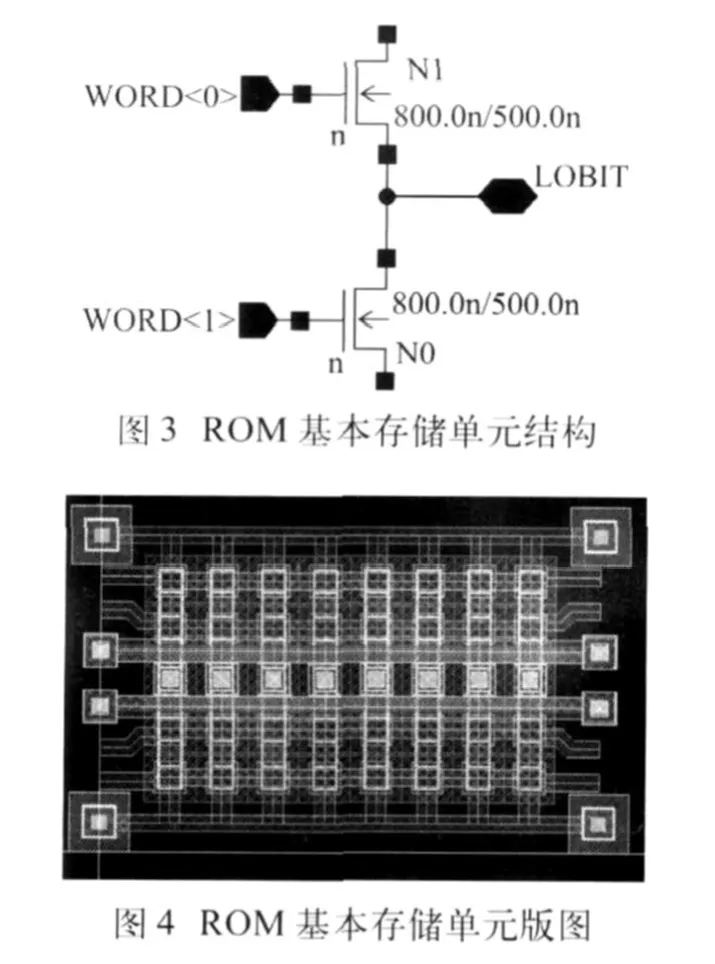

上述设计没有考虑存在的寄生电阻、电容,而这些会对电路性能产生较大影响,特别是对ROM中的较长字线且负载重的。考虑到电路对速度的要求,在ROM基本存储单元设计中,两个N管共漏,减小位电容,见图3;版图设计时在栅上覆盖三铝,减小电阻,见图4。

3.4 总线输出

大容量的MaskROM其存储阵列规模大,而数据输出位宽有限,则必须共用输出。本设计运用基于三态门的数据输出总线结构,分为两级:第一级数据总线为“16-9”(单个18k子存储体中的16位线共选9位输出),第二级数据总线为“32-1”(32个18k子存储体选1个输出),可有效减小输出模块的电路规模和输出延时。

4 实现

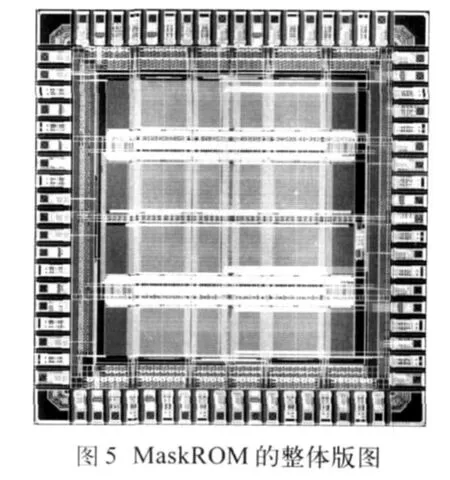

根据预先确定的方案,首先是进行逻辑设计与仿真,消化已有的高速ROM、SRAM设计资料,关键模块采用Hspice仿真,整体电路采用Hsim仿真;然后是进行内核的版图设计,由于对速度和精度都有很高要求,因此版图严格按照电路图器件要求设计,对模拟电路还重点考虑了镜像源的对称性和一致性;尽量减小互连线电容,整体布局时避免长的互连线和多根长的互连线并列走线,并在面积允许的情况下将其宽度尽量加宽,线间距尽量加大。内核部分设计完成后,用Abstract抽取lef文件,在SE中进行整体的布局布线,调入高速PAD,完成整个电路的版图设计;最后是版图提取与验证,整体电路用LPE提取SPICE网表,使用Hsim进行带有电容参数的晶体管级后仿真,在Dracula环境下进行DRC、ERC和LVS检查。整个MaskROM的版图如图5所示,面积为5.4 mm×5.7mm。

采用CSMC 0.5μm CMOS工艺实现并流片,在Teradyne J 750 测试系统上完成了芯片测试,测试结果表明,在地址变化频率f= 20MHz、电源电压VDD= 4.5V~5.5V、温度-55℃≤TA≤ 125℃的条件下,芯片功能及电参数均正常,读取时间约为12ns,单位功耗约为1.06 mW/MHz,达到了设计要求。

5 结束语

本文讨论了掩模只读存储器中各个功能模块电路的原理与设计,运用分体分块结构、三级译码、两级输出总线等技术,设计了一种32×18k bit的MaskROM,完成了“高速、低功耗”的设计目标。

[1]Rabaey Jan M, et al. 数字集成电路:设计透视(第二版)[M]. 北京:清华大学出版社,2004,3.

[2]Wei Cui. Design of Small Area and Low Power ConsumptionMask ROM[J]. ICICDT07 IEEE, 2007.

[3]郭敬松,等. 嵌入式系统中ROM的设计[J]. 微电子学与计算机,2003,1.

[4]张亚灵,等. 一种基于CMOS工艺的掩模ROM设计[J].西安邮电学院学报,2009,14(1).

Research and Design of a High Speed Mask ROM

XU Rui, MAO Guo-jun

(China Electronic Technlogy Group Corporation No.58Research Institute, Wuxi214035,China)

This paper analyses the structure and principle of the MaskRom, and then expatiates the design of a 576k bits MaskRom. This design concentrates on the optimization of decoding part by the means of improving the decoding scheme and reducing wordline RC load, which resulting in advantages in timing, area and power.Applying 0.5μm CMOS process, the MaskRom’s unit dissipation is 1.06 mW/MHz, with 5V supply voltage and about 12ns access time(80MHz speed).

maskROM; CMOS; decoding; wordline; speed

TN706

A

1681-1070(2011)02-0012-03

2010-11-26

徐 睿(1973-),女,山东胶南人,高级工程师,现在中国电子科技集团公司第五十八研究所从事集成电路设计工作;

冒国均(1980-),男,江苏如皋人,工程师,现在中国电子科技集团公司第五十八研究所从事集成电路市场营销工作。

微电子制造与可靠性