数字锁相环在电机控制系统中的应用*

2010-11-21赵创社史志富

韩 瑞,赵创社,史志富

(西安应用光学研究所,陕西西安 710065)

0 引言

锁相环路(Phase-Locked Loop,PLL)是一个能够跟踪输入信号相位的闭环自动控制系统,具有窄带跟踪性能、输入输出信号之间不存在频率差而只有很小的稳态相位差,具有很强的抗干扰性、抑制噪声性和同步跟踪性能,因而在通信、雷达、航天、航海、计算机、电动机控制等领域获得了广泛应用,逐渐成为电子设备中常用的一种基本部件。随着大规模、超高速数字集成电路的发展及计算机的普遍应用,出现了全数字化PLL,即环路部件全部数字化,采用数字鉴相器(Digital Phase Detector,DPD)、数字环路滤波器(Digital Low Filter,DLF)、数控振荡器(Digital Controlled Oscillator,DCO)构成PLL。数字化锁相环的电路完全数字化,受外界干扰小,系统可靠性大大提高。整个环路都可以直接用微处理机来模拟实现。

使用锁相环进行电机[1]的速度反馈控制,具有控制精度高、转速稳定、锁定时间短等优点,本文就使用数字锁相环构成速度反馈环节进行速度控制。通过VHDL语言编写程序构成锁相环,用锁相方式进行电机控制系统速度回路的反馈控制。

1 数字锁相环的原理

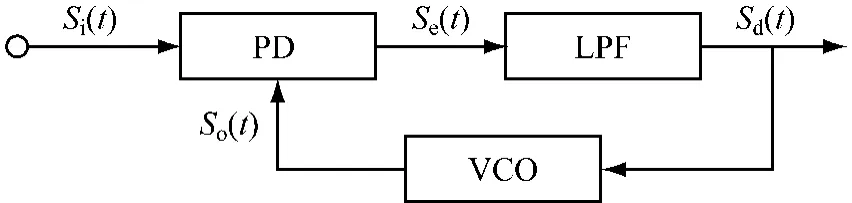

锁相环最基本的结构如图1所示。它由鉴相器(Phase Detector,PD)、环路滤波器(Low Pass Filter,LPF)和压控振荡器(Voltage Controlled Oscillator,VCO)三个基本部件组成。PD是相位比较装置,将输入信号Si(t)和VCO输出信号So(t)的相位进行比较,产生对应于两个信号相位差的误差电压Se(t)。LPF的作用是滤除误差电压Se(t)中的高频成分和噪声,以保证环路所要求的性能,增加系统的稳定性。VCO受控制电压Sd(t)的控制,使VCO的频率向输入信号的频率靠拢,直至消除频差而锁定[2]。

图1 锁相环的基本结构

瞬时频率和瞬时相位的关系如下:

式中:θ0——初始相位。

加到PD的两个振荡信号的频率差为

式中:ωR——输入信号频率;

ωV——反馈信号频率。

此时的瞬时相位差为

当 ωR=ωV时,有 Δω(t)≈0,于是:

由此可知,当两个振荡器频率相等时,他们的瞬时相位差是一个常数。

同样的道理,如果 θe(t)=θ0,则:

也就得到了ωR=ωV,证明了当两个振荡信号的瞬时相位差为一常数时二者的频率必然相等[3]。

在闭环条件下,如果由于某种原因使VCO的角频率发生变化,则会引起两个信号间的相位差不再是恒定值,PD的输出电压也就跟着发生相应变化。该变化的电压使VCO的频率不断改变,直到ωR=ωV为止,这就是PLL的基本原理。

一般数字PLL的组成与模拟PLL相同,即由相位检波器、LPF和VCO等基本部件构成,但这些部件全部采用数字电路。输入信号被采样并与环路输出的本地估算信号作相位比较,产生一个与两者相位误差成比例的数字样本序列。这个代表相位误差大小和极性的数字样本序列由数字LPF加以平滑得到控制信号去控制DCO的周期(频率或相位)。只要环路设计正确,经过反复的反馈调节控制,将使输出本地估算信号的相位逼近输入信号的相位,最终使环路锁定。

2 锁相环控制系统控制策略和硬件组成

2.1 控制系统的控制策略

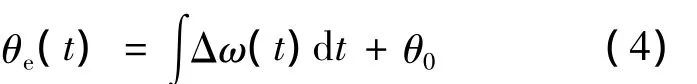

电机控制系统采用转速、电流双闭环控制[4],采用PID控制方式构成系统的速度和电流控制器。复杂可编程逻辑控制器(Complex Programmable Logic Device,CPLD)完成两部分功能:一部分构成数字锁相环[5],检测输入频率与反馈频率的误差值,进行速度反馈控制;另一部分采集电枢反电势产生电机逆变器的换相控制信号。

系统采用锁相环进行速度反馈控制,锁相环的控制方式为将反馈频率(电机转动频率)与输入系统的基准频率进行比较,如果反馈信号频率低于基准频率,说明电机转速偏低,增加经过分频后的本地高速时钟的占空比,增大锁相环输出信号的直流分量,电机转速上升;如果反馈信号频率高于基准频率,说明电机转速偏高,减小锁相环输出周期信号的占空比,则电机转速下降。其中,计数器的模值K对锁相环的速度锁定起关键作用。环路滤波器(计数器)在环路中对输入噪声起抑制作用,而且对环路的校正速度起调节作用。计数器的模数K越小,系统响应越快,捕捉时间越短;模数K越大,系统响应越慢,捕捉时间越长。

采用数字锁相环的系统控制原理框图如图2所示。

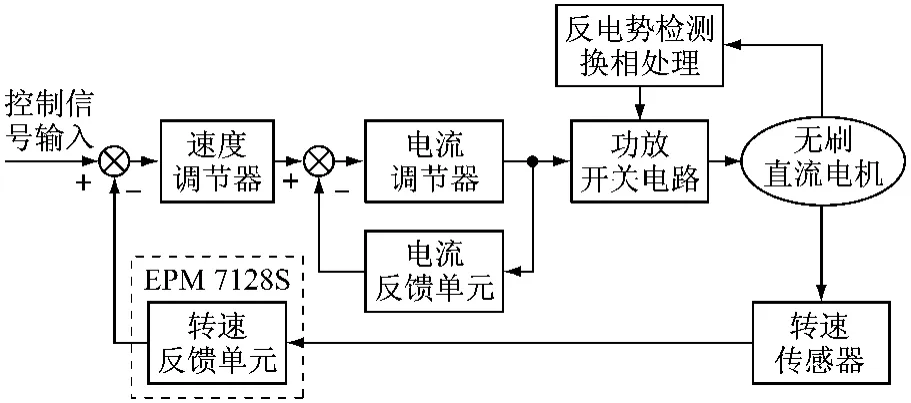

2.2 控制系统的硬件组成

无刷直流电机控制系统的硬件连接框图如图3所示,主要由无刷直流电机、逆变器、控制器和电源等组成。

图2 系统的控制框图

由于电机的转速较高,达到19 500 r/min,采用运行速度快的CPLD进行速度反馈和电机换相信号的处理。电机的速度反馈量经VHDL语言编写的数字锁相环处理,产生偏差量进入速度控制器进行速度校正。EPM7128S CPLD接收电机绕组的反电势[6],产生控制4组功放开关导通的信号。控制电机依次以一定的顺序转动。

图3 控制系统硬件连接框图

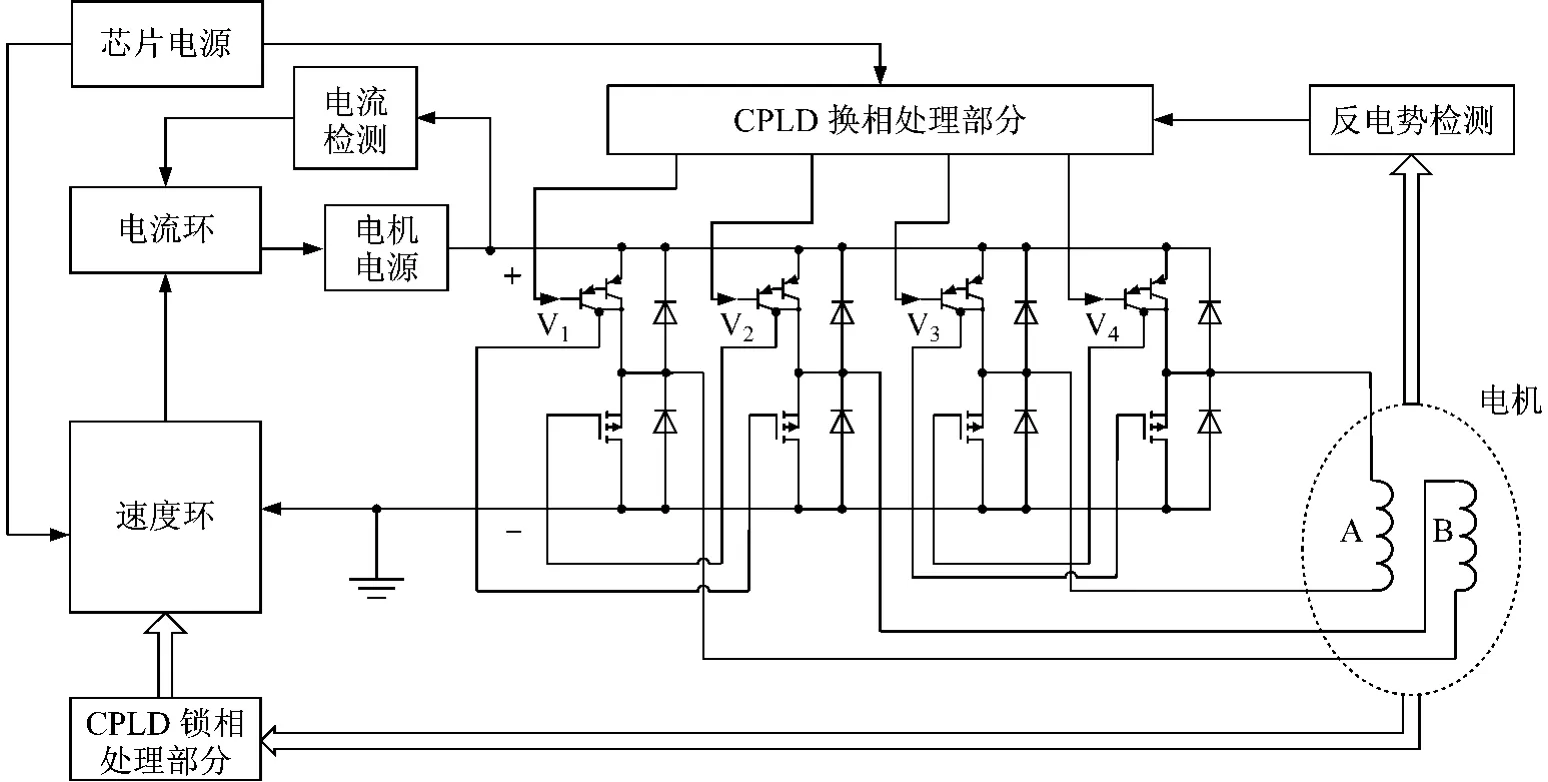

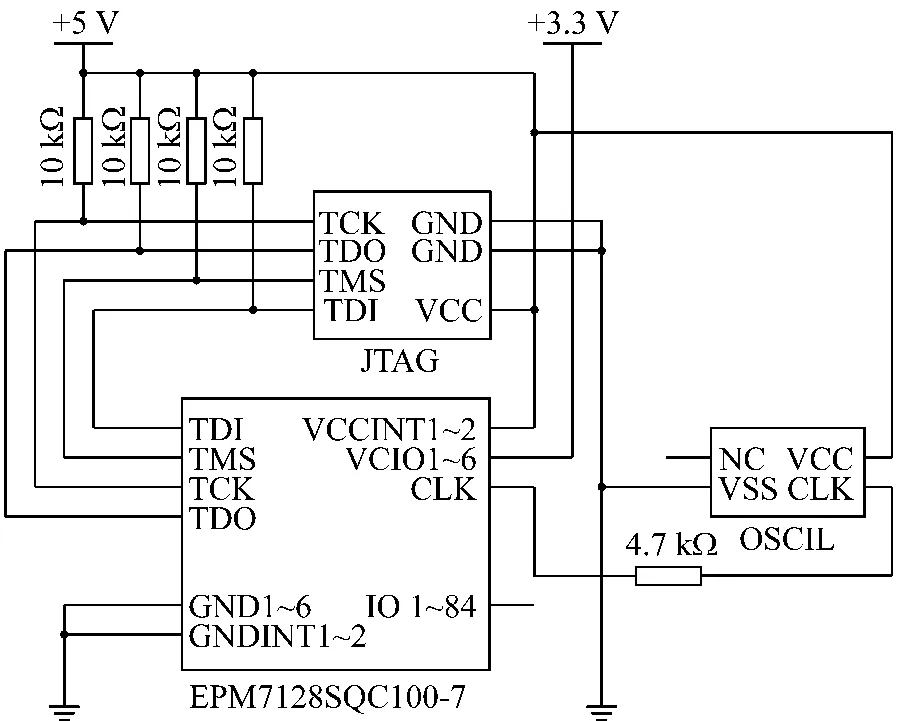

系统的CPLD控制部分的硬件电路连接如图4所示。

图4 CPLD电路连接图

3 软件设计

CPLD部分完成电机的换相处理和速度反馈控制等功能,采用图形化设计和VHDL语言混合设计完成时序部分的编写。CPLD接收电机绕组反电势,经片内逻辑电路处理,形成4路逆变器的导通控制信号,用以控制电机绕组的加电顺序;通过CPLD内置的数字锁相环74LS297进行锁相处理,完成对电机转速的恒定控制。利用CPLD将锁相环和换相处理电路封装在一起,形成一个完整的速度反馈控制模块。

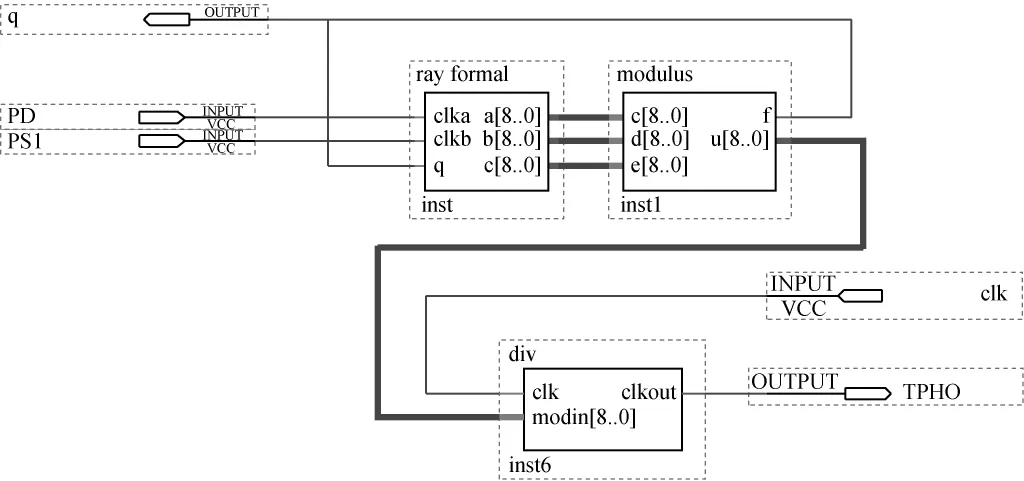

锁相环控制部分在QuatrusII[7]开发环境中用VHDL[8]语言编写,由以下三个模块构成。

(1)PD模块:对输入的电机转速信号进行计数,并与给定的参考转速进行比较,如果电机转速低于参考值,则输出滞后脉冲;转速高于参考值,则输出超前脉冲。

(2)LPF模块:超前和滞后脉冲分别送入各自的计数器里进行计数。超前计数器记满时,输出超前控制脉冲,控制分频器的分频系数;滞后计数器记满时,输出滞后控制脉冲,增大分频器的分频系数。

(3)相位控制器模块:对基准频率进行分频,接收到超前脉冲时,减小分频系数;接收到滞后脉冲时,增大分频系数。

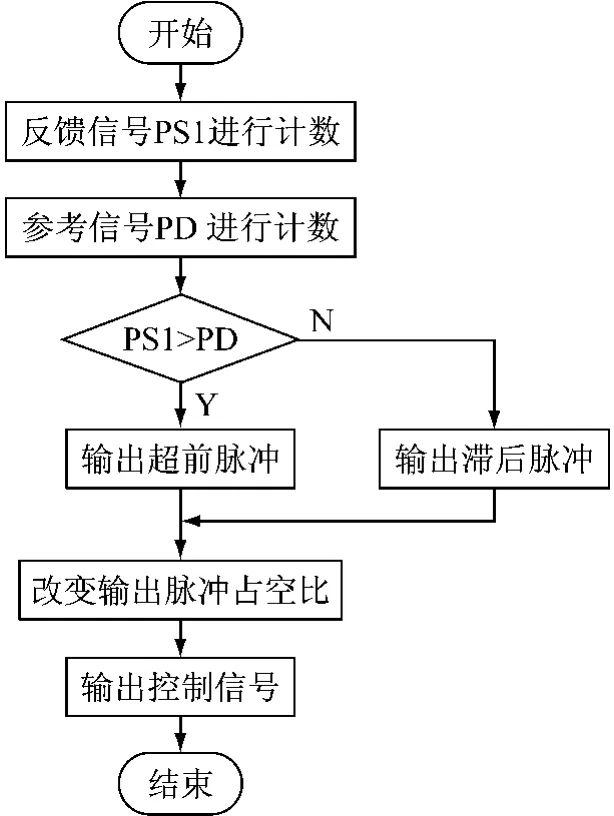

CPLD部分程序流程图如图5所示。

锁相环的控制模块框图如图6所示。

4 控制系统仿真及其试验结果比较分析

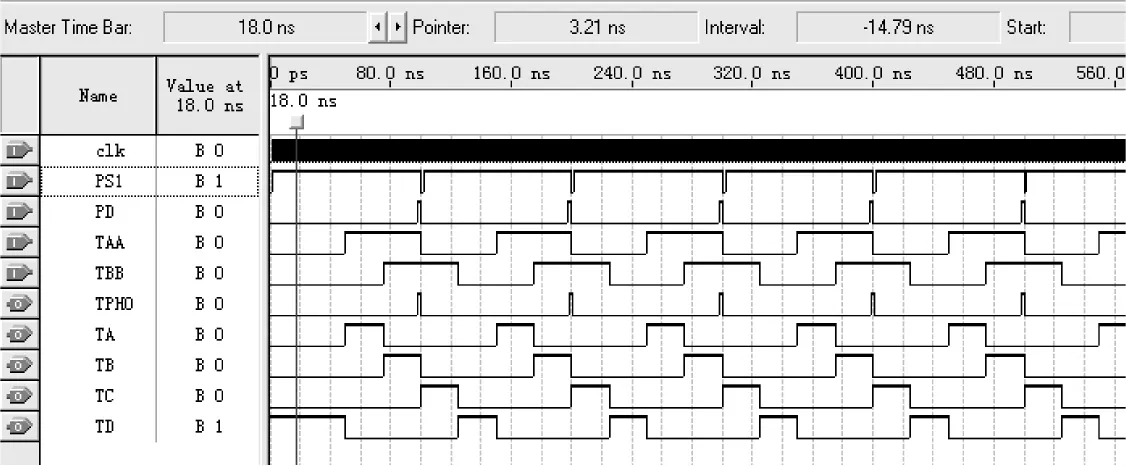

在进行了VHDL描述和编译后,就可应用EDA软件进行时序功能仿真。功能仿真是在QuartusⅡ软件开发环境下进行的,时序仿真波形如图7所示。

图5 数字锁相环程序流程图

图6 数字锁相环控制模块

图7 CPLD时序仿真图

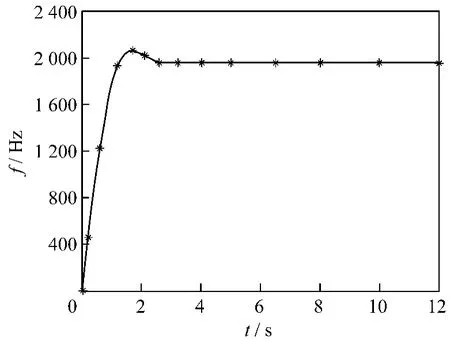

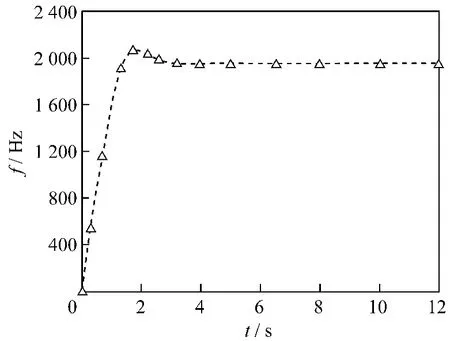

记录下行扫电机的峰值时间、稳定时间、最高转速和锁相环路的抖动值,由峰值时间、稳定时间、最高转速等指标,绘制出数字化模拟控制系统的电机转速响应曲线[9],分别如图8、9所示。

图8 数字化电机转速响应曲线

图9 模拟系统电机转速曲线

从图8可以看出,当给定加速信号后,电机在加速后1.6 s达到了速度峰值,在约3 s时达到了稳定转速,经过一次振荡后进入稳态,调节时间ts为2.8 s。

由图9可看出:行扫系统在加速后1.8 s达到速度峰值,调节时间ts为3.2 s。

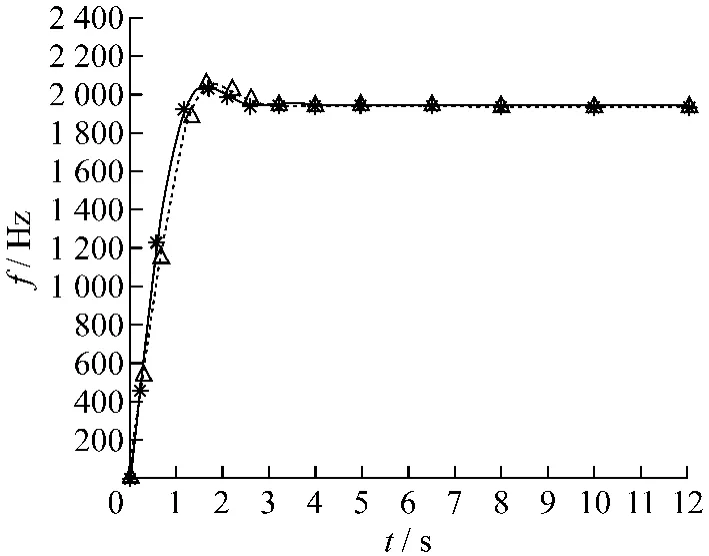

两曲线的叠加波形如图10所示。

从图10可以看出,数字化电机控制系统的调节时间小于模拟控制系统的调节时间,系统可以更快地达到稳定转速;数字系统最高转速小于模拟控制系统,即超调量小。

5 结语

图10 数字化与模拟系统的转速曲线对比

在分析数字锁相环原理的基础上,提出了基于EPM7128S构成数字锁相环的电机控制系统解决方案,充分利用CPLD的强大功能,使系统获得较高的控制精度和动、静态特性。将锁相速度控制方式应用于无刷直流电机系统,将模拟和数字系统的结果加以比较和分析,证明该系统具有较强的鲁棒性和自适应能力,实现了对电机输出转矩和转速的控制,改善了电机的调速性能。

[1]王益全.电动机原理与实用技术[M].北京:科学出版社,2005.

[2]张厥盛,郑继禹,万心平.锁相技术[M].西安:西安电子科技大学出版社,1994.

[3]徐丽娜.数字控制——建模与分析、设计与实现[M].北京:科学出版社,2006.

[4]张璟玥,纪明,王惠林.机载稳瞄控制系统模型及仿真分析[J].应用光学,2006,27(6):491-496.

[5]耿计芳.高精度自动变模控制全数字锁相环的研究[D].天津:天津大学,2006.

[6]林明耀,王永,李海文,等.反电势法无位置传感器无刷直流电机最佳换相逻辑分析[J].中小型电机,2003,30(5):14-16.

[7]周润景,图雅,张丽敏.基于QuatrusⅡ的FPGA/CPLD数字系统设计实例[M].北京:电子工业出版社,2007.

[8]雷伏容.VHDL电路设计[M].北京:清华大学出版社,2006.

[9]张静.MATLAB在控制系统中的应用[M].北京:电子工业出版社,2007.