OFDM系统中低存储可配置的(I)FFT的设计与实现

2010-11-04余厚全龚光勇朱嵘涛

陈 超 余厚全 龚光勇 朱嵘涛

(中石油川庆测井公司 重庆)

OFDM系统中低存储可配置的(I)FFT的设计与实现

陈 超 余厚全 龚光勇 朱嵘涛

(中石油川庆测井公司 重庆)

文章提出了一种OFDM系统中高速、可配置、低存储的(I)FFT处理器设计方法。该方法采用了按频率抽取的基4流水线结构实现高速运算,利用单个原位同址运算RAM及CORDIC算法实现低存储运算,通过改变流水线的级数实现多种点数的(I)FFT运算。整个设计通过FPGA实现。在外部时钟为100 MHz时,处理器计算一次4096点、13位长数据FFT的时间约为103μs,所消耗的存储器仅为106 Kb。

快速傅立叶变换;正交频分复用;坐标旋转数字计算机;基4算法;现场可编程门阵列

0 引 言

随着成像测井等测井新技术的发展,测井过程中需要实时上传的数据量越来越大。受限于测井电缆恶劣的传输环境,传统的测井电缆数据传输系统的传输速率一般只有100 kb/s,极大的限制了整个成像测井系统的性能。OFDM(正交频分复用)是一种多载波调制技术,由于其具有高效的频谱利用率、抗窄带干扰及对抗频率选择性衰落等能力,已被广泛应用于各种宽带通信系统中。根据测井电缆的传输特性,将OFDM技术应用到测井电缆数传系统中将有望大大提高测井电缆数据传输的速度。OFDM系统中最核心的部分无疑是负责调制解调的(I)FFT/FFT运算。其(I)FFT的变换点数都是多种可配置的,对FFT处理器的数据吞吐量和数据处理的实时性也有着很高的要求。为满足这些需求,本文设计了一种高速、位长及点数可配置、低存储的(I)FFT处理器。该处理器采用了乒乓流水线结构来满足高速、大吞吐量数据处理要求,单个原位同址运算RAM及CORDIC算法实现低存储运算,通过改变流水线的级数来实现多种点数的(I)FFT变换。

1 算法选择

1.1 FFT算法选择

从FFT算法的复杂性来看,基4算法比基2算法减少约20%的运算量。从硬件实现的难易程度来看,基4算法具有比分裂基和更高基较易控制的特点。

FFT算法有按时间抽取DIT和按频率抽取DIF两种形式,其区别在于输入数据和旋转因子乘、加的顺序不同。在DIT中,蝶形运算的输入数据和旋转因子是先乘后加,而在DIF中,则是先加后乘,两者并没有实质区别。本设计采用的是DIF的基4 FFT的算法。

1.2 CORDIC算法

一个基4蝶形运算单元需要8个复加和3个复乘,也就是12个实数乘法和22个实数加法,若直接用乘法器实现需要消耗大量的硬件资源,还需要专门用一块ROM存放旋转因子的实部和虚部。所以本文采用CORDIC算法来实现蝶算单元的乘法。

2 (I)FFT/FFT处理器的设计和实现

参数化(I)FFT处理器的结构如图1所示,首先给定位长的4M点数据串行输入到RAM中经过第一级(共M级)基4蝶形运算处理后,得到的数据经过“溢出检测控制模块”处理,再写入到双口RAM中,经过第二级基4(I)FFT运算处理。重复上述操作,直到第后,数据经过“4M级点(I)FFT/FFT”后直接混序输出,之后输出整序和循环前缀插入共用一个模块,这样做不仅节省了一级存储器,而且在下一次(I)FFT开始前,不必等待上一次(I)FFT的输出、整序及循环前缀插入,从而大大提高了处理器的速度。各个功能模块的设计和实现如下:

图1 图1 OFDM系统中参数化(I)FFT整体实现框图

2.1 控制信号与地址产生模块

控制信号与地址产生模块是整个系统的核心,也是最复杂的部分。它负责控制系统运行过程中的各个启动信号的产生,及对高速数据存储交换单元RAM的操作,选择何时该写入何处的数据,同时产生各级流水线中RAM的读写地址。其工作流程可以简述如下:在(I)FFT启动信号发出后,判断(I)FFT的选择信号(如0为fft,1为ifft),由此决定是对输入数据何种变换。确定所作变换后,开始读入输入的数据。RAM在第一级的时候,写入的数据就是输入样本,在后面的各级中,写入RAM的数据是经过蝶型运算后的中间数据。此时地址产生模块会按照蝶型运算信号流图上各中间数据点的位置产生RAM的读写地址。到最后一级蝶算完成后,控制数据不必经过CORDIC模块,直接输出,即为数据经过(I)FFT变换后的结果,此时由模块产生一个输出有效信号。,模块还会产生一个系统工作状态指示信号,以确定下一次(I)FFT运算何时开始。

2.2 双口RAM

RAM是存储输入数据及中间运算结果的单元。蝶型运算的输入、输出数据都要经过RAM的读写操作,因此RAM的读写速度直接影响(I)FFT处理器的速度。为了提高系统的整体速度,在尽量节约硬件资源的前提下,本设计采用了Altera提供的参数化功能模块LPM实现的双口RAM,实部和虚部数据各一个双口RAM。这样可以对一块RAM同时进行读写操作,大大提高了数据吞吐量及这个系统的效率。

2.3 四点FFT模块

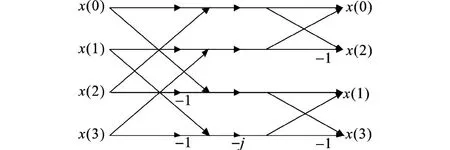

图2所示是基4蝶算的信号流图,四点FFT模块中完全不需要复数乘法。乘-j只需将实部虚部交换,再加上相应的正负号即可。四点FFT模块采用的是流水线结构,每次蝶算需要四个周期才能完成。四点(I)FFT与四点FFT共用一个模块,只需将图2中的-j变为j即可,其中原理将在后面讲述。

图2 基4蝶算单元信号流图

2.4 CORDIC模块

CORDIC算法的原理在前面已有说明,其硬件实现如图3所示,本设计采用的是流水线结构。该结构能够在执行过程中同时输入数据,从而极大的提高了模块的运行效率。在该结构中,每一个移位都是固定的深度,且旋转因子的各个值作为常数直接连到累加器上,不需要存储空间和读取时间。整个CORDIC简化为加减法的直接相连,硬件实现非常的简单方便。

图3 CORDIC硬件实现结构图

当需要旋转的角度在(0,π/2)范围之外时,只需简单的互换、取反操作就可以将其调整到(0,π/2)范围之内,代价比直接作旋转要低。不同角度范围的预旋转对应关系见表1。

表1 角度预旋转关系对应表

2.5 溢出检测和控制模块

在一个基4蝶形运算单元中,由于旋转因子的实部和虚部的绝对值总是不大于1,故乘法运算不会引起输出数据位数的增加,而输入数据的加减也最多只有两次进位。因此,若输入数据的实部、虚部分别为N位字长,为防止溢出,输出数据要用N+2位字长表示。溢出检测可采用状态机的描述形式对输出数据的高3位进行比较,得到溢出控制位,以决定下一级作何种移位处理,移位输出的N位字长的数据作为下一级蝶形运算的输入。同时,对各级的溢出控制位进行求和运算,得到一次N点FFT处理结果的块浮点指数。

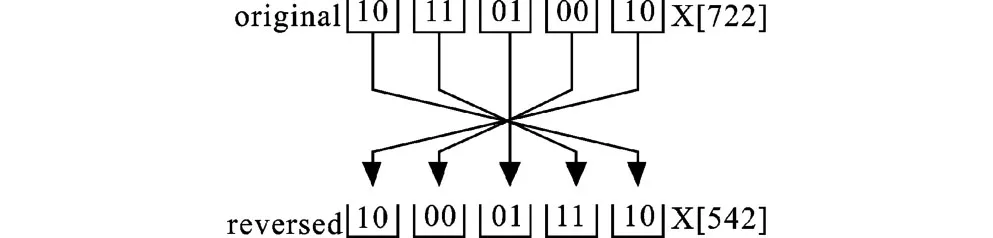

2.6 输出整序

本设计中,数据经过第M级流水线处理后,直接混序输出,不用再输入到RAM中,之后输出整序和循环前缀插入共用一个模块,这样做不仅节省了一级存储器,而且在下一次(I)FFT开始前,不必等待上一次(I)FFT的输出、整序及循环前缀插入,从而大大提高了处理器的速度。基4FFT算法的整序如图4所示。

图4 基4FFT整序规律图

2.7 用FFT实现(I)FFT

利用FFT模块求序列的IFFT在硬件实现中通常有两种方法:一是对输入序列取共轭,在输出端同样对数据取共轭,得到的序列除以点数N就是输入序列的(I)FFT变换结果。另一种是直接按照IDFT的公式(式1)直接求得x(n)。两种方法实现起来都比较简单。本设计采用的是后一种方法,具体做法就是产生与FFT运算相反的旋转因子,输出数据除以点数N即可。

3 结果分析

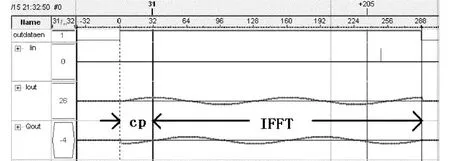

在QuartusII平台上,选用Altera公司的CycloneII系列EP2C35F672C6器件进行综合、布局布线和时序分析。在外部时钟为100 MHz的情况下,一次13位、4096点数据FFT处理所需时间是103μs,所消耗的资源如下:存储器106 Kb,逻辑单元1 880个,其中寄存器单元1 295个。图5是用Altera提供的SignalTapII逻辑分析仪得到的硬件测试结果,图中Iin是加载到子载波上的单个脉冲,经过256点(I)FFT变换、整序,加循环前缀后,得到数据Iout、Qout。图中0~31是循环前缀(CP),32~287是256点IFFT的变换结果,由(I)FFT的性质可知:单个脉冲组成的实序列(Iin)经过IFFT变换后所得到的序列(Iout&Qout),其实部(Iout)是余弦信号,虚部(Qout)是正弦信号。两者频率、幅度相同,相位相差90°。

图5 单个脉冲加载到子载波后(I)FFT加循环前缀

4 结 论

本文设计了一种高速、低存储、位长及点数可配置的(I)FFT处理器。该处理器可被用于测井数传及

WLAN、WiMAX、LTE、DVB等现代通信系统中。在时钟为100MHz时,处理器计算一次4096点的FFT所需时间稍大于Altera提供的IP Core,但所消耗的存储资源仅为IP Core的四分之一。

[1] UweMeyer.Baese.数字信号处理的FPGA实现(第二版)[M].北京:清华大学出版社,2006

[2] 胡广书.数字信号处理—理论、算法与实现(第二版)[M].北京:清华大学出版社,2003

[3] 尹长川,罗 涛,乐光新.多载波宽带无线通信技术[M].北京:北京邮电大学出版社,2004

[4] F.Kristensen,P.Neilson and A.Olssen.Reduced transceiver-delay for OFDM systems[M].IEEE Vehicular Technology Conference,VTC,Spring 2004

[5] Y.-T.Lin,P.-Y.Tsai and T.-D.Chiueh.Low-power varibable-length fast Fourier transform processor[J].IEE Proc.-Comput.Digit.Tech,2005,152(4)

[6] Son.B.S,Sunwoo.M.H,Y ong Serk Kim.A high-speed FFT processor for OFDMsystems[J].Circuits and Systems,2002.ISCAS 2002.IEEE International Symposiumon Volume 3,2002,3

PI,2010,24(6):74~76

This paper proposes a high speed,reduced-memory and reconfigurable(I)FFT processor for OFDM systems.the processor uses radix-4 DIF pipeline architecture for high speed computation.In order to meet the low memory requirement,single in-place memory and CORDIC algorithm are adopted.Implemented on a FPGA device,the processor can calculate a 4096-point complex FFT in 103us when operates at 100MHz,while just consumes 106K B memory.

Key words:FFT;OFDM;CORDIC;Radix-4 algorithm;FPGA

educed-Memo-ry and reconfigurable(I)FFT processor for OFDM system.

Chen Chao,Yu Houquan,Gong Guangyong and Zhu Rongtao.

P681.8+3

B

1004-9134(2010)06-0074-03

陈 超,男,1985年生,长江大学工程技术学院信息系硕士研究生,主要研究方向为软件无线电。邮编:434023

2010-07-09编辑:刘雅铭)