一种远程配置FPGA的设计方法

2010-10-27张学森李宏中国电子科技集团公司第38研究所230031

张学森 李宏 中国电子科技集团公司第38研究所 230031

一种远程配置FPGA的设计方法

张学森 李宏 中国电子科技集团公司第38研究所 230031

远程配置FPGA是通过对FPGA配置芯片的读写实现对FPGA设计的更新。本文主要介绍了一种基于片上可编程系统(SOPC)技术,通过以太网实现对现场可编程逻辑器件进行远程更新配置文件的设计方法。

FPGA;片上可编程系统;远程配置

FPGA; system on a programmable chip(SOPC);remote configuration

1、引言

随着FPGA广泛的应用于很多领域,在有些领域要求系统具有远程更新设计的功能,而对FPGA设计的升级必须更新FPGA的配置文件才能完成,目前很多方案都是基于CPU+CPLD+FLASH方案,其原理是通过CPU获得远程加载数据写入FLASH存储器,CPLD电路从FLASH读取配置数据产生相应的时序对FPGA进行配置。本文主要介绍在Altera公司的FPGA里运用SOPC设计手段,嵌入Nios II软核处理器技术,通过对FPGA配置芯片EPCS器件的读写实现对FPGA设计的更新。

2、SOPC技术及FPGA常用配置方法简介

SOPC(System on a Programmable Chip:片上可编程系统)是Altera公司提出来的一种灵活、高效的片上系统(S O C)解决方案,它将处理器、存储器、I/O口等系统设计需要的功能模块集成到一个可编程器件上,构建成一个可编程的片上系统,根据系统实际需求可裁减、可扩充、可升级,并具备软硬件编程的功能。Nios II 是Altera 公司为SOPC设计提供的软核处理器,它具有32位处理器的基本结构单元—32位指令大小,32 位数据和地址总线,32 位通用寄存器和32个外部中断源,其处理速度可达到200DMIPS,Nios II 软核发展至今主要以下几大特点:1)在一片FPGA器件里可配置多个软核处理器;2)支持操作系统的移植;3)支持硬件加速;4)支持用户接口的开发。

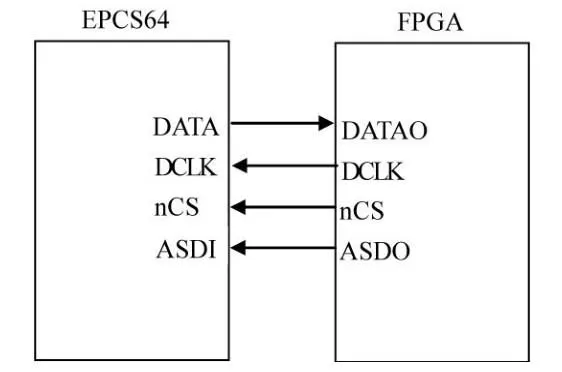

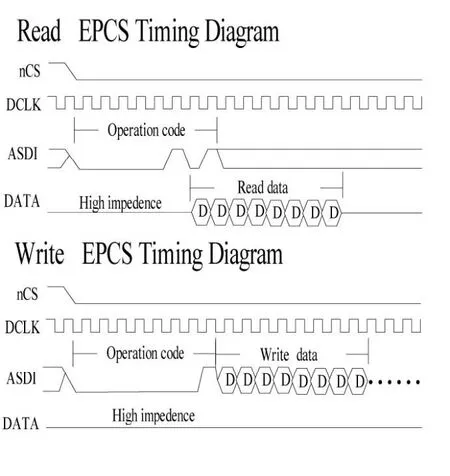

FPGA的配置器芯片常用的有两大类:一类配置芯片是主动的,其代表是EPC16系列, 这类器件可以主动产生F P G A配置时需要的时序,把其内部FLASH存储的文件加载到FPGA;另一类是配置芯片是被动的,其代表是EPCS系列,FPGA需要主动产生相应的时序去读写这类芯片内的FLASH。本文介绍配置系统中选用的EPCS系列的EPCS64,其配置连接关系如图1, EPCS64是串行被动配置芯片,内部有64Mbits数据存储空间。配置系统的读写时序关序如图2。

图1 串行配置芯片与FPGA接法

图2 EPCS读写时序图

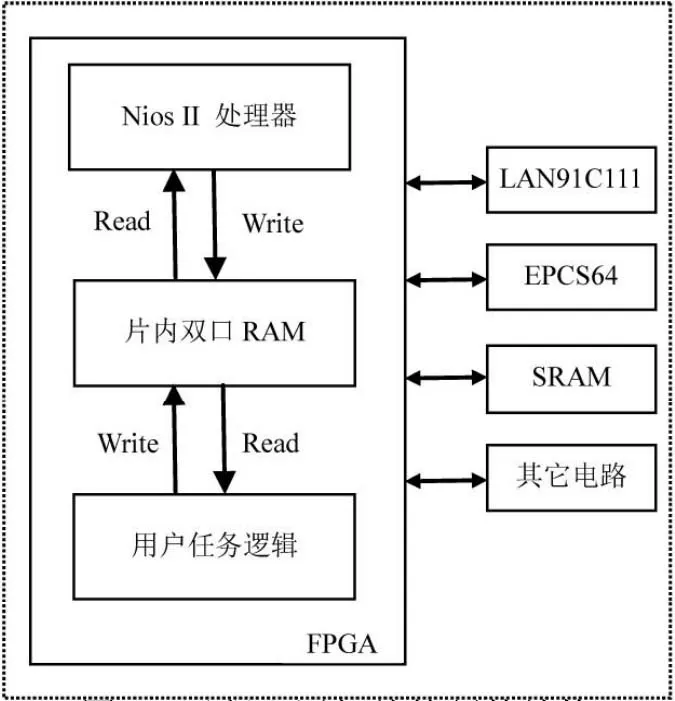

图3 远程配置相关的硬件结构

3、远程配置的硬件架构

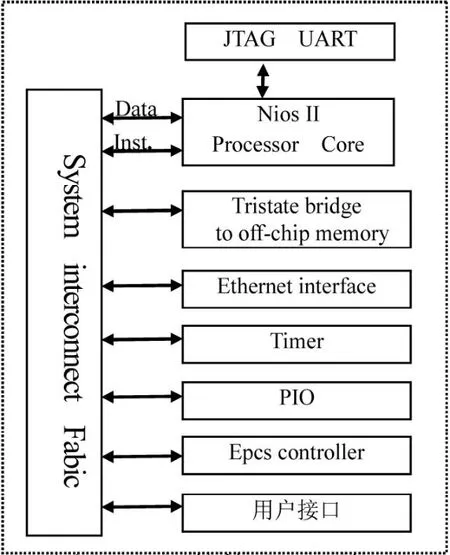

在某系统中,其远程加载功能部分涉及到的硬件结构如图3,图3中FPGA选用的是EP2S30系列,其内部大部分逻辑是用来完成用户任务,另外一部分是Nios II处理器及其相关外围接口电路控制;以太网接口芯片选用了SMSC 公司推出的LAN91C111 芯片,该芯片内部集成了以太网介质访问(MAC) 及物理层收发器(PHY) ,支持10M/100M 全双工传输模式、自动协商等功能;EPCS64芯片用来存储FPGA配置文件、Nios II运行程序以及用户数据;SRAM是Nios II 程序运行的空间;FPGA内部的双口RAM是用户任务逻辑与Nios II 之间交换数据的空间。软核处理器Nios II配置的相关资源如图4。整个系统配置启动过程如下:FPGA上电启动时,主动从EPCS器件里读取其自身加载文件,读写完毕后,FPGA开始正常工作,FPGA内嵌入的Nios II 处理器的EPCS controller从EPCS相应存储空间里搬移程序运行文件至Nioss II程序运行空间SRAM,搬移完后,Nios II开始正常工作。

图4 配置软核处理器资源

4、远程配置的软件设计

在某系统中,Nios II处理器里嵌入了uC/os II操作系统,嵌入式操作系统uC/os II是基于任务优先级的多任务的微内核RTOS,其源代码公开,可移植性好,可裁减。Altera公司已在其Nios II开发环境里嵌入了uC/os II操作系统,设计者仅根据需要去选择。所以该系统中Nios II需处理的任务都是在uC/os II操作系统架构下完成的,本节仅介绍远程配置任务的软件设计。

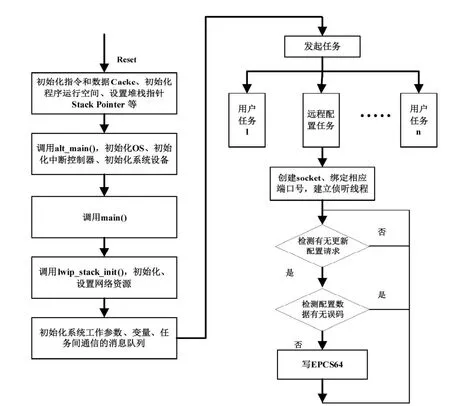

对于NiosII处理器来说完成对FPGA配置的任务主要需要解决两个问题:一个是获得远程配置更新的数据,一个是将配置数据写入配置芯片。在此我们利用网络技术获取远程配置数据,在uC/os II操作系统采用轻量级网络协议LWIP(Light weight IP,LWIP), LWIP是一种专门针对嵌入式系统应用而设计的网络通信协议,由于LWIP 实现的关键在于削减代码大小和内存消耗,在网络协议栈初始化后,使用标准套接字API 创建新任务访问网络协议栈就可以实现网络通信了。对于配置芯片读写是通过EPCS_contrller接口去控制的,该接口根据Nios II处理器发出的指令,产生类似图2所表述的时序。其软件具体流程如图5。

5、结论

本文论述了远程配置FPGA的设计方法,该设计方法基于SOPC 和嵌入式系统技术,实现了远程更新FPGA的配置文件及Nios II的运行软件,完善了SOPC设计。整个系统仅集中在一片FPGA里完成,系统安全可靠,应前景广阔。

图5 远程配置软件设流程

[1] Altera Company. Nios II Processor Reference Handbook [ Z] .2009

[2] Altera Company. Nios II Software Developer’s Handbook

[3] JEAN J.LABROSSE,邵贝贝译. uC/OS-II 源码公开的实时嵌入式操作系统[M].北京,中国电力出版社

A Design Method for FPGA Remote Configuration

Zhang Xuesen Li Hong38th Research Institute of China Electronic Technology Corporation, Hefei230031,China

Update the design of FPGA depend on reading &writing the configurable chip, that is FPGA remote configuration. A design method for FPGA remote updating and configurating files on Ethernet base on system on a programmable chip(SOPC) in the article.

10.3969/j.issn.1001-8972.2010.14.048

张学森 男,1979年,工程师,研究方向:雷达信号处理,阵列信号处理;

李宏 男,1979年,工程师,研究方向:雷达信号处理,阵列信号处理。