高速高精度流水线模数转换器的设计

2010-10-18蔡小波李福乐

蔡小波 李福乐

摘要:本文给出了两版基于0.18mmCMOS工艺的12位100MS/s流水线ADC。测试、分析了两版芯片,经过改进版图得到满意结果。

关键词: 流水线ADC 参考电路 寄生电阻

引言

随着新一代无线移动通信时代的到来,通信系统中数字中频接收机对ADC的速度和精度的要求越来越高,而兼顾了速度和精度的流水线ADC是适应这种要求的较好选择。

在大规模模拟电路的设计中,由于电路规模比较大,提取寄生参数时如果提取寄生电阻,那电路节点数急剧增加,后仿真速度将会很慢甚至无法收敛,所以在提取寄生参数时一般只提取寄生电容,这样电路节点数不会增加,仿真时间也不会太长。但采用这种方式时仿真将忽略寄生电阻的影响,这与实际情况是有差别的,在版图设计时需酌情考虑,尤其当版图走线中有静态电流流过的时候。

本文给出了两次流片(tape out)的测试结果。着重分析了第一版芯片参考电压模块版图设计时由于不合理的布线,导线上的寄生电阻对ADC参考电压、静态特性和动态特性的影响,并用MATLAB搭建流水线ADC的行为级模型来模拟验证寄生电阻对ADC性能的影响。此外,根据对第一版芯片测试结果的分析,第二版芯片对参考电压产生电路的版图进行了修正然后重新流片,测试结果表明,对寄生电阻的分析是合理的,对应的修正措施也是行之有效的。

系统结构和关键电路模块设计

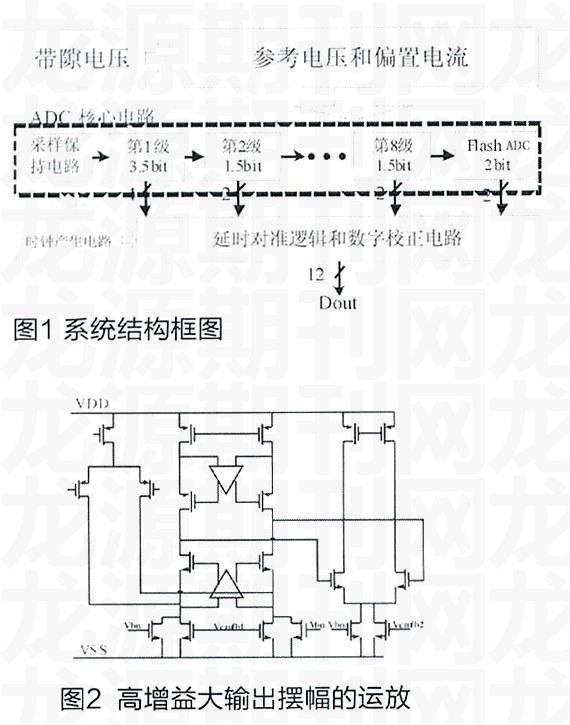

本流水线ADC的系统结构如图1所示,主要由时钟电路、参考电路和ADC核心电路三部分组成。ADC核心电路用采样保持放大器(SHA)采集模拟输入信号,接着第1级采用3.5位/级的结构,后面7级采用1.5位/级的结构,最后1级为2位的ash ADC。

采样保持放大器

如果不使用采样保持放大器,ADC的输入带宽将受限于孔径误差(aperture error)[1],所以本设计在级电路之前放置了一个SHA。从噪声和功耗两方面考虑,SHA采用电荷翻转式(flip-around)结构而不是电荷重分配式结构(charge-redistribution)。

级分辨率的优化

当第一级电路从采样相进入到建立相的一瞬间,运放输入端会产生一个阶跃电压Vx,文献[2]指出第一级电路分辨率越高这个阶跃电压Vx越小,意味着建立时间越短,并且对运放压摆率的要求越低。第一级电路分辨的提高可以降低对电容匹配的要求[3],从而可以不用校准电容失配而实现12位的ADC。此外,相比1.5比特/级的结构,3.5比特/级的结构在功耗和面积上都更有优势。

级缩减技术

由于系统对每一级建立精度的要求逐级降低,所以运放的速度和增益也可以逐级降低,从而运放的功耗和面积也逐级降低,这就降低了ADC的总功耗和总面积。此外,电容在MDAC工作过程中动态得充放电造成一部分动态功耗,所以也可以在满足KTC噪声要求的前提下逐级缩减电容值来降低功耗。在减少电容的同时,其实也减小了运放的负载,从而进一步减小运放功耗。