数字光端机的二次复分接设计

2010-09-26

(北方工业大学 机电工程学院,北京100144)

1 引 言

目前,大量的信息都是通过光纤传输的,随着传输信息种类的增多,传统的只能传输单一信息的传输设备,如只传输视频或只传输网络的设备各自独占光纤,造成了光纤资源的浪费。复分接技术是利用时分复用技术,将不同的数据进行合并和分离,有利于多种信息的传输[1]。可编程逻辑器件(FPGA)的应用使得复分接技术的实现变得容易。FPGA集成度很高,可以完成极其复杂的时序和组合逻辑电路功能,适用于高速、高密度的数字逻辑电路设计领域[2]。目前一些光端机采用的复分接方式不够灵活,造成信道利用率低。为此,本文提出一种二次复分接方法,将不同速率的数据灵活处理后,复接在一起进行传输,取得了很好的效果。

2 系统构成

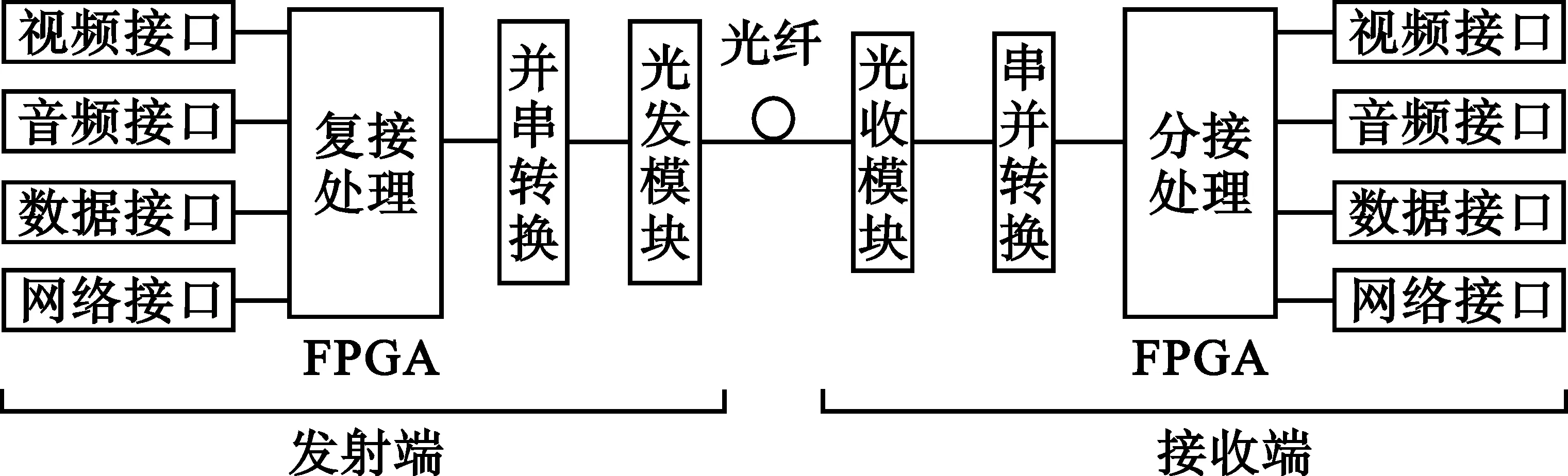

通过光纤进行信息传输的系统是由光传输设备和光纤组成[3],其中的光传输设备是成对使用的,简称为光端机。光端机的工作原理如图1所示。

图1 光端机原理Fig.1 Schematic diagram of optical translator and receiver

3 设计原理

设计为单模单光纤传输2路视频、2路立体声音频、8路数据及1路以太网的数据。光端机的传输分为正反两个通道,设计原理基本相同,本文只以正向通道的设计为例进行说明。

3.1 硬件设计

视频接口:AD部分采用AD9280芯片,15 MHz采样,8位量化数据输出;DA部分采用AD9708芯片,工作频率15 MHz,8位数据输入。

音频接口:AD部分采用CS5340芯片,将左右声道音频分别用78.125 kHz时钟采样24位量化加上8位同步码,两个声道共64位组成一位5 Mbit/s的数据输出。DA部分采用CS4344芯片,将左右声道音频还原。

数据接口:采用MAX232芯片,完成232数据接口电平和TTL电平转换。

网络接口:采用KSZ8995芯片,发射部分将100 Mbit/s以太网数据转换成5位速率为25 Mbit/s的数据,其中1位是使能数据。接收部分将5位25 Mbit/s的数据转换成100 Mbit/s以太网数据。

FPGA:采用Altera ep2c5芯片,具体工作由软件设计完成。

转换部分:并串转换部分采用LV1023芯片,串并转换部分采用LV1224芯片。

3.2 软件设计

整个软件设计在QUARTUS II下用VHDL语言编程实现[4]。

3.2.1FPGA对各个接口数据的采集

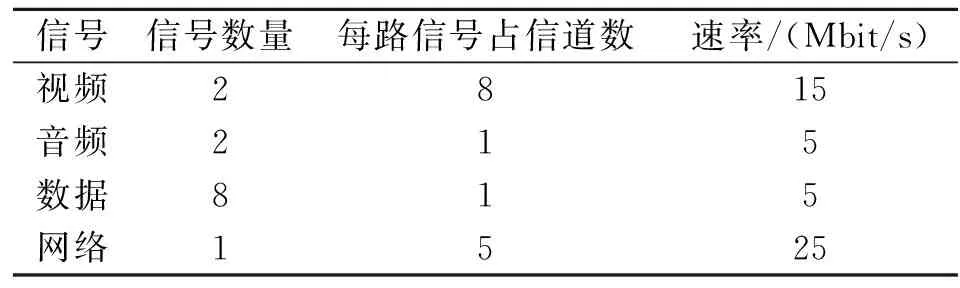

数据采集情况如表1所示。

表1 信号数据的采集情况Table 1 Collection statistics of signal data

3.2.2复接

复接是设计的重点。数字复接的方法按照各支路信号的交织长度分为按位复接、按字复接和按帧复接[5]。按位复接方法对设备要求简单,存储容量小,较易实现,但要求各个支路码速和相位都相同。按帧复接时不破坏原来各帧的结构,有利于交换,但要用很大容量的缓冲存储器。结合以上两种复接方法的特点,本设计采用按字复接的方法,此种方法既灵活,又不需要大容量的缓冲存储器,一个码字由一个字节即8位码组成。

数字复接方式从复接中各支路信号时钟间的关系角度分为同步复接、异步复接与准同步复接[5]。如果各支路信号的时钟并非来自同一时钟源,各信号之间不存在同步关系,称为异步复接。对于异步复接一般都要通过异步FIFO等进行异步数据同步化,如处理不当,容易进入亚稳态。准同步复接相对于同步复接技术来说增加了码速调整和码速恢复的环节。本设计采用同步复接的方式,与以上两种方式相比,既不易进入亚稳态,又没有码速处理的环节,系统更稳定可靠。

图2 复接原理Fig.2 Multiplexing principle

同步复接方式的各支路信号使用的时钟都是由一个时钟提供,而从表1看出本系统要复接的数据速率有3种。一次复接是不可能完成的,因而本设计提出了一种二次同步按字节复接的方法。它将各种不同速率的数据进行处理,使其能够灵活地组合在一起,在保证了不同速率数据传输的同时,也使信道的利用率大大提高。复接原理如图2所示。

每次复接8位数据,其中前七位为有效数据,第八位为标志位,分接时同步用。具体复接过程如下:

(1)网络数据的处理

利用FPGA内部的移位寄存器对网络数据进行串并转换,将5个25 Mbit/s的网络数据转换成25个5 Mbit/s的数据。

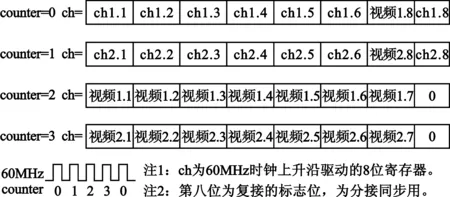

(2)一次复接

利用15 MHz时钟的上升沿触发一个模为3的计数器。一次复接是复接5 Mbit/s数据,复接后为15 Mbit/s数据,复接分为两组,具体过程如图3所示。

图3 一次复接原理Fig.3 The primary multiplexing principle

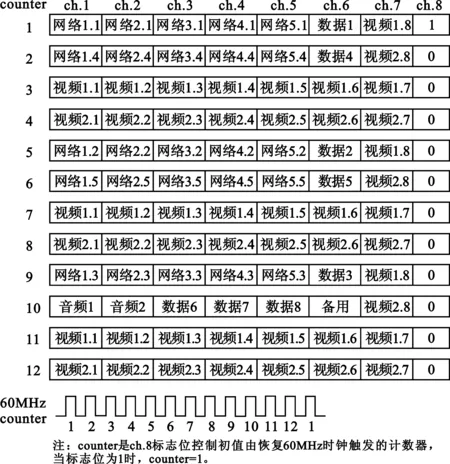

(3)二次复接

利用60 MHz时钟的上升沿触发一个模为4的计数器。二次复接是复接一次复接后的15 Mbit/s数据,复接后为60 Mbit/s数据,具体过程如图4所示。

图4 二次复接原理Fig.4 The secondary multiplexing principle

3.2.3分接

分接是复接的逆过程,在恢复60 MHz时钟的控制下完成12个节拍,由接收到的标志位来控制节拍的起始。恢复60 MHz时钟是由串并转换芯片送给的,其它时钟由此时钟分频得到。分接后的视频数据每隔4节拍变化一次,其速率为15 Mbit/s,其它的数据每隔12节拍变化一次,其速率为5 Mbit/s。用15 MHz恢复时钟将分接后的视频数据送到视频接口,用5 MHz恢复时钟分别将分接后的音频和数据送到音频接口和数据接口。对于分接后网络的5 Mbit/s数据必须进行处理,将25个5 Mbit/s的数据,还原成5个25 Mbit/s的数据。做法是在FPGA内部用25 MHz恢复时钟串行读取5个5 Mbit/s的数据,完成并串转换,再将5个25 Mbit/s的数据送到网络接口。分接过程如图5所示。

图5 分接原理Fig.5 De-multiplexing principle

4 测 试

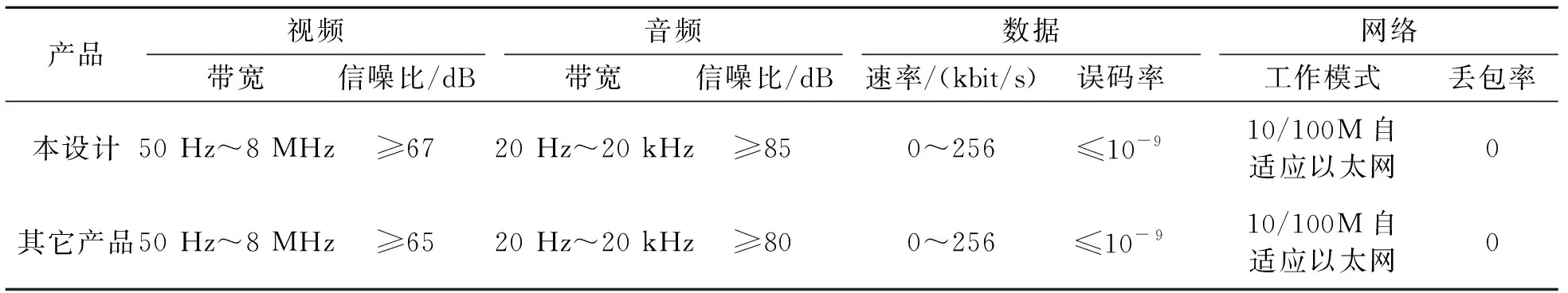

将编译好的目标文件下载到实验板FPGA上进行了测试。复接的过程中除了第八通道复接的标志位外,其它通道复接的全部是有效数据,信道利用率高。对于信号指标,经查阅国内同类技术资料并对一些产品进行实际测量,再与本系统各项性能指标作比较,结果表明本系统视频和音频的信噪比性能指标优于国内同类技术产品性能指标,如表2所示。

表2 信号指标Table 2 Signal parameters

5 结束语

本文研究了数字光端机的复分接方式,根据视频、音频、数据及网络等信号速率的不同,采用了二次复分接的方式,将不同速率信号的数据进行调整处理,二次复接后传输。测试表明,采用此种复接方式的光端机其信号指标好,性能稳定,信道利用率高,节省光纤资源,可广泛应用于智能交通、安防和工业监控等领域。把电话和E1同视频、音频、数据及网络信号复接在一起传输是进一步的研究方向。

参考文献:

[1] 褚改霞,潘卫,王栋,等.基于FPGA的多路数字信号复分接器的设计[J].电子技术应用,2009(5):43-46.

CHU Gai-xia,PAN Wei,WANG Dong, et al.Design of multi-channel digital signal multiplexer/demultiplexer based on FPGA[J].Application of Electronic Technology, 2009(5):43-46.(in Chinese)

[2] 王诚,吴继华,范丽珍,等.ALTERA FPGA/CPLD设计[M].北京:人民邮电出版社,2005:2-3.

WANG Cheng,WU Ji-hua,FAN Li-zhen,et al. Design of ALTERA FPGA/CPLD[M].Beijing:People′s Telecommunicaions and Posts Press, 2005:2-3. (in Chinese)

[3] 邱昆.光纤通信导论[M].成都:电子科技大学出版社,1995:111-117.

QIU Kun.The introduction of fiber communication[M]. Chengdu:University of Electronic Science and Technology of China Press, 1995:111-117. (in Chinese)

[4] 刘绍汉,杜灶生,刘新民. VHDL芯片设计[M]. 北京:清华大学出版社,2004:151-156.

LIU Shao-han,DU Zao-sheng,LIU Xin-min.The design of VHDL chip[M]. Beijing:Tsinghua University Press, 2004:151-156. (in Chinese)

[5] 孙莉萍,顾美康,李莉.基于FPGA的数字复接器的设计[J].中小企业科技,2007(7):177-178.

SUN Li-ping,GU Mei-kang,LI Li. Design of digital multiplexer based on FPGA[J].Small and Medium Enterprises Technology, 2007(7):177-178.(in Chinese)