SignalTapII ELA 的FPGA 在线调试技术

2010-08-27刘政蒋志勇

刘政,蒋志勇

(桂林航天工业高等专科学校电子工程系,桂林541004)

在设计基于FPGA 的电子系统时,一般需要用示波器、逻辑分析仪等外部测试设备进行输入输出信号的测试,借助测试探头把信号送到测试设备上进行观察分析。当然,前提是需要保留足够多的引脚,以便能选择信号来驱动I/O进行测试。但是外部的测试设备在测试FPGA系统时,常会遇到这样的情况:FPGA 的I/O 引脚数量不够丰富,PCB 布线和封装工艺复杂导致I/O 引脚引出困难,外部测试探头有影响FPGA 信号时序和完整性的可能[1-2]。

如果能在FPGA 内部嵌入具有外部测试设备功能的逻辑测试模块,那么以上问题就可以一一解决。Signal-TapII 就是这样一种嵌入式逻辑分析器(embedded logic analy zer),简称为SignalTapII ELA。它是QuartusII 软件中集成的内部逻辑分析软件,使用它可以实时观察内部信号波形,方便用户查找设计的缺陷。

1 SignalTapII ELA 的原理

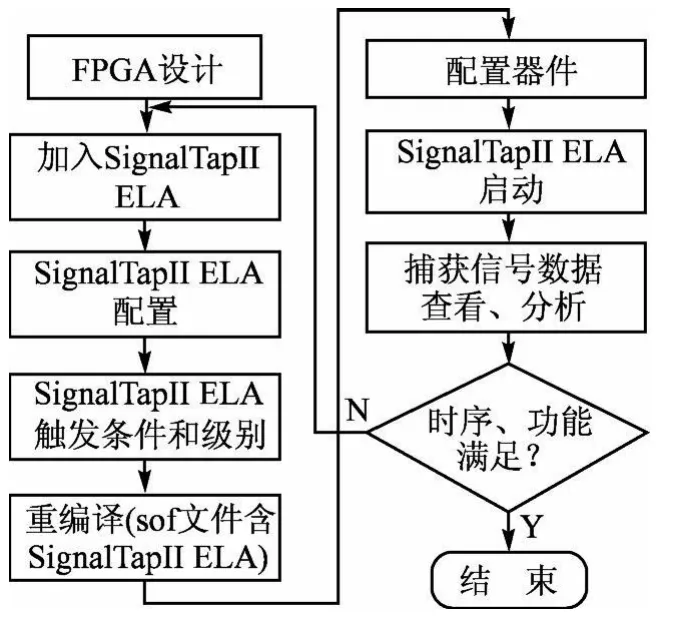

SignalTapII ELA 是Quartus 软件中第二代系统级调试工具。将SignalTapII ELA 代码和系统逻辑代码组合交由QuartusII 编译、综合、布局布线,生成sof 文件中内含SignalTapII ELA,把sof 文件配置到FPGA 内。FPGA 运行时,一旦满足待测信号的触发条件,SignalTapII ELA 就立即启动,按照采样时钟的频率捕获待测信号数据并暂存于FPGA 片内的RAM 中,采样数据不断刷新片内存储器,最后通过JTAG 口将捕获的信号从片内RAM 传至Quartus II实时显示。SignalTapII ELA 的原理流程如图1所示。

图1 SignalTapII ELA 原理流程

实际工程中,加入SignalTapII ELA 不会影响系统原有的逻辑功能。

2 SignalTapII ELA 的配置

SignalTapII ELA 基本配置过程[3]如下:

①添加采样时钟。SignalTapII ELA 在时钟的上升沿进行采样,可以使用设计系统中的任何信号作为采样时钟,根据Altera 公司的建议最好使用同步系统全局时钟作为采样时钟。但是在实际应用中,多数使用独立的采样时钟,这样能采样到被测系统中的慢速信号,或与工作时钟相关的信号。当然采样时钟的频率要大于被测信号的最高频率,否则被测信号波形会有较大误差。

②定义采样深度。采样深度决定了待测信号采样存储的大小,而可以采样的深度是根据设计中剩余的RAM块容量和待测信号的个数决定的。若待测信号较多,则在同样I/O Bank 个数情况下采样深度较浅。待测信号个数的增减和采样深度的深浅会直接改变RAM 块的占用情况,采样深度的范围为0 ~128 KB。

③定义RAM 类型。设置占用片内何种RAM 块资源,随着采样深度的改变,RAM 块的数据线和地址线宽度可以分割成多种组合。例如:采样深度是1 KB,RAM数据线、地址线可以分割成2×512 或4×256 等多种组合。依此类推。

④定义触发位置。Pre trigger position 表示采样到的数据12%为触发前,88%为触发后;Center trigger position表示采样的数据处于触发前后各一半;Post trigger position 表示采样到的数据88%为触发前,12%为触发后。

⑤触发条件级数设置。SignalTapII ELA 支持多触发级的触发方式,最多可支持10 级触发,帮助滤除不相干的数据,更快地找到需要的数据。若有多级触发条件,首先分析第一级触发条件。若第一级为TRUE,则转到分析第二级是否满足,直到分析完所有触发条件均为TRUE才最终触发时钟采样数据。

⑥触发条件。设定约束性的触发条件。可以允许单个信号的独立触发条件Basic,直接采用单个外部或设计模块内部的信号;也可以允许多个节点信号的组合触发条件Advanced,构成触发函数的触发条件方程。例如:使能信号ENA 与4 位输出信号Q 相与后触发,触发条件=ENA&(Q=15)。

⑦添加待测信号。可以使用Node Finder 中的SignalTapII ELA Filter 查找所有预综合和布局布线后的SignalTapII ELA 节点,添加待测的中间信号和端口信号。SignalTapII ELA 不可测试的信号包括:逻辑单元的进位信号、PLL 的时钟输出、JTAG 引脚信号、LVDS(低压差分)信号等。

完成STP 配置,将sof 文件配置到FPGA ,运行SignalTapII ELA ,当待测信号条件满足时,数据捕获开始,捕获的数据以波形的形式表示出来。Sig nalTapII ELA 也可将捕获数据通过多余的I/O 引脚输出,以供外部的测试设备使用。

3 实例分析

本文以一个基于DDR SDRAM 高速数据采集IP 核的设计为例[4],具体说明如何用SignalTapII ELA 来进行FPGA 在线调试。使用Altera 公司的器件CycloneII 系列FPGA EP2C5F256C6,该器件支持SignalTap II ELA。

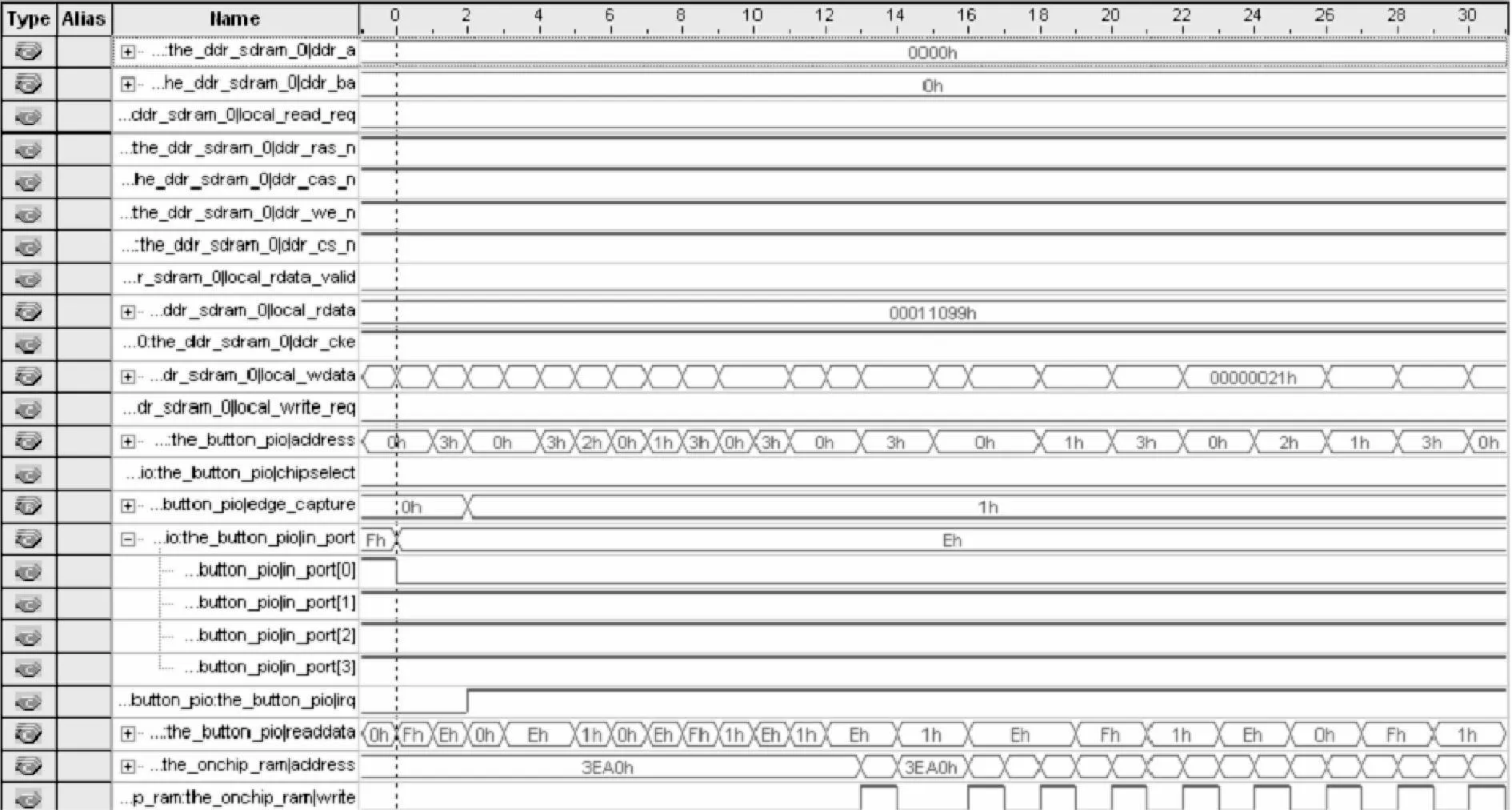

当前需要测试来自3 个模块的信号:外部存储器DDR SDRAM 与FPGA 的接口信号、FPGA 内部输入输出PIO 寄存器信号、FPGA 内部RAM 接口信号。

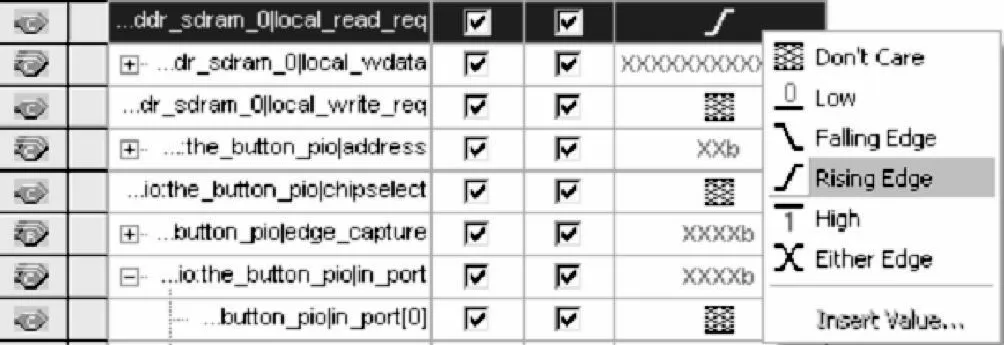

先关闭增量编译,设置采样时钟为外部独立时钟CLK=50 MHz;采样深度为256;RAM 类型为M4K ,数据宽度分割为256×1;触发位置为Pre trigger position;触发信号为DDR SDRAM 读操作信号;触发条件为Basic 单信号触发;触发条件级数为1 级。从图2 可知,该触发信号设置为上升沿触发有效。重新编译后将包含SignalTapII ELA 的sof 配置文件下载到FPGA 中,图3 即是从Signal-Tap II ELA 数据窗观察到的来自FPGA 内部实时信号的捕获波形。

图2 触发条件设置

图3 捕获的信号波形

如果设计文件中添加SignalTapII ELA 后编译时间显著增加,可以考虑使用Start Analysis &Elaboration代替Start Analysis &Sy nthesis,这样可以显著缩短编译时间。

加入SignalTapII ELA 后,如果发现一些用于调试的逻辑(比如调试用的计数器)被优化掉,不能出现在波形中,可以尝试这样解决:在HDL 设计文件中对要调试的信号添加保持或保护属性[4]。

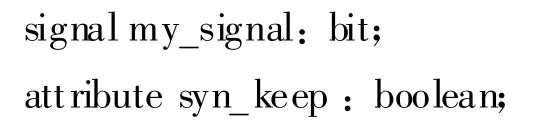

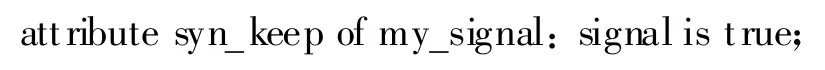

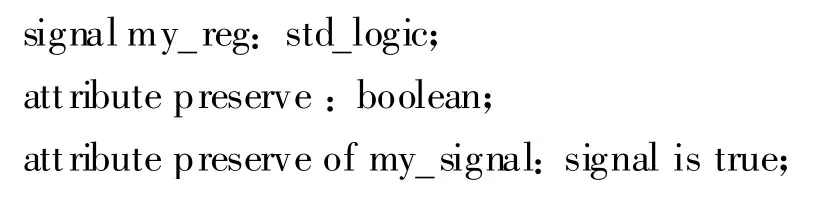

保持属性主要用于信号和网络节点。代码如下(以VHDL 为例):

保护属性主要用于寄存器。代码如下(以VHDL 为例):

通过改变待测信号的触发方式和条件,可以捕获到其他相类似的信号波形,这里就不一一列举。

需要注意的是,SignalTapII ELA 本身是一块独立逻辑资源,需要占据FPGA 资源。比如RAM、LE 等,资源消耗量与需采集的数据量成正比,采集存储的数据深度由设计中的内部RAM 剩余大小决定。在调试完成后,需将SignalTapII ELA 从系统逻辑设计中移除,以免浪费资源和影响设计的性能。

结 语

通过对FPGA 内部信号的捕获测试,可以实现对系统设计缺陷的实时分析和修正。与外部测试设备相比,可以总结出SignalTapII ELA 的几点优越性:不占用额外的I/O引脚,不占用PCB 上的空间,不破坏信号的时序和完整性,不需额外费用;从多方面证实,该测试手段可以减少调试时间,缩短设计周期。

[1]李文江,赵增辉.用SignalTap II 逻辑分析仪调试FPGA[J].无线电工程,2007,37(1):48-50.

[2]孟令军,李娜.基于FPGA 的内部逻辑在线测试技术研究[J].电测与仪表,2008,45(11):34-37.

[3]王成,吴继华.Altera FPGA/CPLD 设计(基础篇)[M].北京:人民邮电出版社,2005.

[4]Altera Corporation.Using SignalTap II Embedded Logic Analyzers in SOPC Builder System s[OL].(2007-11)[2009-11-02].http://www.altera.com/literature/an/an323.pdf.