基于Verilog HDL的SPI IP核的设计及仿真实现

2010-08-24白光泽

白光泽,邢 燕

BAI Guang-ze1,XING Yan2

(1.长春职业技术学院,长春 130033;2.长春物业管理学校,长春 130033)

0 引言

集成电路(IC,Integrated Circuit)作为各种信息设备的核心,它体现一个国家的利技实力、综合国力及对科学界和社会的影响力,它也是国家的战略性产业。为了抓住IP设计技术这一提升我国设计水平、发展IC产业不可多得的历史机遇,信息产业部于2002年成立了集成电路IP核标准工作组,为我国IP核标准的制定及其在业界的推广等方面做了大量的工作。因此,研究、开发和应用IP核技术,对企业、对国家、乃至对全球的IC产业的发展都有着至关重要的意义。

随着SOC的规模不断扩大,集成的IP模块不断增多,复杂程度不断加大,使得片上各个模块之间的通信问题越来越突出,为了解决这一问题,各大公司都相继推出了自己的IP核互联规范。另外,长期以来,外围设备与主机CPU速度之间的不匹配始终困扰着人们,影响了计算机系统的迅速发展,随着计算机处理能力及存储规模的迅速增长,这个问题表现得更加突出。

本文的针对SOC片上系统的SPI接口设计[1],目标是实现适用于SOC设计并且符合SPI通行协议的IP核,让SOC通过此SPI核可以与外围设备通信,中间以片上总线Wishbone为接口。设计中,本着片上系统SOC要求的高度集成和低功耗的特点,在设计时将面积和功耗放在了第一位,这意味着在用Verilog HDL编程时,必须在遵循SPI协议、实现基本SPI通信的基础上,将RTL级逻辑门数尽可能的减少。保留规定的四个外部信号,将SPI主机与从机分开,仅设计SPI_MASTER Core,利用控制寄存器进行状态控制,省去时钟极性与相位配置,直接与Wishbone总线连接。其次,围绕着SPI IP核的设计与实现来讨论和研究SOC设计中IP设计的方法。

SPI Master设计是本设计的核心,其主要目标是能实现Wishbone Master对SPI Maste的初始化,配置SPI Master的控制寄存器,以实现对SPI各传输模式的控制,及其双向数据通信。其次,是实现SPI Master与SPI Slave之间的数据双向通信,从而实现SOC与外界的数据通信。在设计程序时,采用了top-down至上而下的设计流程,那么首先做的是对所要设计的SPI IP核做总体的规划,建立架构,对系统进行层次划分。

1 WISHBONE接口信号声明[2, 3]

根据前面对Wishbone总线的介绍,在本设计中spi_master模块内Wishbone接口就是初wishbone slave接口。按照Wishbone协议,端口定义如下表1所示:

表1 Wishbone slave接口信号表

2 程序模块介绍

1)spi_defines模块

该模块是宏定义模块,主要规定了分频值由访divider,允许一次最大传输字节SPI_MAX_CH,从机扩展数SPI_SS_NB以及各寄存器的相关数据。这里采用了define来定义,主要一个特点就是这些宏定义中的参数都是全局的,并不局限在某个module范围之内,这样可以便于对所设计的IP核的参数做修改,从而提高IP核的通用性和可移植性。

2)spi_master模块

由前面的设计思路可知,该模块要完成与wishbone_master的连接,实分频和串并转换。按照设计目标,可将spi_master划分成如下的功能块和模块:

(1)地址解码;

(2)读寄存器,并行输出至wishbone

(3)写寄存器,由wishbone并行输入对曲divider, control和 slave slect寄存器初始化;

(4)实现分频,spi_clgen子模块;

(5)实现串并转换,spi_shift子模块。

3)spi_slave模块

spi_slave用于完成数据串行输入输出,其时钟信号是spi_clgen产生的sclk,与spi_shift时钟同步。注意的是,spi_slave均是从其数据寄存器最高位串行输出miso,从最低位串行输入miso,且传输和接收的时钟边沿与spi_shift相同。

4)wb_master模块

该模块在本设计中只是作为SOC端,来模拟SOC对spi_master读写数据,其中只是简单地运用任务(task)写了一个读任务、一个写任务和一个数据比较任务。

3 设计仿真与验证

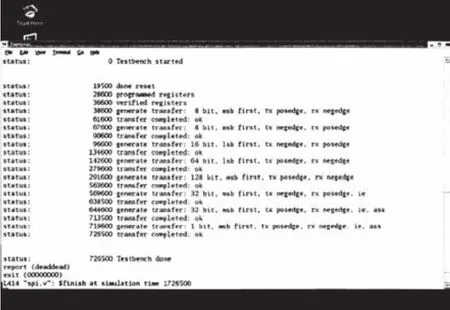

仿真与验证是IP核设计中非常重要的一部分,因为它直接关系着IP的可用性。考虑到设计的SPI的门数和速度上的要求比较低,以及实际资金等清况,在仿真时,本文采用软件仿真[4,5]的方式。为突出典型性和正确性,所以spi_master只选择了与一个spi_slave连接进行通信,在不同的传输要求下,分别检测lbit,8bit,16bit,32bit,64bit和128bit数据传输,测试的基本步骤为:首先是调用Wb_master模块中的写任务对各个相关寄存器进行初始化,完成传输之前的准备工作,结束之后,会显示在某时刻programmed register;之后,是调用数据比较任务,对写入寄存器的数据进行验证,确认之前写寄存器操作的正确性,完成之后会显示在某系统时刻 verified register;接着是进行不同位数、不同顺序的传输:最后对比传输之后的数据与期望的数据,从而验证传输的正确性,如果传输正确则显示 transfer completed ok,否则,显示错误。

另外,在spi_defines模块中,本文测试时设置了最大传输数据长度为128bit,先对 spi_master进行初始化,然后对各寄存器写入数据,第一次是8bits的传输,spi_master tx0中并行数据为32'h5a,spi_slave数据寄存器内为32'ha5967e5a,首先传高位,上升沿传输,下降沿采集,按照spi_shift模块中tx寄存器的传输规则,传输完成之后spi_slave.data=32'h967e5a5a以tx0=32'ha5;第二次与第一次一样是8bits的传输,tx0=32'ha5,只是换成在下降沿传输,上升沿采集,传输完成之后spi_slave.data=32'h7e5a5aa5以及tx0=32'h96;第三次是16bits的传输,首先传低有效位(lsb first),tx0=32'h5aa5,此时spi_slave.data=32'h7e5a5aa5,由于是lsb first,按照tx的传输规则,32'h5aa5的lsb先传输,则变为32'ha55a从spi_slave.data的最低位经mosi串行输入,同时spi_slave.data[31:16]=16'h7e5a,由最高位开始经miso并行输入tx,从tx的最低位开始锁存,16'h7e5a变为16'ha57e,所以传输完成后spi_slave.data[15:0]=16'ha55a以及tx0=32'h5a7e;同理,测试程序对64bit,128bit,32bit,1bit进行了检测,以及在ie和ass赋值的情况下。最后在linux环境下的EDA平台上,用Ncverilog进行仿真,最终得到了较满意的仿真结果,仿真结果如图2,所有仿真模式全部通过。

图2 SPI IP 核的仿真结果

[1] L.Bacciarelli.G.Lucia.Design,testing and prototyping of a software programmable I2C/SPI IP on AMBA bus.Research in Microelectronic and Electronic.2006: 373-376.

[2] 牛风举.刘元成.朱明程.基于IP复用的数字IC设计技术.电子工业出版社,2003.

[3] 李宽余.戴瑜兴.张义兵.基于可编程逻辑器件的串行外设接口设计及实现.低压器件,2004(11):28-30.

[4] Cadence Design Systems Inc.Verilog-XL Reference [C].Cadence, 2003.

[5] 陈献文.HDL Debugging with Debussy [M].2004.