AD9707高速DAC的内部寄存器配置

2010-08-14赵孔新毕韬

赵孔新,毕韬

(长春工业大学 计算机科学与工程学院,长春130012)

赵孔新(教授),研究方向为模式识别与智能系统;毕韬(硕士研究生),研究方向为数据采集与数据处理。

引 言

随着通信、工业仪器设备和便携式设备的发展,新一代高速DAC逐渐朝高性能、低功耗、芯片多功能集成和输入输出高速化的方向发展。AD970X系列DAC针对低功耗特性进行了优化,同时仍保持出色的动态性能,适用于手持便携式仪器等需要有效合成宽带信号的场合。AD9707精度高达 14位,其采样率为175 M sps,内部集成边沿触发式输入锁存器,1.0 V温度补偿带隙基准电压源和自校准功能使之能提供真14位INL与DNL性能。AD9707还具有共模电位移动能力,当与其他模拟器件连接时无需电平移动电路,从而简化了模拟电路的设计,并且减小了小型便携式设计中的印制电路板面积。

由于DAC内部集成度越来越高,外围辅助电路越来越少,通过外围引脚的设置很难把DAC所有的功能发挥出来。高速DAC内部一般集成内部寄存器,用户可以通过修改DAC的内部寄存器,使DAC输入输出模式达到设计要求。为了减少芯片引脚数量,内部寄存器一般是通过串行接口来配置,比较常见的接口有 SPI、I2C和串行2-wire等。AD9707使用的是SPI接口。

1 AD9707测试

测试电路主要由Samsung公司微处理器S3C2410、Altera公司CycloneIII系列FPGA EP3C25和ADI公司的AD9707组成。FPGA主要负责算法,ARM微处理器主要负责控制字输入和 LCD显示。测试时,分别使用S3C2410的SPI接口和EP3C25模拟SPI接口,来配置AD9707内部寄存器。测试的过程是,在FPGA中构建了一个DDS(数字直接频率合成器),通过修改控制字来改变输出波形数据,经AD9707转换后检测输出的波形。

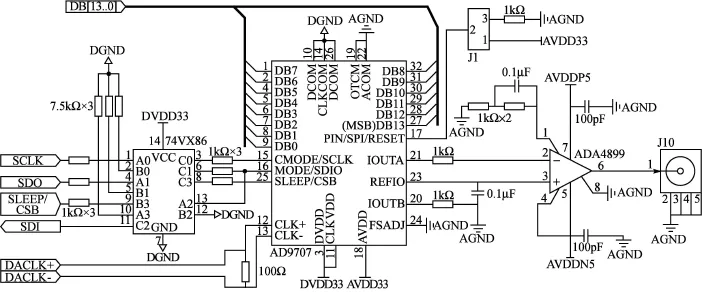

如图1所示,AD9707的基本外围电路由低电压异或门74VX86和运算放大器ADA4899组成。测试时可以通过跳线J1选择AD9707的工作模式:高电平时为PIN模式;低电平时为SPI模式;出现高电平脉冲时复位内部寄存器。图中AD9707的输入时钟选择差分时钟;输出选择单端输出,正向输出端IOUTA与ADA4899的反相输入端相连,反向输出端IOUTB接地;内部基准电压源 REFIO与 ADA4899的同相输入端相连。ADA4899将AD9707单端输出的电流变化转换为电压变化。外部使用内部基准电压源时,REFIO引脚需用一个0.1 μ F电容接地。74VX86与外部 SPI接口相连,主要起电压匹配整形作用。它的电压范围为1.2~3.6 V,支持AD9707工作的1.8 V和3.3 V。

图1 AD9707的基本外围电路

2 SPI模式下AD9707与外部CPU的通信

在AD9707测试之前,必须按照外围电路的设计配置好AD9707的工作状态。AD9707有两种配置模式可供选择:PIN模式和SPI模式。设备可以通过PIN模式进行简单配置,也可以通过SPI模式进行高级配置。当用户使用自校准等高级功能时,必须使用SPI模式配置AD9707内部寄存器。

SPI(Serial Peripheral Interface,串行外围设备接口),主要应用在 EEPROM 、Flash、ADC/DAC上 。SPI是一种高速的、全双工、同步的通信总线,在芯片的引脚上只占用 4根线,为PCB的布局节省了空间。正是由于这种简单易用的特性,现在绝大多数芯片都集成SPI通信协议。

SPI的通信原理很简单,它以主从方式工作。这种模式通常有一个主设备和一个(或多个)从设备,需要4根线(单向传输时3根也可以)。AD9707的SPI接口由SCLK(串行时钟)、SDIO(数据输入输出)和CSB(片选)3根信号线组成。串行时钟SCLK用来同步数据,并从AD9707中运行内部状态机,最大频率是20 M Hz。串行数据输入输出SDIO作为双向的数据总线,用于发送或接收数据。片选信号CSB低电平时启动通信周期,它允许多个设备在同一条通信线路上使用。当CSB为高电平时,SDIO引脚为高阻抗状态。在整个通信周期内,CSB必须保持低电平[1]。

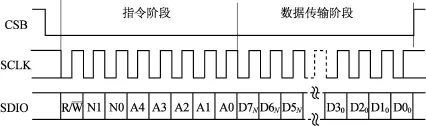

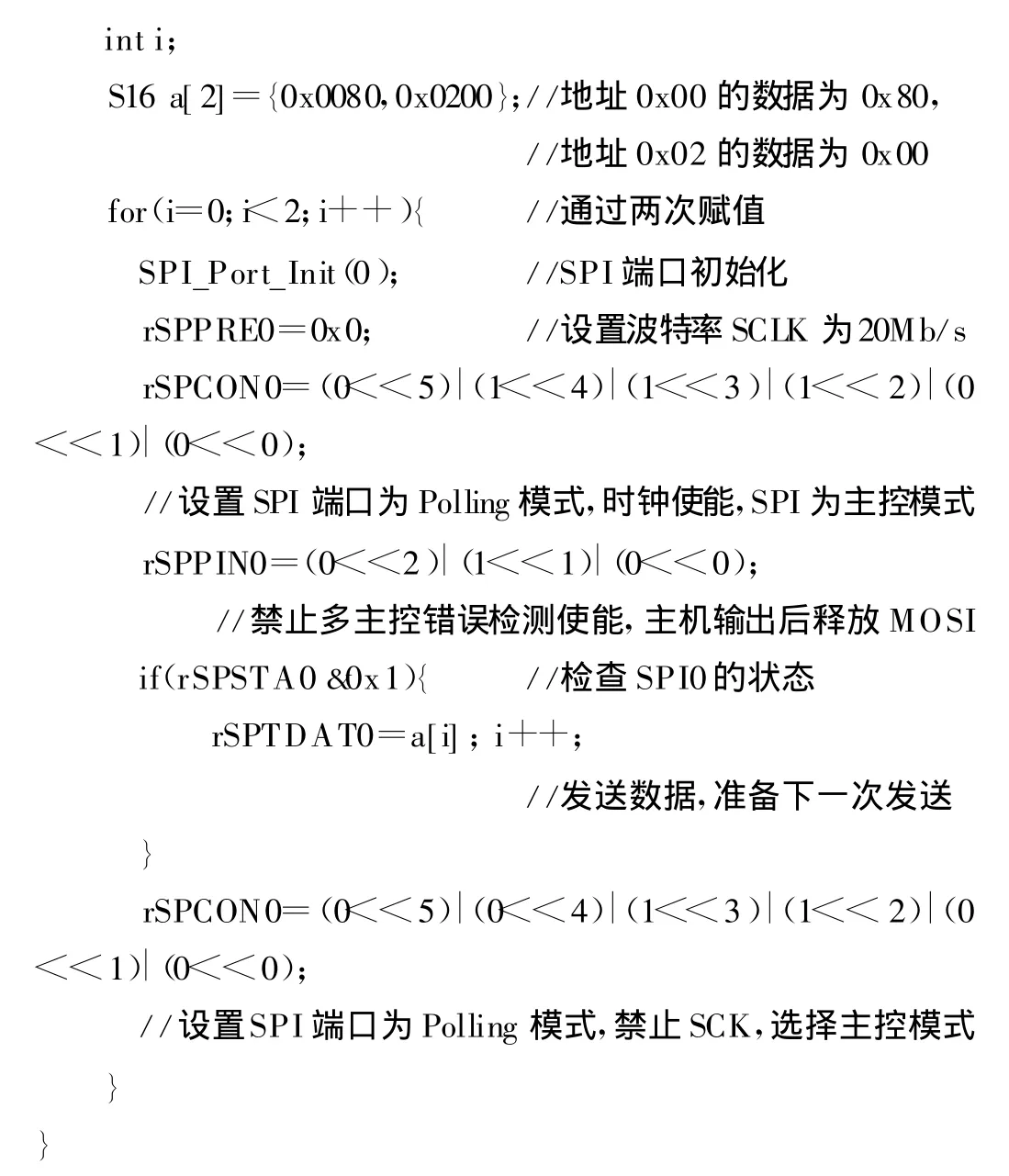

图2是外部SPI端口与AD9707通信的时序图。

图2 最高有效位先写入的SPI通信时序

整个通信周期分为指令阶段和数据传输阶段。第1阶段是指令阶段,在前8个SCLK上升沿时将8位指令字节写到AD9707中。指令字节决定了通信中第2阶段的数据传输模式,定义第2阶段的数据传输是读或写,以及数据传输的字节数和传输数据第1个要修改的寄存器地址。指令字节组成如下:

MSB LSB 7 6 5 4 3 2 1 0 R/W N1 N0 A4 A3 A2 A1 A0

第2阶段是数据传输阶段,在此阶段外部SPI控制器与AD9707开始传输数据。一次传输的数据量由指令阶段来决定,可以传输1~4个字节的数据。每个字节最后一位传输完成后,寄存器立刻改变。

当AD9707的 17脚(PIN/SPI/RESET)上有一个下降沿电平变化时,SPI端口的计数器将复位到指令周期的初始状态。如果SPI端口正处于一个指令周期或数据传输周期,寄存器中不会写入任何数据。

AD9707内部寄存器主要包括:寄存器SPI CTL,地址为0x00,用于设置SPI通信的具体模式、软复位和内部参考源等,按照测试电路要求设置为0x80;寄存器DATA,地址为0x02,主要用于设置输出模式选择、数据上升沿锁存和时钟输入模式选择等,按照测试电路要求设置为0x0;寄存器CALMEM、MEMRDWR和TRIM等用于校准和静态寄存器访问。测试时主要使用寄存器SPI CTL和DATA。下面围绕着这两个寄存器的配置介绍两种配置方式。

3 通过SPI端口配置AD9707内部寄存器

3.1 使用ARM微处理器的SPI接口

S3C2410是Samsung公司推出的采用 RISC结构的16/32位ARM微处理器。它基于ARM920T内核,采用五级流水线和哈佛结构,频率达到203 MHz,是高性能、低功耗的硬宏单元。S3C2410还包含下列部分:LCD控制器(STN&TFT)、NAND Flash引导装入程序、系统管理(片选逻辑和 SDRAM 控制器)、3通道 UART、4通道DM A、4通道 PWM 时钟、I/O 口 、RTC、8通道 10位 ADC及触摸屏接口、I2C总线接口、I2S总线接口、USB主口和设备口和2通道SPI总线接口。

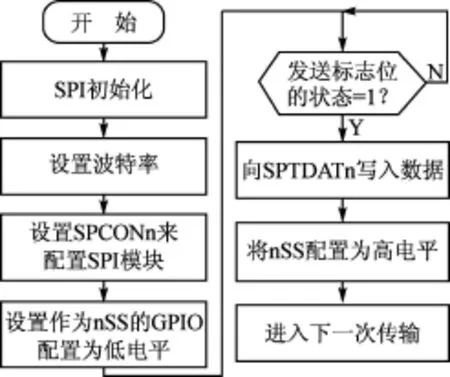

S3C2410具有2个SPI接口模块,每个模块分别具有2个8位移位寄存器用来接收和发送数据。数据的接收(串行移入)和发送(串行移出)是同时进行的,串行数据的速率由相应的寄存器设定。其时序很简单,主要是在CLK的控制下,2个双向移位寄存器进行数据交换。当一个数据写入SPTDATn寄存器时,如果 ENSCK和SPCONn寄存器中的MSTR位被置位,则启动数据发送[2]。SPI接口发送数据的流程如图3所示。

图3 SPI数据发送流程

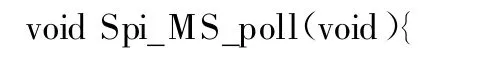

使用S3C2410的SPI端口0来配置AD9707内部寄存器的主程序如下:

使用 S3C2410的 SPI接口可以很方便地配置AD9707,但是在测试电路板上S3C2410离AD9707较远,布线时比较复杂,不得不使用飞线。为了解决布线困难的问题,采用FPGA模拟SPI接口配置AD9707内部寄存器。

3.2 使用FPGA模拟SPI接口

FPGA(Field Programmable Gate Array)即现场可编程门阵列。FPGA的使用非常灵活,同一片FPGA通过不同的程序可以产生不同的电路功能。本文使用VHDL语言编写一个SPI控制器,来发送配置数据给AD9707。

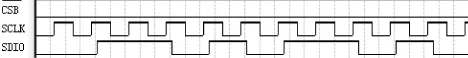

当仅需要向AD9707中写入数据时,使用SPI时钟线SCLK、SPI数据线SDIO和片选线CSB即可通信。根据图2中的写入时序编写程序[3],具体代码如下:

程序编译仿真后得到的时序图如图4所示。整个程序综合之后仅占用4个逻辑单元,使用类属参数定义配置数据,方便用户按照自己的设计随意修改。由于AD9707与FPGA直接相连,用FPGA直接配置AD9707在 PCB走线上方便很多,比较适合于我们的测试平台。通过在FPGA中构建的DDS发送波形数据,即可构成一个简易波形发生器,产生一些常见的波形。

图4 FPGA模拟SPI接口发送数据的时序仿真图

结 语

本文着重介绍了使用ARM微处理器和FPGA这两种常见的嵌入式处理器来配置AD9707,具有一般性和实用性。经测试检验,配置正确。由于大多数公司的DAC都是使用SPI接口配置内部寄存器,因此本文的程序也可用于配置其他DAC。

[1]Analog Devices.AD9707 Datasheet,2006.

[2]范书瑞,赵燕飞,高铁成.ARM处理器与C语言开发应用[M].北京:北京航空航天大学出版社,2008.

[3]Pedroni Volnei A.VHDL数字电路设计教程[M].乔庐峰,王志功,等译.北京:电子工业出版社,2005.