1.9 GHz低电压低功耗CMOS射频低噪声放大器的设计*

2010-08-12周建明陈向东兰萍谢睿徐洪波

周建明,陈向东,兰萍,谢睿,徐洪波

(西南交通大学信息科学与技术学院电路与系统研究所,四川成都610031)

随着无线通信技术的蓬勃发展和广泛应用,无线终端系统的小型化、低功耗、低成本和高性能已成为发展趋势。对于多级级联系统,第一级的噪声性能对整个电路的影响最大,而低噪声放大器(LNA)作为无线通信系统射频接收机前端的关键模块,其性能对射频接收系统的性能起着至关重要的作用。因此,为了降低整个系统的噪声系数,得到良好的系统性能,一方面要求其具有足够低的噪声系数,输入输出阻抗匹配,高线性度和低功耗,同时还要求其具有一定增益以降低后级系统的噪声系数。

但在实际电路设计中,这些性能指标之间并非相互独立,而是相互牵制、相互影响。因此在进行LNA设计时,采用折衷原则优化参数和改进电路结构,以提高各项性能指标。本文采用TSMC 0.18 μm CMOS工艺设计了工作于1.9 GHz的CMOS低噪声放大器,通过改进电路结构和优化参数,得到良好的仿真结果。

1 LNA电路设计

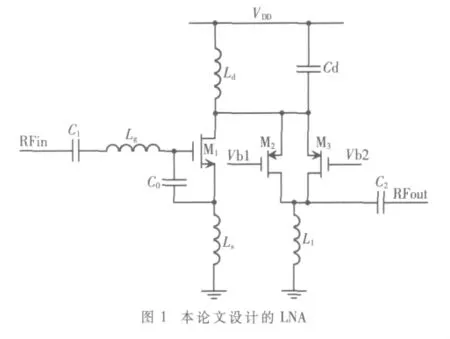

目前,为了满足低噪声放大器不同性能指标的要求所提出的不同电路结构中,公认为较好的电路结构形式是在共源极采用源极电感负反馈的共源共栅级结构,它能实现与信号源阻抗匹配[1]减小米勒效应,但其不能工作在低电压下,因此为了获得低功耗,本文在传统共源共栅结构基础上进行改进,采用折叠共源共栅结构[2],并在折叠结构输出极并联PMOS管,使其工作在线性区附近,利用晶体管线性补偿技术,提高低噪声放大器的线性度。电路如图1所示。

从结构上分析,该电路有以下特点:

(1)采用折叠共源共栅结构,将两层晶体管变化为一层晶体管以降低共源共栅电路工作所需要的电源电压,进而降低整个电路的功耗,同时这种结构也提高了输入与输出之间的隔离度;

(2)在M1漏极和栅极之间并联一电容C0,可以同时获得最小噪声系数并实现输入阻抗的共轭匹配,另外还可以解决功耗与噪声之间的矛盾;

(3)在输出极并联PMOS管M2,根据对单个晶体管线性度的分析,可以通过改变M2的栅源偏置,让其工作在线性区,利用M2的线性补偿技术降低M3晶体管的三阶跨导gnm,使其趋近于零,从而改善整个电路的线性度。

总之,在低噪声放大器的设计过程中,在满足输入、输出阻抗匹配以及增益要求前提下,噪声系数和线性度2个性能指标的优化显得更为重要。因此,本文也将重点从噪声系数和线性度这2个方面进行详细的分析。

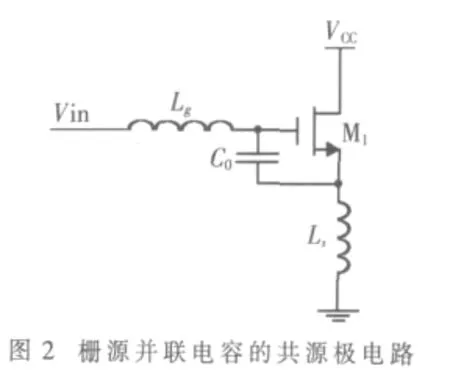

1.1 低噪声放大器噪声分析

传统的折叠共源共栅CMOS LNA的结构具有易于实现输入阻抗匹配、低功耗、减小米勒效应和提高隔离度等优点,但该结构的LNA不可能在要求达到最小噪声系数的同时实现输入阻抗共轭匹配而获得最大传输功率。为了解决二者间相互制约的矛盾,本文采用传统方式[3]在M1源极和栅极之间并联一电容C0,电路如图2所示。

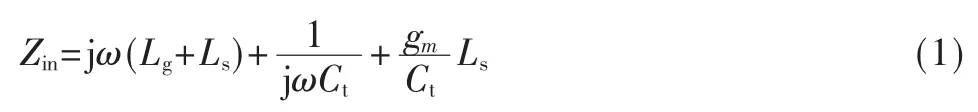

通过对该电路的分析,从信号源看过去的输入阻抗为:

其中Ct=Cgs+C0,在式中,增加并联电容C0并不会增加功耗。而且电容的增加必然导致串联电感Lg减小,同时可以降低对Lg高品质的要求。更利于低噪声的实现。

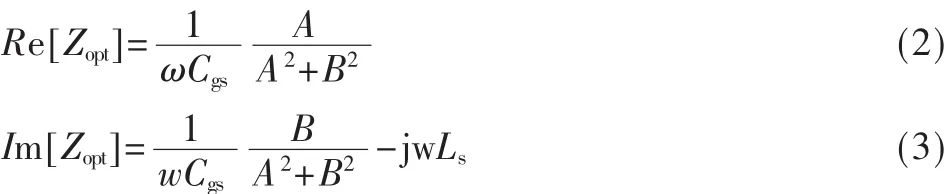

对于噪声系数的公式,参考文献[3]给出了详细的推导过程。为了获得最优的噪声系数,系统获得最佳噪声的输入阻抗实部与虚部分别如下所示:

综上所述,加入并联电容C0,能在低功耗的约束下,解决两者之间的矛盾进而实现噪声系数的优化和输入阻抗匹配。

1.2 LNA线性度的分析

对于线性度的改善,也是低噪声放大器设计过程中面临的重要挑战,传统的方法是采用源极或射极负反馈技术,对于本文所设计的折叠共源共栅电路,也是在共源极采用电感源极负反馈,但由级联系统的线性度表达式(4)可知,在级联系统中,后级对整个系统线性度性能影响更大。参考文献[4]中采用经典的折叠源极负反馈的共源共栅结构,输入三阶交调点仅0.77 dBm。所以在第一级采用负反馈对线性度的改善极其有限。

本文利用晶体管的幂级数非线性分析法[5],求得三阶交调遮断点IM3,有:

因此,根据三阶交调点IIP3定义,得:

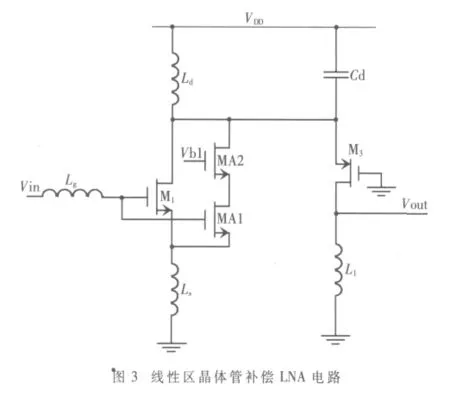

由IIP3定义式(6)可知,IIP3与晶体管跨导有关,如果晶体管三阶gnm趋近于零,则IIP3将趋近于无穷大。根据输入三阶交调点的这个特点,一种新的改善线性度的电路结构如图3所示[4]。

第一级共源级并联共源共栅晶体管,利用该结构对晶体管进行线性补偿。但该电路有2个缺点:

(1)级联系统的线性度,主要取决于后级电路,在第一级采用线性补偿技术来提高线性度,效果不如在输出级改善明显;

(2)并联的2个晶体管中的一个工作于弱反型与强反型之间的过渡区,此时漏端电流同时由漂移电流和扩散电流组成,晶体管的截止频率以及噪声系数都急剧恶化。

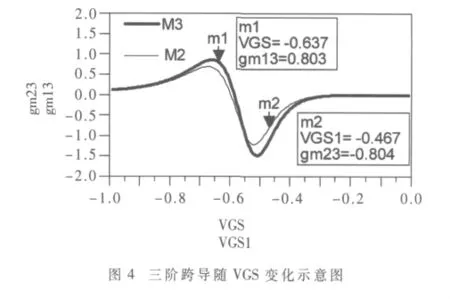

因此,为了克服以上缺点,得到低的噪声系数和高的线性度,本文在这个电路基础上进行结构优化,电路如图1所示,即在输出极采用2个PMOS管,M2,M3组成并联共源极,根据PMOS管的直流特性,随着晶体管偏置VGS的减小(|VGS|≥|Vth|)M3从线性区过渡到饱和区,M3的三阶跨导随偏置电压VGS的变化由图4可知。M3的三阶跨导曲线在(|VGS|≥|Vth|)区间会出现一个峰值点,晶体管的三阶跨导偏大,不易于IIP3的提高,因此,可通过适当的改进电路结构来抵消这个峰值。

即在晶体管M3的基础上并联M2,通过改变M2的栅极偏置,让其工作在线性过渡区,产生一个“谷”用以抵消M3的“峰”,如图4所示。m1为晶体管M3工作在饱和区的峰值点,m2为晶体管M2工作在线性过渡区的波谷点,两者相加后总的三阶跨导几乎趋近于零。根据式(6)的分析,输入三阶交调点得到极大提高,从而改善了LNA的线性度。从结构来分析,该电路唯一的缺点就是增加了功耗,但M2工作在线性过渡区,电流很小,对整个电路的功耗影响有限。因此,最后通过折衷考虑,该电路在略微牺牲功耗的前提下,LNA的线性度大幅度提高。

2 仿真结果与对比验证

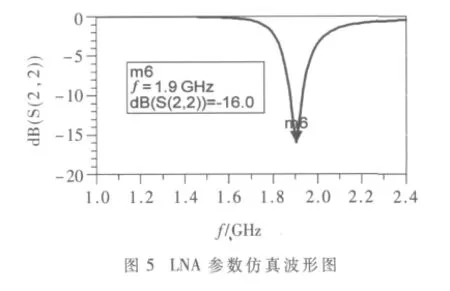

为了验证所提出的LNA结构的有效性,采用TSMC 0.18 μm CMOS工艺库,基于BSIM3模型,采用Agilent公司的ADS2008对图1所示的LNA进行设计并仿真,图5为本文设计的LNA参数仿真波形图。

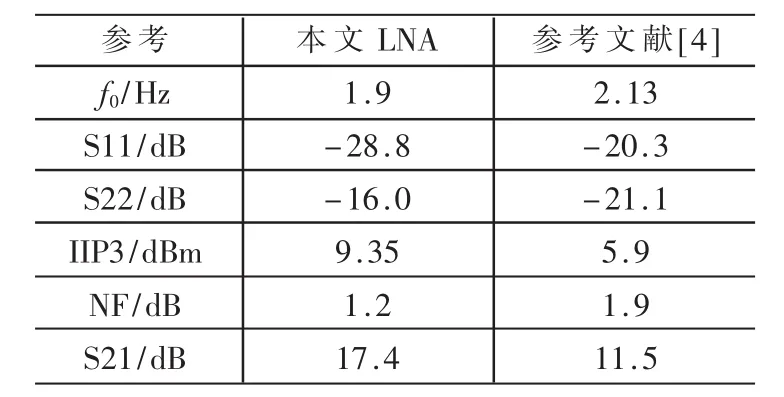

在设计过程中,电感采用INDQ模型,中心频率为1.9 GHz,可用于PHS和DECT无线接入系统,采用低电压0.9 V电源供电。同时为了验证栅源级电容C0对噪声性能的优化和M2晶体管线性补偿技术对线性度的改善,本文电路的仿真结果与参考文献[4]中LNA电路(图3)仿真参数进行对比,如表1所示。

表1 两种结构LNA仿真参数的对比分析

比较两种结构的仿真参数可以分析出,加了电容C0后,噪声性能得到优化,折叠共源共栅结构中,在输出级利用线性补偿技术,线性度改善效果比输入级利用该技术更好。因此,通过仿真结果和对比分析,验证了本电路理论分析的正确性和可行性,

通过在栅源极之间加入电容,实现了低功耗约束下的噪声系数最优化和输入阻抗的共轭匹配。另外,在输出级采用晶体管的线性补偿技术,极大地改善了线性度。最后,按照本文的设计方法,该电路工作在低电压0.9 V,中心频率1.9 GHz,在满足输入,输出阻抗匹配的条件下,增益17.4 dB,噪声系数1.2 dB,输入三阶交调点为9.35 dBm,功耗仅6.8 mW。

[1]SHEAFFERDK,LEETH.A 1.5 V 1.5 GHz CMOS low noise amplifier[J].IEEE Journal of Solid-State Circuits,1997,32(5):745-799.

[2]TOMMY K.K.Tsang,MOURAD N.El-Gamal.Gain ConTrollable very low voltage(<1 V)8-9 GHz Integrated CMOS LNA’s[C].IEEE Radio Frequency Integrated Circuits Symposium,2002:205-208.

[3]肖琚,李永明,王志华.低功耗CMOS低噪声放大器的设计[J].微电子学,2006,36(5):671-673.

[4]曹克,汪蕙.低电压低功耗CMOS射频低噪声放大器的设计,全国优秀博士学位论文[D],2005,6,87-120.

[5]钟晓伟,陈勇.射频集成低噪声放大器的分析与设计,全国优秀硕士学位论文[D],2008,5:50-60.