Prewitt图像边缘检测及边缘细化的FPGA实现*

2010-08-12谢昭莉白颖杰

谢昭莉,白颖杰

(重庆大学自动化学院,重庆400030)

图像边缘检测是图像分割、目标区域识别、区域形状提取等图像分析领域的基础,图像理解和分析的基础是边缘检测。边缘检测目前已成为机器视觉研究领域最活跃的课题之一,在工程应用中占有十分重要的地位。

边缘的检测常借助空域微分算子进行,通过微分模板与图像卷积完成。常见的边缘检测算子有Roberts、Laplacian、Sobel、Prewitt、Krisch等,其中Prewitt和Sobel算子是在实践中计算数字梯度时最常用的[1]。Prewitt算子比Sobel算子略简单,但实际应用中和Sobel算子的效果差别很小。从运算结构上看,图像卷积运算主要是乘加运算且具有很高的重复性和并行性,属于图像处理中最耗时的低层处理算法,其速度和性能直接影响到实时图像处理系统结果的好坏,也一直是传统实时图像处理系统的瓶颈。现场可编程逻辑门阵列FPGA具有高度的并行性和设计灵活性,因而基于FPGA用硬件实现对图像底层的处理,可以大大提高图像处理的速度,满足系统的实时性要求。

本文针对实际使用中的320×240×8 bit的灰度图像数据流,在FPGA芯片上利用3×3的Prewitt卷积模板检测图像的边缘,动态计算阈值,用非极大值抑制方法对边缘检测的结果进行细化处理,提高了边缘检测的精度,满足了实时性要求。

1 Prewitt图像边缘检测及边缘细化原理

1.1 图像卷积和Prewitt模板

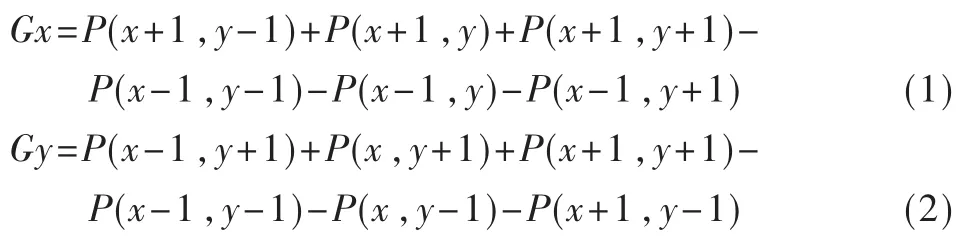

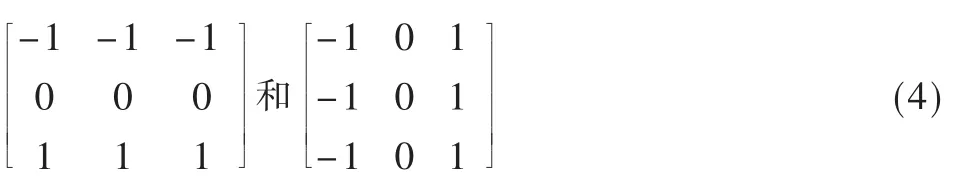

本文采用3×3大小的Prewitt算子。数字图像在位置(x,y)处点P(x,y)的水平差分算子Gx和垂直差分算子Gy为:

该点梯度的模近似为[1]:

上述公式采用模板表示:

可以看出,Prewitt算子是对图像灰度求平均后再求差分的,因此可以抑制噪声,但Prewitt算子检测出的边缘较宽。模板算子运算时采用模板卷积的方式,即把模板在图像上移动并在每点计算相应的梯度值。Prewitt算子使用2个有向算子(1个水平,1个垂直,一般称为掩模)。进行边缘检测时,用这2个核对图像中的每个点做卷积,其中一个核对垂直边缘响应最大,而另一个则对水平边缘响应最大。将它们的绝对值相加作为该点的输出,运算结果是一幅梯度幅度图像。

1.2 梯度幅度图像的非极大值抑制及自适应阈值

本文中原始图像的大小为320×240,经过3×3的模板卷积后,得到的梯度幅度图像G(x,y)大小为318×238。该图像增强了边缘信息,削弱了灰度变化缓慢的信息。但是,该图像产生的边缘较粗,因而传统的Prewitt边缘检测的定位精度较差。为了精确定位边缘,减小后续处理的数据量和复杂度,本文对梯度幅度图像G(x,y)进行了非极大值抑制和二值化处理。

非极大值抑制NMS(Non-Maximum Supression)是将当前像素的梯度值同沿其梯度方向相邻2个梯度值进行比较,如果其值比相邻的梯度值小,则此像素点被判断为非边缘点;如果其值比相邻的梯度值大,则此像素点被判断为边缘点[2]。

梯度幅度图像G(x,y)在(x,y)位置的非极大值抑制算法定义如下:

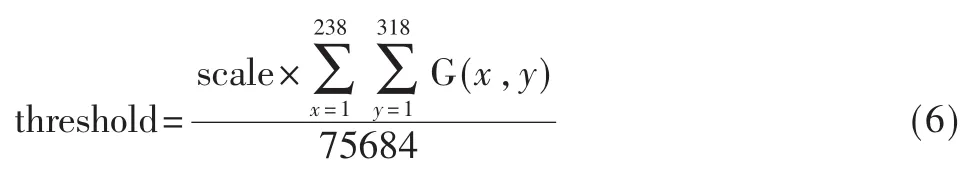

传统边缘检测需要人工给定阈值,适用性有限。本文根据噪声标准偏差估计RMS(estimate of noise)原理,用梯度幅度图像的平均值与增益系数的乘积作为自适应阈值:

这里,对Prewitt算子来说,scale取4。

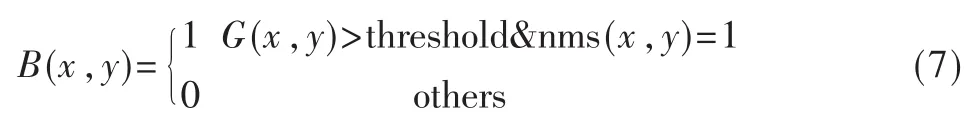

最终的梯度二值(边缘二值)图像B(x,y)为:对梯度幅度图像上的像素点G(x,y),若其梯度幅值大于阈值,并且该点是局部变化最大的点,即nms(x,y)为1,则该像素点为图像的边缘:

2 Prewitt图像边缘检测及边缘细化的FPGA实现

根据以上数学推导和分析得出,Prewitt边缘检测的核心运算是对每个像素点进行8邻域的模板卷积,以及对梯度幅度图像进行十字邻域的非极大值抑制运算。算法数据量大,但具有很高的并行性,一般通用处理器因其顺序执行的特点不能总是满足实时性要求[3]。而FPGA具有硬件执行处理、流水线任务处理技术以及并行信息处理的优点,适合用于图像处理领域,结合自身优点提高处理速度[4]。

2.1 系统结构设计

用FPGA实现实时Prewitt图像边缘检测及边缘细化的流程为:

(1)从数字摄像头获取8 bit灰度图像数据流,经过2个行缓冲器,流水生成3×3大小的窗口。

(2)根据算式1、2、3计算窗口中心像素的梯度幅值G(x,y),比较Gx和Gy的大小,输出带比较位的G(x,y);根据场信号VSYNC、行信号HREF、像素时钟信号PCLK确定G(x,y)有效区间G_valid和有效时钟G_clk。

(3)根据式(6)的改进式(见下文)计算阈值,该阈值每一场更新1次。

(4)将第2步生成的梯度幅值图像数据流,经过2个行缓冲器,流水生成十字窗口。

(5)根据式(5)、式(7)判断窗口中心像素是否为边缘,生成边缘二值图像B(x,y);根据G_clk、G_valid和VSYNC确定B(x,y)的有效区间B_valid和有效时钟B_clk。

(6)一场图像流水处理完毕,进行下一场图像的在线处理。

系统采用流水线作业方式,由原始图像的像素时钟PCLK驱动,将8 bit灰度图像数据流首先转换成梯度幅度图像数据流,进而转换成边缘二值图像数据流。由于经过了3×3窗口的图像卷积和十字窗口的非极大值抑制处理,图像大小由原始图像的320×240变为梯度幅度图像的318×238,进而变为边缘二值图像的316×236。系统的功能结构图如图1所示。

2.2 重点模块分析

(1)复位和时钟控制模块

本文采用的摄像头OV7620输出制式NTSC,1 s有60场图像(分为奇场和偶场),每场240行,每行640像素,原始像素时钟周期为75 ns。时钟控制模块将原始像素时钟二分频,像素时钟周期变为150 ns,故输入图像分辨率为320×240。本设计的处理周期以场为单位,除了阈值以外,所有寄存器都在场开始时清零。

在窗口生成过程中,每个像素时钟都会流水地生成窗口,但并不是每个都有效。对3×3窗口来说,由于采用8邻域的模板卷积,那些在图像边缘的像素没有“有效”的窗口,故只有那些行数大于2并且行内像素数大于2的点才有有效窗口。考虑到模板计算模块的执行时间,梯度幅度像素的时钟延迟“有效”像素时钟半个周期。边缘二值像素时钟产生的过程类似。

(2)FIFO和窗口生成模块

以3×3窗口为例。为了实现窗口并行结构,需要2个先进先出缓冲器(FIFO)和9个8 bit寄存器。可以使用FPGA内部逻辑资源构造FIFO,但是会占用大量的逻辑资源[5]。本文采用ACTEl提供的FIFO控制器和FPGA内部RAM实现。FIFO通过2个指针来控制数据的读写,写时钟和读时钟分离。本文读写时钟共用像素时钟,复位时读写地址相同,必须初始化读写地址,否则不能进行正常读写。为了实现行缓冲功能,写使能信号比读使能信号提前319个周期,这样写地址就比读地址大319。窗口生成模块结构图如图2所示。考虑到FIFO有一个时钟周期的延时,故在第321个像素时钟的上升沿时,第321个像素被锁入D33,第一个像素被锁入D23。

(3)模板计算及比较模块

该模块按照式(1)、式(2)、式(3)在生成的窗口中计算G(x,y)。为避免数据溢出,Gx、Gy为11 bit有符号数,绝对值按如下方法确定:如果最高位为1,则结果为原数取反加1,舍掉最高位(符号位);否则直接舍掉最高位(符号位)。由于后续模块要比较Gx和Gy的大小,显然保存Gx和Gy会浪费很多逻辑单元,故本文将结果G(x,y)扩展1 bit,令其最高位表示Gx和Gy的大小:如果Gx大于等于Gy,则该位为1;否则为0。

(4)阈值模块

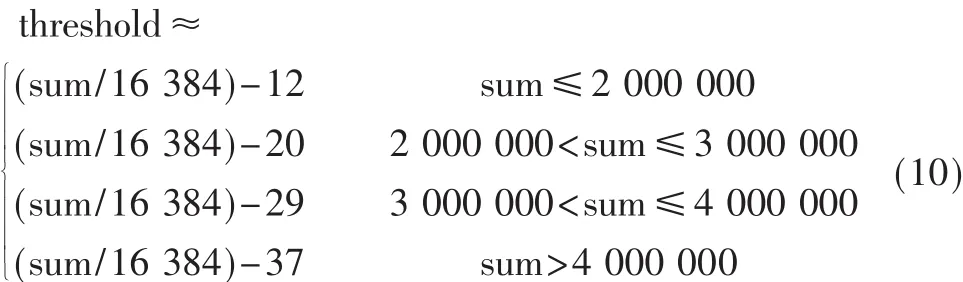

式(6)存在大数据除法,直接计算很慢而且不易实现,故本文采用构造分段函数的方法来逼近。首先将式(6)化简为:

其中累加和sum可以用累加器实现。经过大量实验数据分析,发现sum值大多集中在2 000 000到4 000 000区间内,考虑到可以方便高效地用移位来实现除数为2的倍数的除法,故阈值threshold用式(10)逼近。FPGA实现时,把累加器sum先右移14 bit,再减去补偿系数。

(5)非极大值抑制及二值化模块

该模块按照式(5)、式(7)判断对应像素是否为边缘,若是,则B(x,y)为1,否则为0。

3 实验结果分析

本文选用ACTEL公司FUSION系列60万门的AFS600,该款FPGA基于FLASH架构,拥有上电即行、单芯片、非易失性、低功耗等优点,具有4 Mbit用户可用的Flash Memory、1 kbit的FlashROM、108 kbit的RAM。

3.1 有效性验证

(1)控制FPGA按照320×240大小采集灰度图像并存储在片外SRAM中,通过串口将图像数据发送到计算机,用MATLAB还原图像,得到原始图像(图3(a))。该图像表明采集到的图像无随机噪声,可以不用滤波处理。为了直观地显示算法的处理过程,本文利用MATLAB模拟算法的中间过程。在MATLAB上得到基于Prewitt算子的梯度幅度图像(图3(b)),为了方便显示,将其最大值限制为255。在MATLAB上得到传统Prewitt边缘检测结果,如图3(c)所示,取阈值为130。该图像边缘较粗,定位精度不高。

(2)用MATLAB生成原始图像的数据文件,利用Verilog的系统任务“$readmemh”将原始图像数据写入测试程序(testbench),用modelsim进行布线后仿真,将结果B(x,y)导出,用MATLAB还原成图像(图3(d)),该图像即为本算法边缘检测结果。

3.2 实时性验证

加入VGA驱动模块,将边缘结果B(x,y)接入VGA实时显示。VGA显示大小与图像大小一致,为320×240。处理和显示的频率为60场/s。

实验结果表明,本系统产生单像素边缘,边缘细,定位精度高,较好地完成了边缘检测的任务,为轮廓跟踪、目标识别打下良好的基础。本系统用FPGA实现,消耗逻辑资源1 473个Core Cells,占片上资源的11%;处理的图像大小为320×240,处理速度达到60场/s,满足了实时性要求。

本文利用FPGA实现了基于Prewitt算子的边缘检测,并提出基于FPGA的自适应阈值算法和非极大值抑制方法对边缘检测的结果进行细化处理,克服了传统方法产生的边缘较粗的问题,提高了边缘检测的精度。在设计中使用FIFO控制器、流水线结构、分段函数逼近等方法提高了硬件处理速度,减少了资源占用,克服了软件方法速度不足的问题,满足了系统实时性要求。

[1]GONZALEZ R C.Digital image processing[M].北京:电子工业出版社,2004.

[2]韦海萍,赵保军,唐林波,等.Canny算法的改进及其硬件的实现[J].光学技术,2006,3(2):263-266.

[3]César Torres-Huitzil,Miguel Arias-Estrada.Real-time image processing with a compact FPGA-based systolic architecture[J].Real-Time Imaging,2004,10(3):177-187.

[4]胡亮,段发阶,丁克勤,等.基于FPGA图像处理技术在钢板表面缺陷检测系统中的应用[J].传感技术学报,2006,19(3):694-696,701.

[5]朱耀东.一种卷积滤波器大容量延迟线实现新方法[J].计算机工程,2006,32(15):215-217.