FPGA在直接数字波形合成宽带信号源中的应用

2010-08-10陈波,王铁

陈 波,王 铁

(海军装备研究院,北京100161)

0 引 言

线性调频(LFM)信号是宽带雷达常用的信号形式。目前,大带宽LFM信号的产生一般都采用数字方法产生基带信号(或中频信号),再经过适当的倍频、变频环节来得到最终信号的方案。波形存储直读法(DDWS)是产生数字基带信号的一种重要方法,其工作原理是将预先存储的经理想采样的数字波形直接进行数模变换(DAC)产生所需要的模拟信号。该方法可充分利用软件支持来加载波形数据,几乎可以产生任意波形(包括许多复杂波形及大数据量组合波形),还可通过对预先存储的波形数据进行预失真处理的方法来补偿信号产生本身的误差,甚至能补偿整个系统的误差,提高系统的性能。

应用波形直读存储法,基本前提是保证数据传输(包括计算机加载数据到存储器及存储器输出数据到DAC)准确稳定,这就要求系统有一个高速、可靠、稳定的控制单元。本文以单片高速FPGA 取代以往设计中使用的数字信号处理器(DSP)+FPGA作为宽带信号源控制核心,分析了FPGA在时钟管理、数据传输和电平转换中的作用,充分利用其高速、高集成度和可编程性,简化系统结构,保证信号产生的高速、灵活可控。

1 系统结构

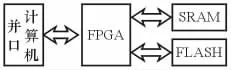

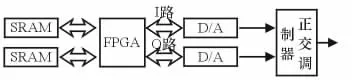

为了充分利用数字基带产生的信号带宽,信号源采用正交调制的方法产生中频信号,系统结构如图1 所示。

数字基带产生电路主要由高速D/A转换、大容量高速存储器(SRAM)、高速逻辑控制器、非易失性存储器(FLASH)和必要的调试接口构成。具体工作过程是:由外同步脉冲触发,根据要求的脉冲宽度输出SRAM中存储的I Q 两路数据,经高速DA转换产生I 、Q两路基带信号。

该系统有两种工作方式:脱离计算机工作(以下简称为脱机)和连接计算机工作(以下简称为联机)。联机时,波形数据从计算机并口加载到SRAM,经回读、校验无误后,在FPGA 的控制下,从SRAM中高速输出到DAC 产生基带信号,方便信号源自身的调试和标校。脱机时,波形数据从FLASH中加载到SRAM。FLASH中可存放一组波形数据,也可存储多组数据以方便应用。

图1 中频信号产生原理图

2 FPGA作用分析及实现

本文采用的FPGA 为Xilinx 公司的Virtex-II系列的XC2V500 ,该系列FPGA内核采用低电压工作,工作时钟可达800MHz ,能很好地完成系统的高速控制;芯片内嵌数字时钟管理模块(DCM)可以对输入时钟进行倍频、分频及移相等处理,能方便地提供与外围低速接口的时钟(高速和低速时钟);外围接口支持多达几十种的电平规范,其中包括LVTTL 和LVDS;具有数字阻抗控制(DCI )功能,能精确实现输入、输出数据线的阻抗匹配。本文中FPGA的主要功能如下。

2.1 数字时钟管理

FPGA内嵌功能强大的时钟管理工具——数字时钟管理模块(DCM),具体功能如下:

(1)去除时钟抖动skew歪斜。DCM通过内部DDL 来减少时钟分布引起的延时,以减少输入、输出端口间的抖动。本文通过外反馈的形式,将输出到DAC 处的时钟反馈给DCM,DDL 根据反馈自动调整延时,使得板上高速时钟可控。

(2)时钟频率变换。DCM可根据系统要求对输入时钟进行倍频、分频等变换。本文中信号源使用到的时钟有:信号源输入时钟(100MHz ),加载和回读数据使用的低速时钟(5MHz ),基带信号产生时SRAM 工作的高速时钟(150MHz ),DAC 工作的高速时钟(300MHz )。所有这些时钟都是通过DCM变频得到的。

(3)时钟相位移动。DCM 输出端口CLK90、CLK180 、CLK270 分别对输入时钟进行了1/4 、1/2 、3/4 个周期的固定延迟,此外,DCM 还可对其9个时钟输出进行动态调整——超前或滞后时钟周期1/256 的倍数,本文在调整SRAM高速数据流与DAC 时钟的匹配时就是通过调整DAC 时钟相位实现的。

2.2 计算机并口向存储器(SRAM和FLASH)中加载和回读数据

信号源联机工作时,波形数据由FPGA 控制从计算机并口加载到存储器,如图2 所示。

图2 联机时数据传输

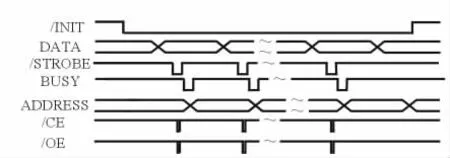

FPGA与计算机接口的通信采用并行接口协议(EPP),实现从计算机加载数据到存储器(SRAM和FLASH)和从存储器中将数据回读回计算机进行校验的功能。

每个计算机并口都可以使用2 种通信模式:应用于计算机到外设数据传送的八位兼容模式和应用于外设到计算机数据传送的四位组模式。兼容模式是主机向外设发送数据时采用的默认模式,而四位组模式容许任何并口从外设接收数据字节。

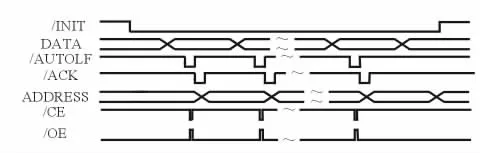

本文并口上有4 个信号被用作控制数据流的握手联络信号。握手联络可以实现多种功能。当外设做好接收数据的准备时,由BUSY 输出通知计算机,计算机的nStrobe 信号则负责通知外设,数据线上有一个待读数据字节;当计算机做好接收数据的准备时,由Autolf 输出通知外设,而外设则通过ACK信号通知计算机,数据线上有一个待读数据字节。计算机并口加载数据的时序如图3 所示,回读数据的时序如图4 所示。

图3 计算机并口加载数据时序

在数据加载和回读的过程中,FPGA作用如下:

1 生成存储器工作时钟。FPGA根据计算机并口发出的INIT 电平选择存储器工作时钟:INIT为低电平时,选择低速时钟(5MHz );反之,选择高速时钟(150MHz )。在加载/回读数据的过程中,计算机并口置INIT 信号为低电平,FPGA 控制内部DCM产生低速时钟。

图4 并口回读数据时序

(2)生成存储器地址。在FPGA 收到加载/回读数据指令后,启用计数器计数产生存储器地址。

(3)生成存储器控制信号。储器控制信号通过FPGA内部门电路产生,为避免时钟信号线上的毛刺而写入错误数据,片选写信号只在写入的单个时钟周期有效。

(4)数据管理。并口输出数据为8bit ,而存储器设置为16bit ,因此,在数据加载到存储器的过程中FPGA 要通过内部锁存器将8bit 数据合成为16bit ,而在回读过程中则将16bit 数据分成8bit输出给计算机并口。此外,为提高数据传输的可靠性,FPGA通过DCI 实现对数据线的阻抗匹配。

2.3 FLASH向SRAM中加载数据

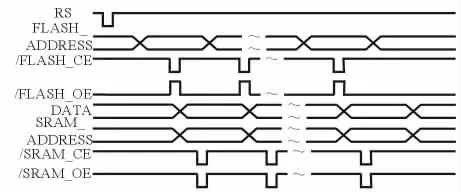

信号源脱机工作时,数据由FPGA 控制由FLASH加载到SRAM,如图5 所示。

图5 脱机时数据传输

信号源加电时,FPGA配置文件(.mcs 文件)自动由EEPROM(XC18V04 )加载,配置FPGA 内部结构。配置完毕时,波形数据由FLASH 加载到SRAM中。FPGA根据FLASH内部状态机WSM(Write State Machine )产生 FLASH 和SRAM 工作的地址、控制信号,控制数据流从FLASH加载到SRAM中。FLASH加载数据到SRAM的时序如图6 所示。数据加载到SRAM中后,可由2.2 介绍的方法将数据回读回计算机进行校验。

2.4 SRAM向DAC 高速输出数据

数据向存储器加载完毕后,FPGA 选择高速时钟作为SRAM的工作时钟。在触发脉冲到来时,FPGA根据所定脉冲宽度控制内部计数器计数,产生SRAM的高速地址,控制数据从SRAM中输出,经DAC 转换后形成基带信号,如图7 所示。

图6 FLASH加载数据到SRAM时序

图7 基带信号产生

这个过程中存在2 个难点:

(1)存储器工作速率低。系统DAC 时钟工作在300MHz ,要求输入数据更新速率也为300MHz ,而现有的晶体管-晶体管逻辑(TTL)电平大容量存储器件数据存取速度远达不到此要求。

(2)电平转换和数据流同步。SRAM信号电平为低电压TTL,要转化为DAC 工作的低电压差分信号(LVDS)电平,以及300MHz 高速数据流与DAC 工作时钟要保持同步是系统的又一难点。

为解决上述问题,系统数据存储部分采用并行结构,在FPGA 内数据输出模块中配置选择开关,将2 路并行数据整合成单路2 倍速率的数据流输出。该方案降低了数据存储器的存取速率,使大数据量高速存取成为可能,且易于系统升级。FPGA配置有不同的I/O标准,如LVDS、低电压伪发射极耦合逻辑等,这就实现了不同电平的转换。DCM可以方便地调整SRAM和DAC 时钟的相位,保证DAC 输入的数据和工作时钟同步,使得最终输出波形稳定准确。

3 结束语

FPGA作为宽带信号源的控制核心,充分发挥了高速可编程器件的优势,使信号源外围接口简单通用,具有模块化的特点,不同波段、不同带宽的系统均能直接使用,而且易于扩展。信号源实物如图8 所示。

图8 FPGA为控制核心的宽带信号源模块

经测试,该信号源主要指标如下:

(1)可产生带宽200MHz 以内、时宽800 μs 以内的任意LFM信号;

(2)线性调频相位失真<±1°;

(3)脉冲压缩性能:采用Hamming 加权后,脉冲压缩峰值旁瓣比大于35dB,主瓣展宽与理论值相当。

本文利用FPGA 实现简单、控制灵活、接口通用等特点,将其作为控制核心设计完成直接数字波形合成宽带信号源。经测试,该信号源成功实现了高指标宽带线性调频信号的产生,大幅简化了结构组成,提高了战术性能及通用性。

[1]李伯成.微机应用系统设计[M].西安:西安电子科技大学出版社,1996.

[2]费元春.宽带雷达信号产生技术[M].北京:国防工业出版社,2002.