基于DSP的铁路信号识别技术

2010-08-07黄雪程

黄雪程,王 焱,刘 春

(1.北京大成通号轨道交通设备有限公司,北京100044;2.北京邮电大学信息与通信工程学院,北京100088)

铁路信号识别技术应用于列车自动防护系统中,对ATP(列车超速防护系统)信号好进行解调、识别,ATP控制以识别结果提供对列车的防护,控制列车运行的追踪间隔与运行速度,该技术还具备检测自身工作状态,判定故障的功能。伴随高速列车运输系统的发展,铁路运输的提速、车载的需求,基于分立元器件和模拟信号处理技术的传统铁路信号设备越来越满足不了铁路系统安全性和实时性的要求。研究开发出基于计算机技术和数字信号处理技术的铁路信号设备已成为铁路信号的发展趋势。

本文提出基于DSP技术的铁路信号识别系统,以数字信号处理芯片TMS320C6713为核心,能够完成铁路信号接收、识别、记录、统计分析和显示多个功能,在重庆单轨交通系统中投入实验测试,测试结果表明该系统具有较高的实时性和可靠性。

1 信号识别系统的整体结构

技术包括铁路信号接收,信号处理和信号统计分析3个部分。信号接收:由接收天线和信号放大器组成,用于实时接收现场信号;信号处理:包括A/D转换模块和解码模块,接收信号先经过A/D芯片(芯片型号:TLV320AIC23B)进行模数信号转换,然后运用数字信号处理算法解调接收的移频信号;信号统计分析:接收信号处理部分输出的解调信息,在PC机上利用相关软件进行统计分析。

整体工作流程如图1:接收天线实时接收铁路信号,由信号放大器放大通过I/O接口送入DSP开发板,先经通过模数信号完成转换,再由TMS320c6713芯片完成解码任务后,一方面完成上灯操作,另一方面将解码信息送入上位PC机,PC机上统计分析软件完成信息的记录、统计分析和结果显示,根据解码信息,获得列车信号设备的工作状态对列车进行控制。

图1 铁路信号识别系统整体结构

2 硬件设计

以32 bit浮点处理器TMS320C6713为数据处理核心,采用外围电路设计。硬件结构框图如图2。

图2 铁路信号识别系统硬件结构框图

2.1 数据采集模块

考虑到本系统将投入某城市跨座式单轨交通系统中使用,一方面某城市单轨交通中铁路信号最大载频为21 kHz,根据奈奎斯特定律可知系统采样频率必须大于或等于42 kHz;另一方面铁路信号富含丰富的低频信息,频率间隔极小,系统要保证低频信号的精确识别必须采用精度很高的芯片。所以采用音频CODEC芯片TLV320AIC23B,TLV320AIC23B采样带宽48 kHz、最大采样速率96 kHz 。可以在 8 kHz ~ 96 kHz 采样率范围内提供 16 bit、20 bit、24 bit和 32 bit采样,音频口耐压范围为0 V~2V。其所有数据性能均满足某城市单轨交通铁路信号动态范围的要求。

音频芯片TLV320AIC23B是通过I2C总线接收配置信息完成内部寄存器配置,通过I2S总线协议完成与DSP的数据交换。高精度、高采样率的采样芯片提高了系统信号识别的精度。另外采用高性能的音频芯片TLV320AIC23B,能够减小数据采集时造成的时延,有效地提高系统的实时处理能力。

2.2 信号识别模块

该模块由DSP芯片协同SDRAM完成。根据铁路信号识别系统信号处理任务及实时性的要求,信号处理芯片选用的高性能32 bit浮点DSP 处理器TMS320C6713,其适用于专业音频信号处理,主频可达到300 MHz,处理速度高达2 400 MIPS/1 800MFLOPS。TMS320C6713 采用了2 级Cache结构,片上共有 264 K×8 bit存储器 。TMS320C6713有32 bit的EMIF 地址总线,有4 个空间,每个空间均可与SDRAM 、SBSRAM 和异步外设实现无缝接口。通过合理的EMIF接口设计,可最大限度的发挥TMS320C6713强大的定点/浮点数据运算性能,提高硬件平台的实时处理能力。

由于采样数据量巨大,片上存储器存储空间不能满足要求,所以信号采集电路将采集到的数据存放在64 MBSDRAM内,通过EMIF与C6713完成数据交换。另外,为实现系统加电后能够自动加载应用程序,进入工作状态,程序代码存放在512 KbFLASH内,在系统加电后由Bootloader 加载到TMS320C6713片内RAM中运行。

2.3 UART通信电路设计

UART (Universal Asynchronous Receiver/Transmitter,通用异步接收/发送装置) 通道实现DSP与上位机之间的通信,为了实现多种电平接口,系统采用TL16C752B作为通用异步收发器。芯片包含二路相互独立的异步收发器,接收和发送各带64 byte的FIFO,最高传输速率可达 1.5 Mbps,采用MAX3160多协议收发器,使得异步串口接口电平可配置为RS232/RS422/RS485 多种接口电平标准。TL16C752B与C6713的EMIF接口,配置在C6713的CE[3] 空间中。

3 软件设计

软件根据功能要求和编程平台的不同可分为DSP程序设计、DSP与上位机通信设计和PC上位机软件设计3个部分。

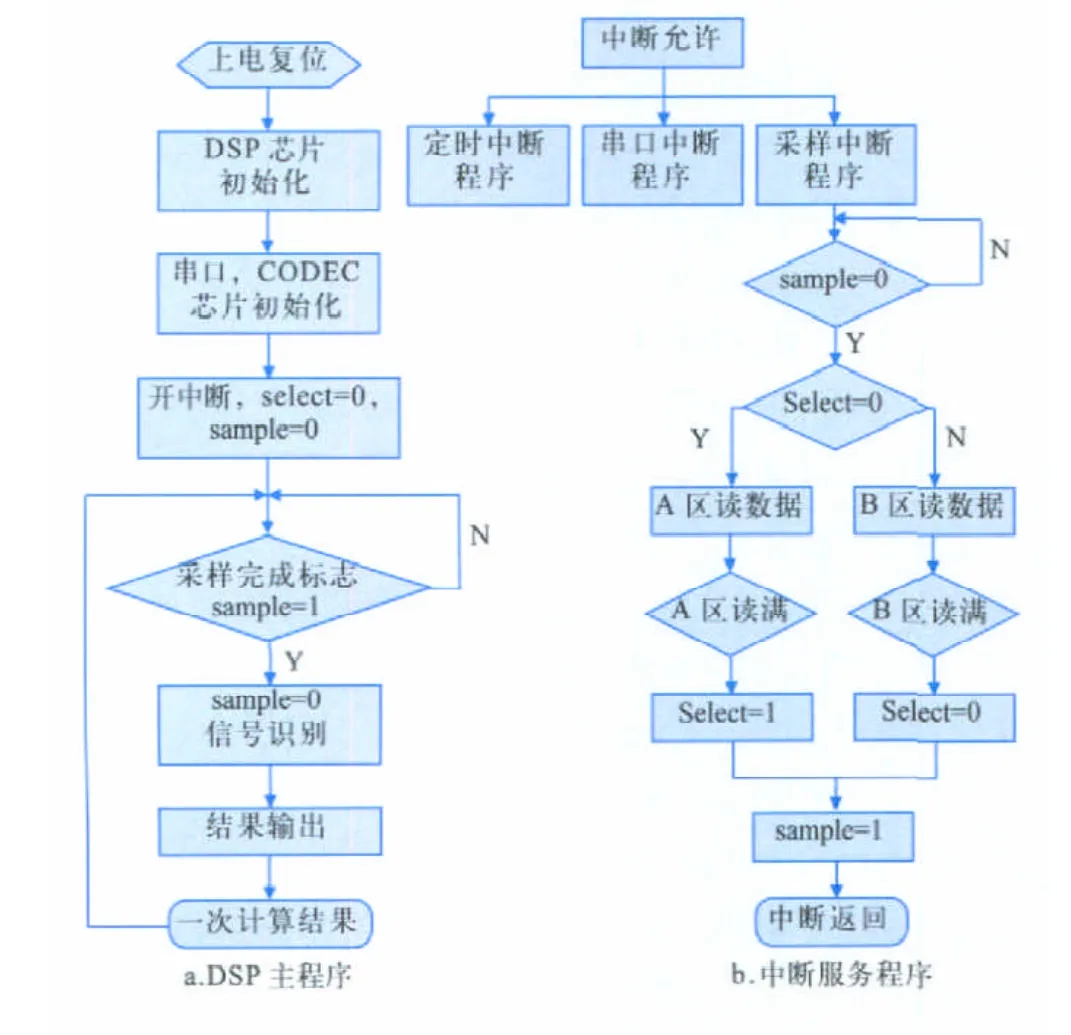

图3 铁路信号识别技术软件流程图

(1)DSP程序设计。系统主程序如图3,包括信号处理芯片TMS320C6713、CODEC及串口芯片等初始化程序设计、信号识别算法设计和中断服务程序设计。

a.DSP芯片初始化程序。完成内置定时器设置、CPU与外部存储器接口EMIF设置和中断向量设置。串口、CODEC芯片初始化程序完成内部控制寄存器设置。

b. 信号识别算法。采用ZFFT算法与频率能量重心校正技术相结合,能够精确识别出频率间隔极小的低频信号,保证铁路信号的精确识别。

c. 中断服务程序。由定时中断程序,串口中断程序和采样中断程序组成。采样中断程序流程如图3b.,图中Sample为一次采样完成标志,Select为采样片选信号。将采样信号存储空间分为A和B两个区域,每个区域能存储一次信号识别所需采样数据,A区采样完成则B区开始采样,任一区采样完成则将采样完成标志Sample置为1,同时主程序开始信号识别计算工作。采样中断程序的分区设计使系统在响应采样中断程序的同时能够完成信号计算的工作,降低了系统完成一次信号识别所需时间,从而保证系统的高实时性。

(2)DSP与PC上位机及下位机信号显示灯通信设计。DSP与上位机之间通信采用RS232串口标准,DSP通过RS232控制寄存器来初始化串口:设置波特率,使能串口接收与发送等。系统通过定时响应串口中断程序完成DSP与上位机之间的数据传输。DSP与下位机信号显示灯之间通过芯片内置外设GPIO连接,信号灯实时显示系统工作状态。

(3)PC上位机软件设计。该软件由C++语言编写完成,具有将解调信号记录存储、统计分析和实时显示的功能。

4 结术语

铁路识别系统在重庆跨座式单轨轨道交通系统已投入实验测试阶段,测试结果表明基于DSP技术的铁路信号识别系统具有运算速度快,精度高,实时性好和稳定性强等特点。

[1] 李方慧,王飞,何佩琨. TMS320C6000系列DSPs原理与应用[M] .北京:电子工业出版社,2005.

[2] 郎宗琰,郜成缙. 现代铁路信号技术[M] . 成都:西南交通大学出版社,2000.

[3] TLV320AIC23B Data Manual[S] . Texas Instruments Incorporated, 2002.

[4] TL16C752B Data Manual[S] . Texas Instruments Incorporated,2002.

[5] TMS320C6000 CPU and Instruction Set Reference Guide[S] .Texas Instruments Incorporated, 2000.