AT91M40800与CAN总线的接口设计与软件编程

2010-07-25王小进李世学

王小进 李世学

(中国船舶重工集团公司第712研究所, 武汉430064)

1 引言

随着信息技术的发展,变电站自动化系统内部各设备间通讯信息量逐渐增大,传统的串口传输已成为数据传输的瓶颈。文中的接口设计结合ARM芯片与CAN控制器具有高实时性、高传输速率、高可靠性等特点,完全适合于变电站上设备间的大数据量实时传输。

2 CAN控制器SJA1000介绍

SJA1000[1]是Philips生产的独立CAN总线控制器,它是早期的 PCA82C200的替代产品。它与 PCA82C200在管脚、电气特性上完全兼容,不仅有和 PCA82C200一样的基本 CAN(BasicCAN)工作模式,而且新增加 CAN(PeliCAN)工作模式,这种模式支持具有很多特性的 CAN2.0B协议。经过简单连接和正确设置的SJA1000,能自动完成CAN总线物理层和数据链路成的所有功能,对于 ARM 芯片AT91M40800来说,只要把它堪称一个基本的I/O设备即可,使用非常简单、方便。SJA1000的主要特性如下[2]:

(1)扩展的接收缓冲器(64字节,先进先出FIFO);

(2)和CAN2.0B协议兼容;

(3)同时支持11位和29位识别码;

(4)位速率最高可达1Mbits/s;

(5)支持多种微处理器接口;

(6)可编程的CAN输出驱动器配置。

3 AT91M40800简介[3]

采用RISC架构的ARM微处理器一般具有如下特点:

(1)体积小、低功耗、低成本、高性能;

(2)支持Thumb(16位)/ARM(32位)双指令集,能很好的兼容8位/16位器件;

(3)大量使用寄存器,指令执行速度更快;

(4)大多数数据操作都在寄存器中完成;

(5)寻址方式灵活简单,执行效率高;

(6)指令长度固定。

AT9140800是美国ATMEL公司推出的AT91系列微控制器中的成员,它基于ARM7TDMI核,包含8KB SRAM、外部总线接口EBI和一些外围部件。外围部件包括定时器、USART和中断控制器。AT91M40800是用于系统主控制器的理想通用微控制器,其内核 ARM7TDMI处理器的性能使得可由软件实现DMA、SPI和ISO7816接口等附加的外围功能。

4 接口电路硬件设计[4]

CAN属于现场总线的范畴,是一种有效支持分布式控制或实时控制的串行通信网络,其协议是建立在国际标准组织的开放系统互连模型基础上的,其模型结构只有三层,只取OSI底层的物理层、数据链路层和顶层的应用层。其信号传输介质为双绞线。通信速率最高可达1 Mbps/40 m,直接传输距离最远可达10 km/5 bps。可挂接设备最多可达110个。

CAN通信模块的硬件电路主要包括:CAN通信控制器与微处理器之间,以及 CAN总线收发器与物理总线之间的接口电路。运用AT91M40800和SJA1000设计的CAN总线节点接口电路如图1所示。

用Philips独立CAN控制器SJA1000作为通信控制器,使用Philips的82C251作为CAN控制器接口芯片,为了增强 CAN总线节点的抗干扰能力,SJA1000的TX0和RX0通过采用高速光耦 6N137实现收发器与控制器之间的电气隔离,满足在最高速率1Mb/s下的电气响应。

图1 CAN通信接口电路

5 ARM软件编程

基于AT91M40800和SJA1000设计的CAN总线节点的软件设计主要包括三大部分:SJA1000初始化、AT91M40800外部中断设置、报文发送与接收。结合图1接口电路图来从以下三个方面对ARM软件编程进行简要描述:

5.1 SJA1000的初始化

SJA1000具有两种工作模式,即 BasicCAN模式和PeliCAN模式。在BasicCAN模式下支持CAN2.0A协议,在PeliCAN模式下支持CAN2.0B协议,功能更加强大。本节点是将SJA1000设置成在PeliCAN模式下工作。SJA1000的初始化只有在复位模式下才可以进行,具体的初始化主要注意以下几个方面:

① 设置为复位模式:向MOD模式寄存器中写入0x09选择单滤波验收,进入复位模式;

② 设置工作模式和时钟分频:向时钟分频寄存器CDR中写入0x88选择PeliCAN模式,关闭时钟输出CLKOUT,跳过输入比较器;

③ 设置中断使能:开放发送中断超载中断和错误警告中断;

④ 定义验收代码和屏蔽代码;

⑤ 设置通讯波特率;

⑥ 设置为正常操作模式:向MOD模式寄存器中写入0x08,将SJA1000设为单滤波的总厂操作模式,这样SJA1000就可以开始正常工作了。

5.2 AT91M40800外部中断设置

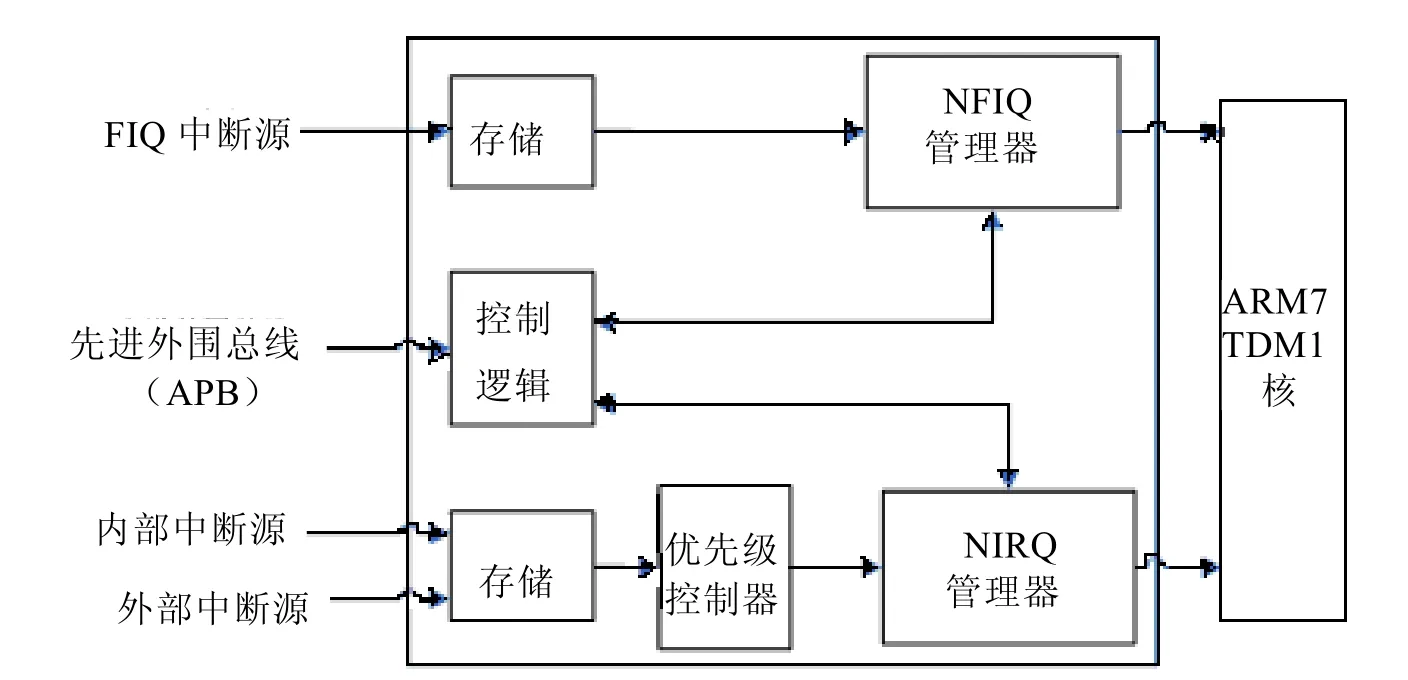

AT91系列微控制器内部的有一个8优先级、可单独屏蔽的向量中断控制器,称为先进中断控制器 AIC(Advanced Interrupt Controller)。AIC可以将中断处理的程序及时间开销大大降低。中断控制器方框图如图2所示。

图2 中断控制器方框图

AIC中断源如表1所示,从图2可以看到,中断控制器与ARM7TDMI的NFIQ(fast interrupt request)和 NIFQ(standard interrupt request)相连。NFIQ只能由快速请求引脚 FIQ产生,而 NIRQ则可以由片内外围及外部中断请求线 IRQ0~IRQ2产生。8优先级中断编码器允许用户定义不同NIRQ中断源的优先级。

内部中断源可编程为电平敏感中断或是边沿触发中断。外部中断则可编程为上升沿、下降沿触发和高电平、低电平中断敏感。

节点电路中把SJA1000作为AT91M40800芯片的一个I/O设备来看待,设定IRQ2为优先级为2的中断源,在初始化完成后进入中断服务程序,中断服务完成后,程序继续执行原来的代码。

表1 AIC中断源

外部中断设置步骤:

首先假设:第一、AIC已经正确编程,AIC_SVR也已经写入正确的中断服务程序的入口地址,且中断已经使能;第二、地址0x18(IRQ中断向量地址)指令为

LDR PC,[PC,# -&F20]

当NIRQ到来,且CPSR的位I为0时,步骤如下:

① CPSR被拷贝到SPSR_irq,当前程序计数器PC的值被保存到IRQ链接寄存器(R14_irq),同时PC(R15)自身被赋予新值0x18;

② ARM内核进入IRQ模式;

③ 当指令 LDR PC,[PC,# -&F20]得到执行后,PC就被赋予了AIC_IVR的内容;

④ 上一步骤将程序跳转到了对应的中断服务程序;

⑤ 清零CPSR的位I就可以使其它中断不被屏蔽,再施加的NIRQ可以被内核接受;

⑥ 接着,中断例程可以保存相应的寄存器以保护现场;

⑦ 在退出中断之前首先要置位 CPSR的位I,以便屏蔽其它中断,保证多个中断有序地完成;

⑧ 在结束中断之前还必须执行一次对AIC_EOICR的写操作,向AIC表明中断已经完成;

⑨ SPSR(SPSR_irq)被恢复。

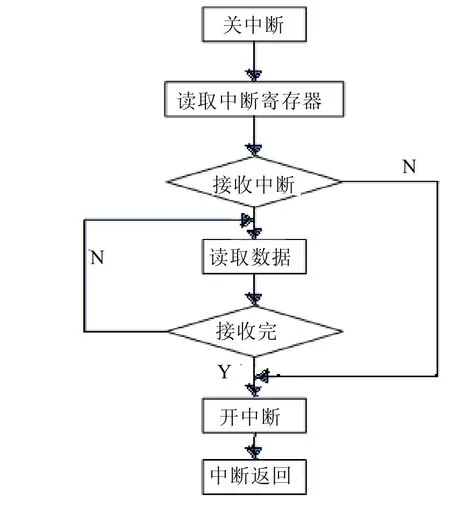

5.3 报文发送与接收[5]

SJA1000接受到匹配的数据帧后向控制器发出中断请求,接收数据只需从接收缓冲区读取数据,将其放在发送缓冲区中。AT91M40800与SJA1000构成的 CAN节点通信是一个半双工通信模式,报文发送的前提是报文接收到的字节符合协议格式,在确定接收报文正确后给出协议响应来完成报文的发送。节点接收和发送程序流程图如图3和图4所示。

图3 接收流程图

图4 发送流程图

6 结束语

本设计可以作为 CAN总线节点的一个模块应用于变电站自动化系统,可确保实现变电站通信的实时性、可靠性及高速率传输性,可以大大促进变电站综合自动化的进程。

[1] Philips Semiconductors.SJA1000 Stand_alone CAN controller[S].2000.

[2] 邬宽明. CAN总线原理和应用系统设计[M]. 北京:航空航天大学出版社,2000.

[3] 马忠梅等. AT91系列ARM核微控制器结构与开发[M]. 北京:北京航空航天大学出版社,2003.

[4] 杨红科, 雷立英. 基于SJA1000的CAN总线接口电路的设计[J]. 南京工业职业技术学院学报,2006(6):54-56.

[5] 黎新亮, 关沫, 马君璞. 基于SJA1000的CAN总线通讯模块的设计.[J] 沈阳工业大学学报,2004(1):99-102.