基于FPGA的双口RAM实现及应用

2010-07-13秦鸿刚刘京科

秦鸿刚,刘京科,吴 迪

(煤炭科学研究总院 西安研究院,陕西 西安 710054)

随着电子技术的飞速发展,大量的高速数据采集和在线测试对现代工业测控系统和仪器仪表的功能和性能提更高要求。CPU并行工作(双单片机系统)方式得到广泛应用。为了使2个单片机能够快速有效交换信息,充分利用系统资源,采用双口RAM实现存储器共享是目前较为流行的方法。

大容量、高速FPGA器件具有集成度高、体积小、灵活可重配置、实验风险小等优点,在复杂数字系统中得到越来越广泛的应用[1]。数字电路设计采用1片FPGA器件、存储设备和一些电气接口匹配电路的解决方案已成为主流选择方案。用FPGA来实现双口RAM的功能可以很好地解决并行性和速度问题,而且其灵活的可配置特性使得基于FPGA的双口RAM易于进行修改、测试及系统升级,可降低设计成本,缩短开发周期。

1 双口RAM简介

双口RAM是在1个SRAM存储器上具有两套完全独立的数据线、地址线和读写控制线,并允许两个独立的系统同时对其进行随机性访问的存储器,即共享式多端口存储器。双口RAM最大的特点是存储数据共享。1个存储器配备两套独立的地址、数据和控制线,允许两个独立的CPU或控制器同时异步地访问存储单元。因为数据共享,则必须具有访问仲裁控制。内部仲裁逻辑控制提供以下功能:对同一地址单元访问的时序控制;存储单元数据块的访问权限分配;信令交换逻辑(例如中断信号)等。双口RAM可用于提高RAM的吞吐率,适用于实时数据缓存。

CY7C006A[2]是Cypress公司生产的16 kb×8高速双口静态RAM,存取速度小于20 ns。该器件具有真正的双端口,可以同时进行数据存取,两个端口具有独立的控制信号线、地址线和数据线,另外通过主/从选择可以方便地扩存储容量和数据宽度。通过器件的信号量标志器,左、右两端口可以实现器件资源共享。

2 双口RAM在FPGA中的实现

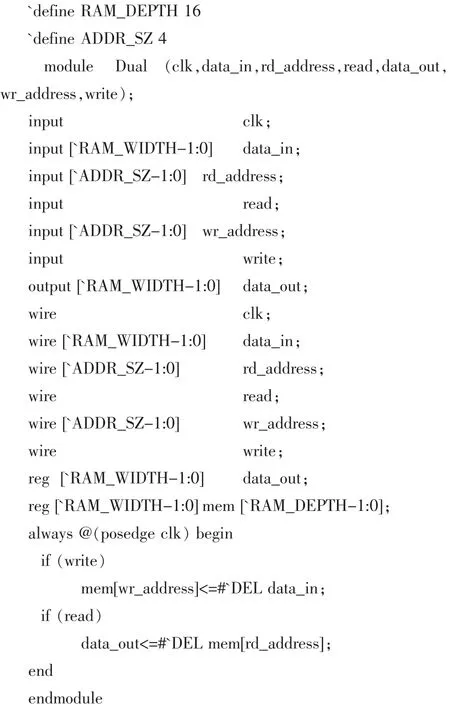

本设计采用自顶而下的设计思想。选用Xilinx公司的Spartan-6 FPGA器件,基于低功耗 45 nm、9-金属铜层、双栅极氧化层工艺技术,提供高级功耗管理技术,150 000个逻辑单元,集成式 PCI Express模块,高级存储器支持,250 MHz DSP slice和3.125 Gb/s低功耗收发器。通过Verilog HDL语言对双口RAM功能的描述就能在一片FPGA器件内实现8位16字节的双口RAM,并进行读写操作控制[3-4]。双口RAM读写操作控制Verilog HDL代码如下:

图1是双口RAM的Verilog HDL代码在Xilinx ISE中综合后的寄存器传输级电路图。

图1 寄存器传输级电路

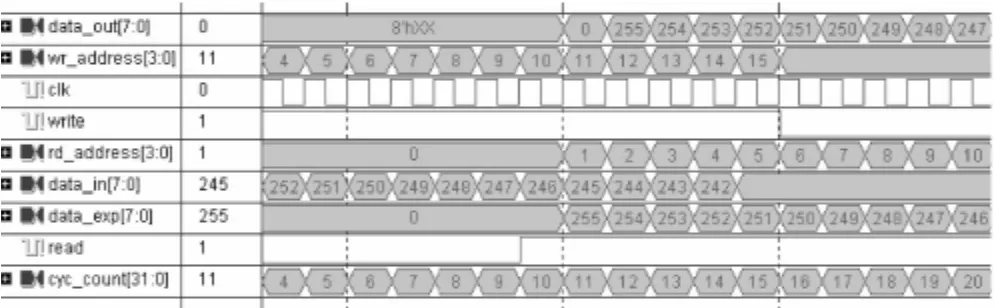

功能仿真的是Xilinx公司已经建立自己的编译库的Modelsim XEⅢ6.2c软件,仿真结果如图2所示,满足设计要求。

图2 双口RAM功能仿真结果

经Xilinx ISE软件综合实现设计,生成可下载的比特流,将其下载到FPGA中,实现双口RAM的功能。FPGA器件内部具有丰富的资源,可以在实现双口RAM基本功能的基础上。满足系统设计的其他需求,且灵活可配置。

3 基于FPGA的双口RAM应用

双口RAM在数字系统中应用广泛[3-7]。高速数据采集系统中,一般的数据传输系统在大数据量情况下会造成数据堵塞现象。在一些实时控制场合,实时算法经常需要由几个DSP串行或并行工作以提高系统的运行速度和实时性。以双口RAM构成的数据接口可以在两个处理器之间进行高速可靠的信息传输。此外,双口RAM可以应用在智能总线适配卡、网络适配卡中作为高速数据传输的接口。在许多宽带信号处理领域(如无线通信、多媒体系统、卫星通信、雷达系统等),FPGA技术已代替DSP实现许多前端的数字信号处理算法。用FPGA来实现数字信号处理能很好地解决并行性和速度问题,而且其灵活的可配置特性,使得FPGA构成的数字信号处理系统易于修改、测试及系统升级,降低设计成本,缩短开发周期。任何一种自动控制系统都离不开数据采集系统[8-10],数据采集系统的质量直接影响整体系统的工作性能。数据采集系统高速、实时发展趋势,对数据的传输和控制速度提出较高要求,而采用双口RAM可有效提高速度,解决速度匹配问题。

设计1块数据采集系统板,用FPGA实现双口RAM功能,并且控制A/D采样与转换,以及数据写入双口RAM。利用单片机控制双口RAM的存取,构成一个独立的数据采集系统,并可以通过串行接口把数据发送给PC机。图3为其系统结构框图。

图3 数据采集系统结构框图

首先,时钟产生启动信号,FPGA向采样开关发出选通信号,选定模拟开关采样,第0路模拟量进入,经A/D转换后变为8位数字量并存储于双口RAM中,ADC0809反馈给FPGA内控制电路并告知转换完毕,FPGA内控制电路再选通第1路模拟量进入,重复上述过程。经过0.1 ms后,时钟又产生一个脉冲启动信号。FPGA又重新从第0路模拟量选通。

在时钟脉冲信号0.1 ms过程中,FPGA顺序通过0~7路模拟开关,在每次选通时须判断是否为第7路模拟量,若是则FPGA不再响应A/D反馈信号,而是等待0.1 ms的时钟脉冲信号到达再重新开始工作。单片机用于与外部PC机通信,PC机查询是否在双端口RAM中有新数据,并经接口电路读入数据。其中双口RAM具有2组独立的数据、地址和控制总线,可对任何一个端口进行独立的操作。若未采用双口RAM,FPGA采取中断方式对CPU传输数据时,CPU就会停止当前工作而去处理外部请求,当处理完外部事件后再回到原来被中止处,继续原来的工作,这样会影响CPU的速度。因此引入双口RAM存储FPGA传送来的数据,然后CPU再从双口RAM中读数,从而提高效率。本数据采集系统采用基于FP-GA双口RAM、单片机等实现数据运行处理和控制功能,使系统的通信和处理能力大大加强,保证了系统的实时性,可以灵活地通过多种方式控制数据读写。

4 结束语

本文充分利用FPGA内部丰富的硬件资源和Verilog HDL语言的灵活性,在FPGA内实现了双口RAM的基本功能,并通过设计一块数据采集板介绍基于FPGA技术的双口RAM的应用,该系统减小了设计电路的复杂性,增强了设计的灵活性和资源的可配置性。整个系统分工明确,构成合理,具有一定的应用价值。

[1]薛小刚,葛毅敏.Xilinx ISE 9.x FPGA/CPLD设计指南[M].北京:人民邮电出版社,2007.

[2]Cypress公司.CY7C006A/CY7C007A/CY7C016A/CY7C017 ADatasheet[EB/OL].2009.http://download.cypress.com.edgesuite.net/design_resources/datasheets/contents/cy7c006a_8.pdf?key=1249349381384.

[3]王 冠,黄 熙,王 鹰.Verilog HDL与数字电路设计[M].北京:机械工业出版社,2006.

[4]雷晓平,罗海天.FPGA在实时嵌入式微机数据采集中的应用[J].计算机应用研究,2004(6):200-201.

[5]季 强,刘利强.双口RAM在数据采集系统中的应用[J].应用科技,2004(5):22-24.

[6]钱瑞霞.基于双口RAM的智能数据采集卡设计[J].中国仪器仪表,2001(3):24-26.

[7]陈德明,熊列彬.双口RAM在自动化系统中的应用[J].电子设计工程,2005,13(4):20-23.

[8]方言军,孙 建.智能仪器技术及其应用[M].北京:化学工业出版社,2007.

[9]胡宏平,胡 兵.基于FPGA的双口RAM在信号采集中的应用[J].微计算机信息,2007(23):223-225.

[10]康华光.电子技术基础—数字部分[M].3版.北京:高等教育出版社,1999.