基于FPGA分布式算法的滤波器设计

2010-07-02田森平

桂 婧 田森平

(华南理工大学自动化学院)

基于FPGA分布式算法的滤波器设计

桂 婧 田森平

(华南理工大学自动化学院)

研究基于分布式算法的数字滤波器设计方法,介绍了能高效实现固定常数乘法的分布式算法原理,并将分布式算法应用于FIR低通滤波器设计,实现了16阶滤波器的设计和调试.采用了EP3C25F324C8来完成滤波器的设计,其中采用串行加法器将数据进行预相加,将16阶降为8阶,降低了资源占用率并提升了处理速度。使用Matlab编程8阶固定常数系数对应256个值的查找表直接导入到FPGA的ROM中,设计方法具有兼容性,可设计更高阶次的滤波器。通过功能仿真证明,方法可行高效。

FIR滤波器; FPGA;分布式算法;查找表

1 引言

在信号处理过程中,如对信号的过滤、检测、预测等,都需要用到滤波器。模拟滤波器是以电容,电阻,预算放大器等模拟元件为基础构成的具有选频作用的电路。但模拟元件所固有的一些缺陷,如元件对温度变化、老化的敏感、现代压微米设计带来的噪声等,取而代之的是采用数字方式实现的滤波器[1]。随着数字信号处理技术的不断发展,采样速率也不断提高。DSP(数字信号处理)芯片和集成滤波芯片由于运算速度、阶数和字长的限制已经不具备实现FIR(有限冲激响应数字滤波器)滤波器的能力[2]。而FPGA(现场可编程门阵列集成电路)在对数据进行实时处理方面具有巨大的优势同时兼具一定的灵活性,因此非常适合用来实现数字滤波器的设计。在基于FPGA的数字滤波器的设计中,分布式算法是常用的算法之一,然而当滤波器阶数高于4阶时,分布式算法中的LUT(查找表)通常采用拆分为多个4输入查找表的方法来实现[5],对于16阶以下的查找表此种方法并非高效。

本文将介绍基于Altera公司的EP3C25F324C8NES系列FPGA的FIR滤波器设计,在对分布式算法理论研究的基础上,采用串行加法器将数据进行预相加,将16阶降为8阶,降低了资源占用率并提升了处理速度。使用Matlab编程8阶固定常数系数对应256个值的查找表直接导入到FPGA的ROM中,避免使用拆分查找表的方式,设计方法具有兼容性,可设计更高阶次的滤波器,并完成了滤波器的结构设计和软件编程和功能仿真。

2 算法描述

2.1 FIR的基本概念

数字滤波器是数字信号处理中使用最广泛的一种方法,实现方法主要有IIR(无限冲激响应数字滤波器)和FIR(有限冲激响应数字滤波器)两种[3],其中IIR滤波器需要执行无限数量卷积,能得到较好的幅度特性,其相位特性是非线性的;而FIR滤波器值由有限个采样值组成,具有严格的线性相位特性。由于在数据通讯、语音信号处理、图像处理等传输过程中不能有明显的相位失真,而FIR滤波器在满足一定对称条件下可以实现IIR滤波器难以实现的线性相位,因而得到广泛应用。

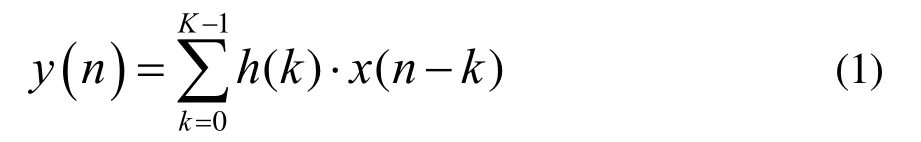

FIR滤波器的数学表达式可用K阶内积来表示:

其中K 表示FIR滤波器的抽头数;h( k)表示第k级抽头系数(单位脉冲响应);x( n-k)表示延时k个抽头的输入信号。

滤波器的单位脉冲响应均为实数,在幅度上只要满足下列两个条件之一,就能构成线性相位滤波器。第一类线性相位的幅度条件为偶对称如(2)式,第二类线性相位的幅度条件为奇对称如(3)式[4]。

FIR滤波器最基本的结构是直接型,由一个”抽头延迟线”的加法器和乘法器的集合构成,每个乘法器的操作数就是一个FIR系数。对每次采样y( n)都要进行K 次连续的乘法和(K-1)次加法操作,能够提供这种算法性能的高性能硬件平台对大多数信号处理设计者来说都有很大的吸引力。

2.2 分布式算法

分布式算法是一项重要的FPGA技术,被广泛运用于计算机的乘法运算中。该算法将乘法运算转换成加法以及移位运算,能够高速完成大量的乘法运算,极大地提高了芯片的使用效率。考虑一个内积运算[5]:

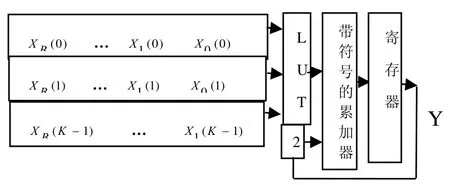

图1 分布式算法原理图

可以看出,分布式算法是一种以实现乘加运算为目的的运算方法,与传统的乘累加运算不同在于执行部分积运算的先后顺序不同,这个过程可用图1的结构来实现。该算法可以利用一个查找表(LUT)实现映射,即用一个2k字宽(即2k行),预先编好程序的LUT接受一个K位输入向量Xb=[X0b,…,X(k-1)b]的映射,经查找表的查找后直接输出部分积算法中的乘以位权2b可以通过图中的寄存器和累加器完成。这个过程可以用递归表达式表示成式(8),在执行了B次查找和B次累加后输出结果。

3 分布式算法在FPGA上的实现

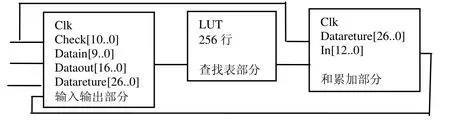

在FPGA上实现分布式算法,可将程序划出为输入输出、查找表、和累加3个部分,如图2所示。

图2 系统原理图

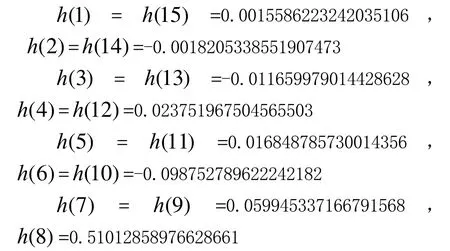

3.1 滤波器系数确定

滤波器系数的确定是利用MATLA B中的Simulink组件中信号处理模块的滤波器设计工具箱FDATOOL来计算。选定所需的各项参数后便可生成所需的系数。由于得到的系数均为介于[-1,1]区间的浮点数,而FPGA上只能进行定点数乘法,故将其量化为整数。

以设计一个16阶的低通滤波器为例,各项技术指标为:16阶低通滤波器、采样频率10M、截止频率3M、最小阻带衰减50DB、采用窗函数法、kaiser窗、beta=5、Scale Passband。

利用MATLAB中simulink的滤波器设计工具箱,可得滤波器的系数为:

将其同乘以1024便得到运算所需的系数。

3.2 输入输出部分

这部分的功能是对输入的模拟信号进行采集、处理,为后续数据处理做好准备,同时它还负责接收经过运算处理后的数据,并通过D/A转换芯片将其恢复为模拟信号。信号从这里流入,也从这里流出。除此之外它还负责产生整个系统所需的时序信号。

通过对晶振信号上升沿的计数,实现对采样速率的控制。按照所设计滤波器的阶数,建立相应于阶数的数据缓冲区。若所设计的为16阶滤波器,将采样得到的10位串行数据依次存入缓冲区,存满后则按照先进先出的流水线原则继续存入数据,缓冲区中始终有不断更新的16个数据。得到数据后,再依次将16个10位数据的每一位取出,组成16个10位的数据。如前所述,然后依次将每个10位的数据传给查找表部分,同时输出同步信号。

3.3 查找表部分(7)中可以看出,由于相加的和还要乘以不同的系数(2b),所以和累加部分与输入输出部分之间还有一条同步信号,用于确定二次幂加权的幂次。

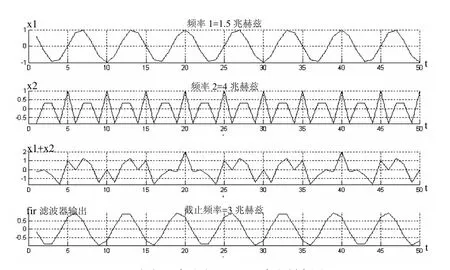

由于对系数进行了量化,即扩大了若干倍,如果直接将滤波的结果传回输入输出部分进行D/A转换,某些数据可能会超出范围,从而使信号产生失真。为此须对得到的结果进行移位缩小,使系统的输出波形避免失真。图3为此滤波器的应用效果图。

这部分的作用为接收经上一部分处理后的数据,利用查询方式找出每一个数据对应的值,然后将值传给下一级进行和累加。本部分用MATLAB编程然后直接导入FPGA的ROM中。部分代码如下:

%%产生分布式算法查找表内容

%利用matlab FDAtools设计滤波器,性能指标:16阶低通滤波器、采样频率10M、截止频率3M、最小阻带衰减50DB、采用窗函数法、kaiser窗、beta=5、ScalePassband、系数偶对称、保留8个。如下:

这部分电路功能相对简单,所需延时较短,所以没有信号设计专门的同步信号,而是将13位数据信号作为触发信号,即只要数据线上数据发生变化则立即完成查表操作。

3.4 和累加部分

查找表部分的输出数据在这部分进行相加,从式

图3 低通滤波器应用效果

4 结论

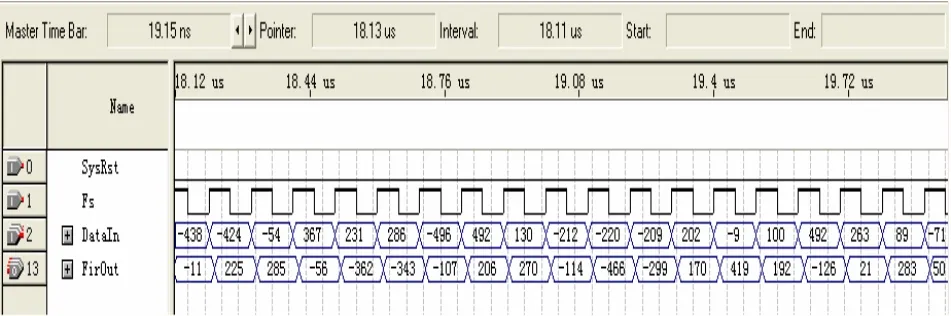

分布式算法非常适合于硬件实现,可以极大地减少硬件资源的消耗。本文讨论了分布式算法的原理和基本结构,并根据实际抽头数较多查找表规模过大的情况简化了算法,降低的抽头数,进一步提高了算法的效率。最后利用QII8.0进行调试,仿真结果表明实现16阶的FIR滤波器只需要占用硬件2%的逻辑单元,大大提高了硬件资源的实用效率。其功能仿真图如图4所示。

图4 系统功能仿真时序图

验证FPGA仿真结果:

FPGA仿真输出文件FirTop.vht中位置18.1us处验证datain=[-424,-54,367,231,286,-496,492,130,-212,-220,-209,202,-9,100,492,263];结果50

[1] 魏灵,杨日杰,崔旭涛. 基于分布式算法的数字滤波器设计[J]. 仪器仪表学报, 2008,29(10):2100~2104

[2] 赵岚,毕卫红,刘丰.基于FPGA的分布式算法FIR滤波器设计[J]. 电子测量技术, 2007,30(7):101~104

[3] 胡广书. 数字信号处理教程[M]. 北京: 清华大学出版社,2001:25~35

[4] HU G SH. Digital signal processing-theory, algorithm and realizes[M].Beijing : Tsinghua University Press, 1998:55~58

[5] 王学梅, 吴敏. 基于FPGA的分布式算法FIR滤波器的设计实现[J]. 世界电子元器件, 2004,10:65~67

Design of Digital FIR Lowpass Filter Using Distributed Algorithm Based on FPGA

Gui Jing Tian Senping

(The College of Automatic Science and Engineering, South China University of Technology)

The design method of FIR filter based on distributed arithmetic is researched in this paper. The algorithm can realize changeless constant multiplication and is applied in the design of FIR filter and a 16 order FIR filter. The EP3C25F324C8 is used. The speed of the process is improved effectively. The results shows that this method to be capable and high effective.

FIR Filter;FPGA;Distributed Arithmetic;LUT

桂婧, 女,1982 年1月出生, 硕士研究生,主要研究方向为系统工程和数字信号处理。