基于FPGA+ARM的实时大视场可视化图像融合系统设计

2010-06-27陈炳权刘宏立李波勇

陈炳权, 刘宏立, 李波勇

(1. 湖南大学 电气与信息工程学院, 湖南 长沙, 410082;2. 吉首大学 物理科学与信息工程学院,湖南 吉首, 416000;3. 郴州职业技术学院 工业自动化系, 湖南 郴州, 423000)

基于FPGA+ARM的实时大视场可视化图像融合系统设计

陈炳权1,2, 刘宏立1, 李波勇3

(1. 湖南大学 电气与信息工程学院, 湖南 长沙, 410082;2. 吉首大学 物理科学与信息工程学院,湖南 吉首, 416000;3. 郴州职业技术学院 工业自动化系, 湖南 郴州, 423000)

大视场可视化系统设备效果依赖于复杂的硬件系统和庞大的图像处理系统,成本相对较高,低成本的高分辨率图像实时采集处理系统是目前图像处理领域的热门研究课题. 笔者拟以FPGA为系统图像处理和控制的核心芯片,ARM处理器为通信控制接口(实现上位机对图像处理模块的通信和控制),重点阐述FPGA内部模块设计.通过调用FPGA内嵌的XtremeDSP模块,可以高速地完成对图像数据的乘累加运算. 实践结果表明:该系统可以应用在大视场可视化系统中,完成对高分辨率高帧率图像的实时处理,处理分辨率可达到1024×768,刷新率达60 Hz, 系统性能稳定,降低了成本.

FPGA;ARM;图像处理;大视场可视化系统

大屏幕显示作为一种“半沉浸式”的虚拟环境,在视频会议、公共场合演示等有着广泛的应用[1],大视场可视化系统[2]是一种可供多人同时使用的大屏幕交互式可视化系统,该系统以高沉浸感、实时性、交互性为特点,通常由图形服务器、投影系统、屏幕及相关附属设备等4个部分构成. 目前世界上流行的大屏幕显示系统是用多个投影仪阵列拼接的大屏幕显示系统[3],而拼接系统主要由大屏幕投影墙、投影机阵列、控制系统组成,其中控制系统是核心,其系统目前主要有硬件拼接系统、软件拼接系统、软件与硬件相结合的拼接系统等3种类型. 硬件拼接系统灵活性差、成本昂贵、扩展性差且受建筑物空间的限制,因此采用软件进行控制的多投影仪无缝拼接受到欢迎.

国外著名的研究大屏幕投影拼接系统的机构目前重点在研究投影的几何校正、颜色校正、拼接图像亮度混合等. 效果好的系统设备大多依赖复杂的硬件系统和庞大的图像处理系统来完成,成本高.成本较低的系统在图像处理的过程中还存在很多的问题,特别是在数据量庞大、图像的帧率和分辨率均要求较高的情况下,目前已有的硬件处理芯片均无法获得令人满意的效果,因此对低成本的高分辨率图像实时采集处理系统的研究迫在眉睫. 笔者将嵌入式处理器应用到图像处理系统上,避免使用PC机底板总线来连接各个模块的局限性,从而实现了图像处理板的分离式工作,能实现大视场可视化系统中图形服务器的图像几何校正、边缘融合和色彩校正等功能,同时可以完成对高分辨率、高帧率的视频图像数据的实时处理.

1 图像融合系统中的相关算法

在大场景可视化系统中,由于投影面是曲面,加上投影位置的不同,在图像被投影前,图像融合处理系统需要根据实际的投影环境对图像进行几何校正[2-4],使经过校正后的图像投影到投影面上不发生失真和变形. 为了利用多台投影仪得到一幅大型的无缝高分辨率图像,需要对原始图像进行拼接,通过拼接的图像需要进行边缘融合才能消除拼接所产生的影响. 由于投影仪之间颜色的差异,光度不平衡造成最后投影拼接图像的颜色不一致性,所以需要对投影仪进行最后的色彩校正.

图像的几何校正主要考虑数字图像的几何变换,一幅图像的几何运算需要2个独立的算法:定义图像的空间变换本身, 描述每个像素点的“运动”;对校正后的图像的每个像素点进行灰度级的插值运算,对每个坐标位置的像素点进行插值运算,以尽可能地减少几何运算后所带来的图像失真. 目前常见的变换方法为空间变换法(平移、旋转、缩放)、灰度插值法(最近邻插值、双线性插值、高阶插值).为了在算法的复杂度和图像处理效果之间得到平衡,笔者选择了算法较容易实现同时插值效果也比较好的双线性插值算法,其图像边缘处理得比较平滑,图像效果令人满意,该算法在FPGA中易于使用硬件逻辑实现,可以实现每幅图像的高速处理.

图像融合技术的核心任务就是把2幅图像的重合区域融合在一起,使其既包含2幅图像的特征,又具有良好的平滑性和视觉效果. 投影仪拼接过程中,对投影图像的边缘邻接部分需要进行边缘融合,通常有硬边融合、简单重叠、边缘融合等方法,前2种方法拼接中对多投影的拼接部分处理效果不是很好,与目标无缝拼接相差较远,因此在实际应用时较多应用边缘融合法.

在不同的颜色系统中存在不同的色域,在不同的色域中,颜色的种类数量有所不同,常用RGB色域存在3个原色,通过原色的不同强度的混合, 可以得到RGB色域中的所有颜色. 对投影仪而言,即使是同一制造商和相同的类型,投影仪之间也有轻微的色域差异,不同类型的投影仪之间的色域差异更大. 颜色校正中,首先得到每个投影仪的投影颜色样本,然后定义1个公共的色域作为标准色域, 再定义投影颜色样本的投影标准颜色,最后建立颜色光学曲解模型,求取投影颜色到标准颜色的颜色变换函数,通过它把投影颜色变换到标准色域内.

2 系统硬件设计

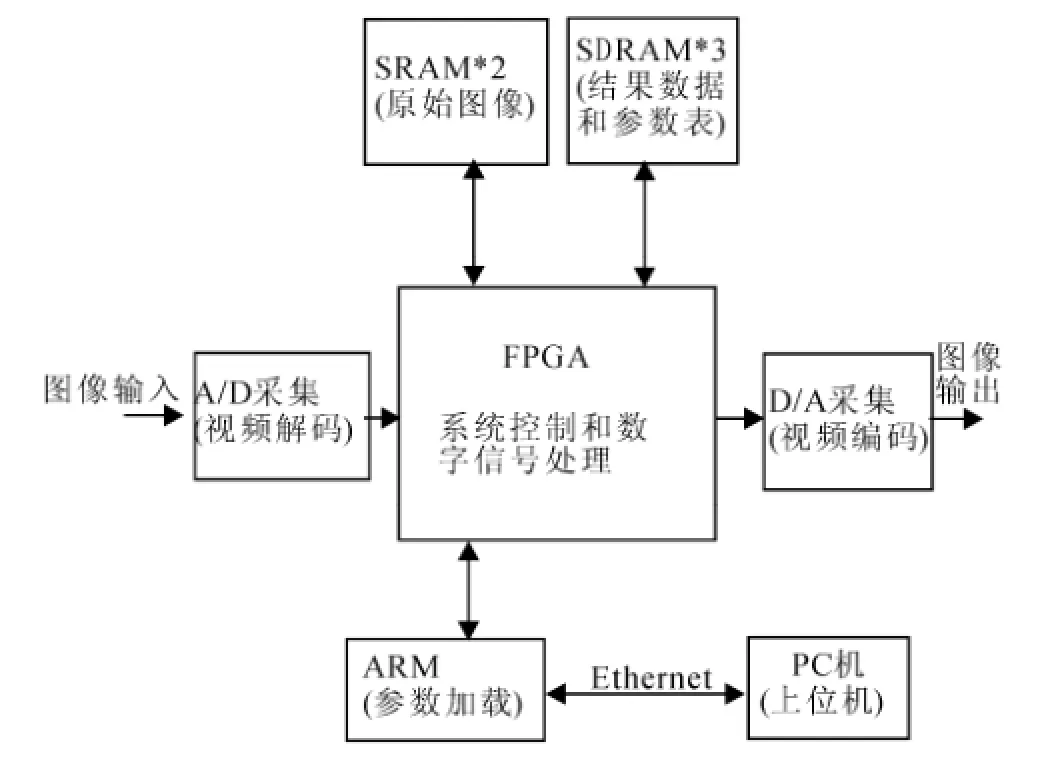

在高分辨率图像数据的实时处理中,影响系统实时处理速度的因素主要是数字信号处理器的运算速度以及系统访问外部存储器的速度. 为了实时地处理图像,文献[5-6]使用FPGA作为系统控制和处理的核心,FPGA器件内的各功能模块可以同时工作,从而可以通过流水线并行地执行,大大地加快了图像处理的速度. 为了简化系统硬件处理器处理图像算法运算的复杂度,同时降低实时处理系统硬件设计的难度,笔者将复杂的图像处理算法(即几何校正算法、边缘融合算法、色彩校正算法等)留在上位机完成,上位机根据图像处理算法生成一个算法参数表. 再通过ARM处理器下载到Parameter SDRAM. FPGA内部的图像处理模块根据计算好的参数表, 只需在内部实现简单的乘累加就完成图像的几何校正或色彩校正处理.

由于图像数据量很大,需要对原始图像数据、处理后的结果数据以及图像处理参数表进行缓存.大量的数据必须使用外部存储器[7]. 实时图像融合处理系统对原始图像进行处理时主要是进行几何校正和边缘融合等操作[8],这些操作对原始图像数据的访问通常是随机的,由于存储原始图像的存储器通常选用SRAM以提高响应速度,而对存储结果数据和参数表的存储器的访问通常具有顺序性,因此笔者选用SDRAM,从而在性能和价格之间得到平衡.

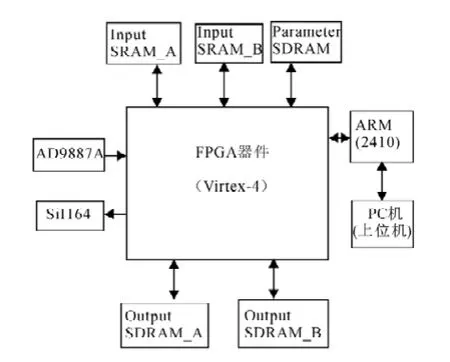

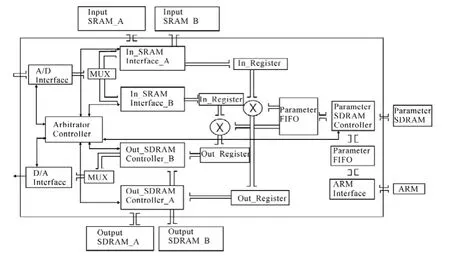

综合上述设计思路,笔者采用了如图1、图2所示的基于FPGA的高分辨率实时图像处理系统及其结构.

图1 高分辨率实时图像处理系统

图2 实时图像融合处理系统结构

图1中的高分辨率实时图像融合处理系统包括图像采集模块、FPGA模块、存储器模块、图像输出模块、ARM处理器模块以及上位机. 从宏观上可以将实时图像融合处理系统分为3个大的模块:上位机;用于通信控制接口的ARM处理器;数据处理相关的FPGA模块. 上位机主要用于人机控制界面,实现图像处理参数和色彩校正参数的计算功能.通过上位机,用户可以选择各种图像处理方式,在系统的安装和各模块的调试阶段,也通过上位机来完成相关的控制. ARM处理器主要用做通信控制接口,实现上位机对图像处理模块的通信和控制. 上位机和ARM处理器之间主要由串口和网口连接,串口主要用于上位机对ARM处理器的启动和控制,网口用于上位机下载参数表数据.

FPGA模块主要包括FPGA芯片和相关外围电路. 外围电路主要包括图像采集芯片、片外SRAM、SDRAM以及图像输出控制芯片. FPGA模块内部集成了大量的乘累加器,适合实现并行算法结构. 为保证系统的实时性要求,在系统的FPGA逻辑设计部分,笔者引入了乒乓操作、流水线设计和同步设计方法,如图3所示.

a. 数据采集模块. 完成与专用采集芯片AD 9887A的接口逻辑,接收从A/D输入的图像数据,同时在模块内部通过双口RAM实现图像数据的时钟域转换和图像帧的选择,最后把图像数据传输给原始图像SRAM接口模块.

b. 原始图像SRAM接口模块. 用于对SRAM芯片的读写进行控制,由于有2个原始图像SRAM接口模块,因此在图像采集模块和原始图像SRAM接口模块之间加入了多路选择器MUX进行2选1操作. 从图像采集模块输出的图像数据通过选择器MUX的选择被送入到被写的原始图像SRAM接口模块. 当对SRAM进行读操作时,原始图像SRAM接口模块根据图像运算模块输出的读地址,将对应位置的所需处理图像数据读出,送给图像运算模块处理. 由于引入了2组图像处理模块,原始图像SRAM接口模块之间不再需要多路选择器MUX进行选择.

c. 参数表SDRAM模块. 用于图像处理的相关参数,其中的每项对应1个需要处理的结果像素所需的参数信息,参数表中的每项包含有对应像素所需的4个像素中左上角像素的坐标以及4个像素分别对应的权值. 当系统开机时,参数表SDRAM控制器模块接受来自ARM接口模块的参数,并将其写入SDRAM中,此时的参数来自ARM处理器外挂的Flash芯片. 上位机中的新参数从网口下载到ARM处理器,ARM处理器通过FPGA内部的ARM接口模块将参数传送到参数表SDRAM控制器模块,最后写入Parameter SDRAM.

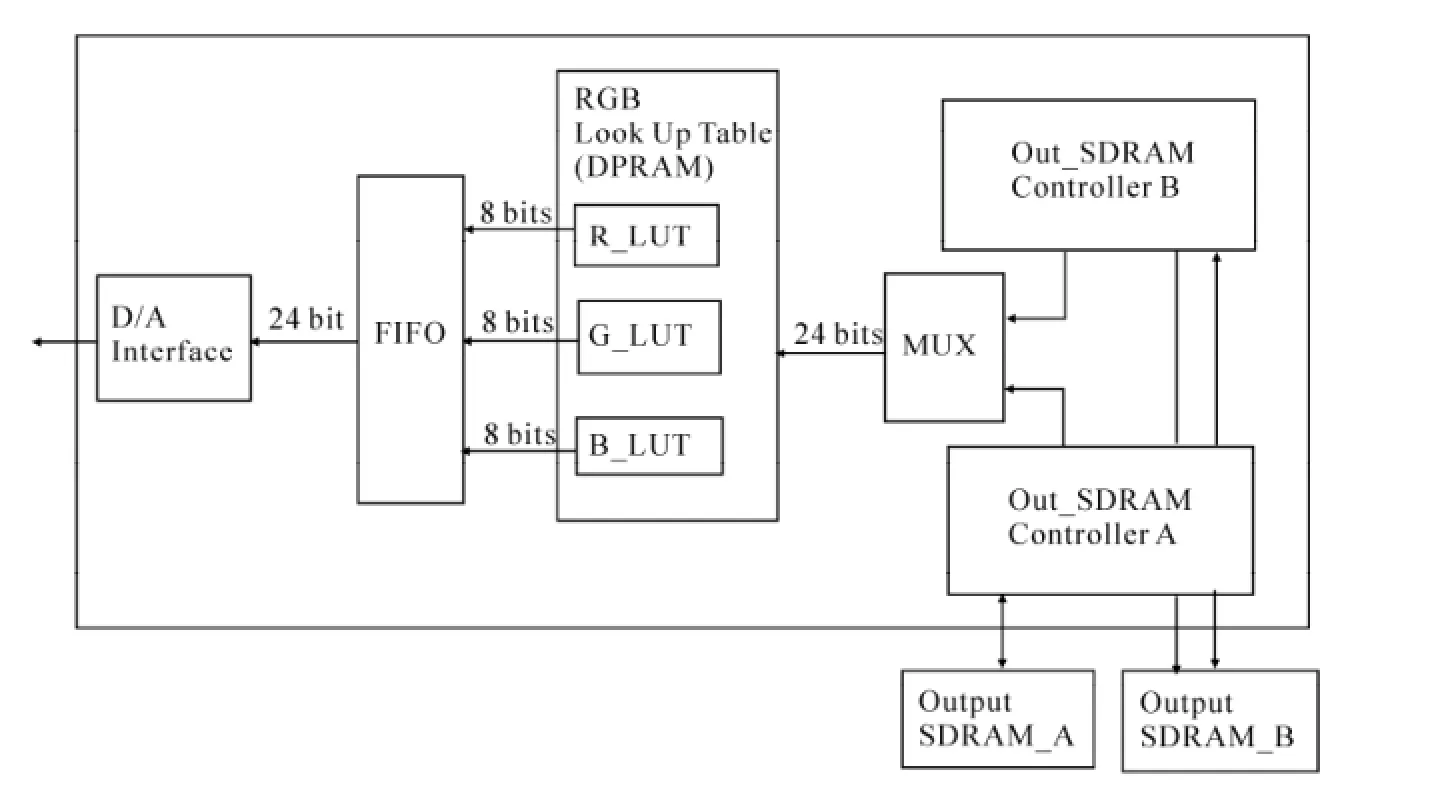

e. 图像输出模块.如图4所示,该模块主要完成输出图像的色彩校正以及芯片SiIl64的接口逻辑.该模块的核心部件是一个用双端口存储器(DPRAM)实现的色彩查找表,即图中的RGB Look Up Table.由于使用的RGB色彩格式, RGB色彩的3种颜色各用1个字节表示,其取值范围为0~255,所以查找表也分为3路并行查找表, 即图4所示的RGB Look Up Table中的R_LUT,G_LUT,B_LUT.

图3 FPGA内部模块功能

图4 图像输出模块

f. ARM接口模块. 该模块主要作为FPGA和ARM处理器之间的接口,完成ARM的命令控制和参数传递. 当系统上电后,ARM处理器将其外挂的Flash芯片中预先设定好的各种工作模式配置信息传送至ARM接口模块,完成对FPGA及各外围模块的配置. 然后设置默认的色彩校正表,最后将预先设定的图像处理参数通过ARM接口模块传送到Parameter SDRAM. 系统正常运行时,该模块处于闲置状态,直到上位机通过ARM处理器请求进行新的工作模式配置或者新的参数信息时,ARM接口模块再次传递新的配置信息或参数到FPGA.

3 FPGA图像处理模块设计及仿真

图像处理模块是整个系统的核心,其先以250 MHz的速率从FIFO中读取参数中的地址信息,并将其转换为读SRAM存储器的地址信号,然后以250 MHz的速率从FIFO中读取参数中的权值信息,并等待原始数据的到来,当以250 MHz的速率从SRAM中连续地得到结果像素的4个相邻的原始数据后,将权值信息和原始图像数据对齐,最后使用DSP48对原始图像进行处理计算. 为了保证图像处理的连续性,从参数表SDRAM存储器中读出的参数先要缓存在Read Par FIFO中,从而屏蔽读SDRAM时每行数据都进行激活操作带来的间断性.一旦进入处理过程,Read Par FIFO就会保证有参数可读,直到处理完一帧图像数据. 从Read Par FIFO中读取的参数信息都是连续的,对于每个结果像素所需的参数,前面32位为原始图像的二维坐标,后面32位为对应4个原始像素的权值.

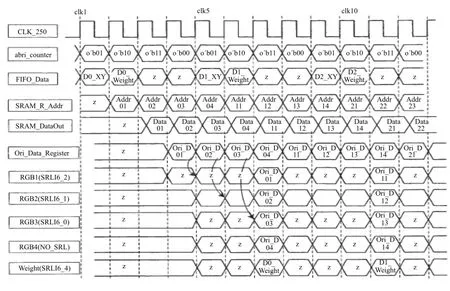

3.1 读取原始图像及其权值信息

读原始图像及其权值需用到的系统信号如下:a. 读写时钟信号为250 MHz的CLK_250变量;b.仲裁与控制器的图像处理状态变量frame_A和frame_B信号;c. 仲裁与控制模块的4进制计数器Arbi_counter信号,用于控制读取4个原始图像数据;d. Read Par FIFO的绝对空信号rfifo_empty,进行图像处理状态后,一旦Read Par FIFO非空,即可从中读取参数信息.

对于每个结果图像,从Read Par FIFO读其对应的参数信息只需要2个周期,因而读Read Par FIFO的使能信号Read_from_Read_ FIFO也是每2个时钟周期跳变1次. 通过该使能信号,从FIFO中读2个周期参数再暂停2个时钟周期. 从FIFO中读出的参数前1个周期是32位的坐标信息,后面32位为权值信息. 当从Read Par FIFO中取得第i个结果图像的参数Di_XY后,可以根据公式Addrl2=x+ 1 024y计算出左上角原始图像的地址. 该地址通过1st_Addr_EN信号寄存在1st_Addr寄存器内,对该地址加1即可得到第2个原始图像数据的地址. 为了得到第2组地址信息,在寄存第1个原始图像的地址信息时通过第2组地址参数寄存信号SRLl6_ 0_Yplus对参数Di_XY信息中的纵坐标Y进行加1后寄存,而x坐标不变,根据第2组地址公式Addr 34=x+1 024(y+1)得到第3个原始图像参数的地址,并通过3nd_Addr_EN允许信号寄存在3nd_Addr寄存器内. 通过从原始图像参数的坐标生成4个地址连续地送到SRAM接口,就可以连续地从SRAM_ DataOut端口得到1个结果像素所需的4个原始图像数据.

3.2 对齐计算数据

从坐标信息到得到原始图像数据共需要5个时钟周期,因而需要对提前得到的权值参数进行寄存并对齐. 在Xilinx公司的FPGA中,可以直接调用SRLl6进行移位寄存,使得权值参数与从SRAM中得到的原始图像参数同步地送入到DSP48的前端寄存器. 原始图像数据与权值参数的对齐时序如图5,其中SRAM_DataOut代表从SRAM的数据端口送出的原始图像数据,该数据被SRAM接口取得并被寄存在Ori_Data_Register寄存器内,Ori_Data_ Register中的数据每4个1组,对应1个结果像素所需的原始图像数据和Register原始图像数据,且与四进制计数器Arbi_counter中00到11这4个状态相对应.

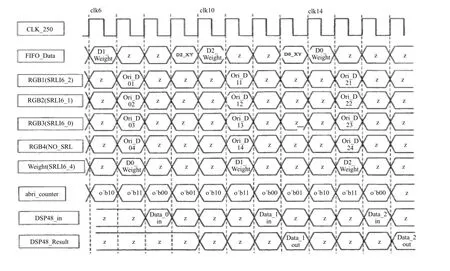

3.3 图像处理

为了并行地对图像实时处理,需要3路这样的连接模块同步进行操作,每路处理模块需要7个DSP48单元,通过虚线将连接图分为3个级. 最前面4个DSP48单元P1至P4分别进行乘法运算,完成Ri×Ki(i=l,2,3,4)运算. 该部分除了对前上级数据的寄存外,需要2个时钟周期. 中间的P5和P6单元分别对前一级的4个乘积进行两两相加,这一级只需要1个时钟. 最后1级的P7用1个时钟实现对前1级的部分和进行累加,从而得到校正过的R路颜色. 完成1个结果图像的处理模块需要5个时钟沿,即每4个时钟周期就可从P7端口得到1个结果图像数据. 对于1 024×768@60的图像,完成一帧图像的处理大约需要12.6 ms(1 024×768×4×4= 12.58 ms). 而系统时间为16. 666 ms,因而该图像处理模块能够满足系统的时序要求. 图6是图像处理时序图,该图与前面数据对齐时的时序图是连贯的.

图5 原始图像数据与权值参数的对齐时序

图6 图像处理时序

4 结语

笔者介绍了大视场实时图像融合处理系统的实现方案,阐述了该图像融合系统的各个分模块,分析了影响系统实时处理速度,设计的大视场实时图像融合处理系统可以实时地处理分辨率为1024× 768且刷新率为60 Hz的视频图像. 为了能够实时处理并输出高帧率的图像,就需要在极短的时间内完成对1幅图像的采集、处理和输出,笔者采用2组片外SRAM芯片以乒乓操作的方式工作,并以增加FPGA的I/O端口为代价,从而保证了系统实时处理图像的速度达到60帧/s.

[1] Thomas F, Kai L. Large-Format Displays[J]. Computer Graphics and Applications, 2006, 35(11): 20-21.

[2] 黄思敏. 视频图像几何校正卡的设计与实现[D]. 成都:电子科技大学, 2005: 33-56.

[3] 何 斌, 马天予, 王运坚, 等. Visual C++数字图像处理[M]. 2版. 北京: 人民邮电出版社, 2003: 120-135.

[4] 巨安丽, 郝重阳, 徐建荣. 边缘融合组合屏图像显示技术与系统研究[J]. 计算机仿真, 2006, 23(2): 267-269.

[5] 刘明章. 基于FPGA的嵌入式系统设计[M]. 北京: 国防工业出版社, 2007: 60-63.

[6] 潘松, 焚继业. SOPC技本实用教程[M]. 北京: 清华大学出版社, 2005: 115-163.

[7] 苏光大, 左永荣. 邻域图像帧存储体的理论及其实现[J]. 电子学报, 1999, 27(2): 85-88.

[8] 贾庆轩, 阮瑞, 孙汉旭, 等. 多投影面显示系统高度均衡的实现[J]. 系统仿真学报, 2006, 18(2): 478-482.

Design of real-time large field visualization image fusion system based on FPGA+ARM

CHEN Bing-quan1,2, LIU Hong-li1, LI Bo-yong3

(1. College of Electrical and Information Engineering, Hunan University, Changsha 410082, China;2. College of Physical Science and Information Engineering, Jishou University, Jishou 416000, China;3. Department of Industrical Automation, Chenzhou Vocational Technical College, Chenzhou 423000, China)

The effect of large field visualization system depends on complex hardware system and huge image processing system, which costs a great. Therefore, the study on real-time image acquisition and processing system of low cost and high resolution becomes the hot subject in the field of image processing. The authors take FPGA as the image processing and controlling core chip of the system, and ARM processor as the communication controlling interface; thus the host computer can achieve communication with and controlling of the image processing module. Emphasis is laid on the detailed description of the FPGA interior module design, and its image processing module is the core of overall system. Xtreme DSP module embedded in FPGA is used to realize multiply-accumulation of the image data. The practice results show that the system can be used in large field visualization system and in the real-time processing of high-resolution and high-frame image. The resolution rate is 1024×768, and refresh rate is 60 Hz. The system is stable, and it reduces the design cost.

FPGA; ARM; image processing; large field visualization system

TN 911.73

:A

1672-6146(2010)04-0066-06

10.3969/j.issn.1672-6146.2010.04.018

2010-06-20

湖南省科技厅科技计划项目(2010FJ4107);湖南省教育厅科学研究项目(08C714)

陈炳权(1972-), 男, 副教授, 博士研究生, 主要研究方向为模式识别、信号处理与智能控制.