M1A3P1000的多功能开发平台设计

2010-06-22黄秋元刘东

黄秋元,刘东

(武汉理工大学信息工程学院,武汉430070)

刘东(硕士研究生),主要研究方向为嵌入式系统应用开发与高速电路设计仿真。

1 平台硬件设计

1.1 主板电路设计

M1A3P1000内置Cortex-M1内核,功能强大,内部已经集成了多种控制器资源,因此可比较方便地在片外添加相应外设。本开发平台在硬件设计上,采用 FPGA主板加扩展子板的架构,可以通过丰富的GPIO资源进行系统级的软、硬件设计开发;也可进行功能扩展,进行相关的产品设计。平台硬件结构如图1所示,主板电路以M1A3P1000为处理器,按照功能可分为:电源部分、缓冲部分、存储器扩展部分(包括SDRAM 、SRAM、NOR Flash等)、IrDA、USB控制器、子板扩展部分等。

(1)电源模块

开发平台用到的标准电压有:5 V、3.3 V、1.8 V、1.5 V,需要给FPGA内核、存储器、IrDA、外部的高速扩展子板等器件供电,要求电压稳定。考虑到 DC—DC纹波较大,调试比较繁琐,另外平台所需电流也较大,因此选用有较高 PSRR的 LDO(低压差线性稳压器)芯片,EXRA公司的SP29302以及NS公司的 LM1117。

图1 开发平台结构框图

SP29302输出电流3 A,LM1117输出电流800 mA,精度±1%。电源部分结构框图如图2所示,平台采用5 V电压适配器直流输入,通过 LM1117转换为3.3 V,给FPGA的I/O供电。还有一路通过SP29302转换为3.3 V给存储器、子板电路及其他外设供电,然后此路3.3 V再经过LM1117转换为1.5 V给FPGA内核供电,另一个LM1117转换为1.8 V给IrDA和Buffer供电。

图2 电源部分结构框图

(2)存储器部分

考虑到处理能力、易扩展性等因素,本系统平台共采用了3种类型的存储器:NOR Flash、SDRAM 、SRAM,默认访问数据宽度均32位。

Flash存储器具有低功耗、大容量、擦写速度快等特点,一般分为NOR Flash和NAND Flash两类。NOR Flash可以直接运行装载于NOR Flash里面的代码,在系统启动的时候直接运行它,不必再把代码读到系统RAM中。NAND Flash能提供极高的单元密度,可以达到高存储密度,且写入和擦除的速度也很快;其缺点是比较容易出现坏块,不能直接运行NAND Flash上的代码。本系统平台选用2片Spasion公司的NOR Flash存储器S29JL064H,容量为4M×16位,工作电压2.7~3.6 V,CPU可对其32位操作,一片为高16位,一片为低16位,两片复用地址线。NOR Flash主要用于存储启动代码、操作系统、用户应用程序及数据信息等,连接示意图如3所示。

图3 NORFlash电路连接框图

SDRAM具有单位空间存储容量大、速度快、价格低等优点,其存储单元可理解为一个电容,必须定时刷新(充电)来避免数据丢失。为充分发挥32位Cortex-M1内核的处理能力,本文并联 2片ISSI公司 16 MB的IS42S16400A,构建32位的SDRAM 存储系统,工作电压3.3 V。如图4所示,用于存放系统及用户堆栈、程序代码及大量动态数据,也是程序运行的场所。

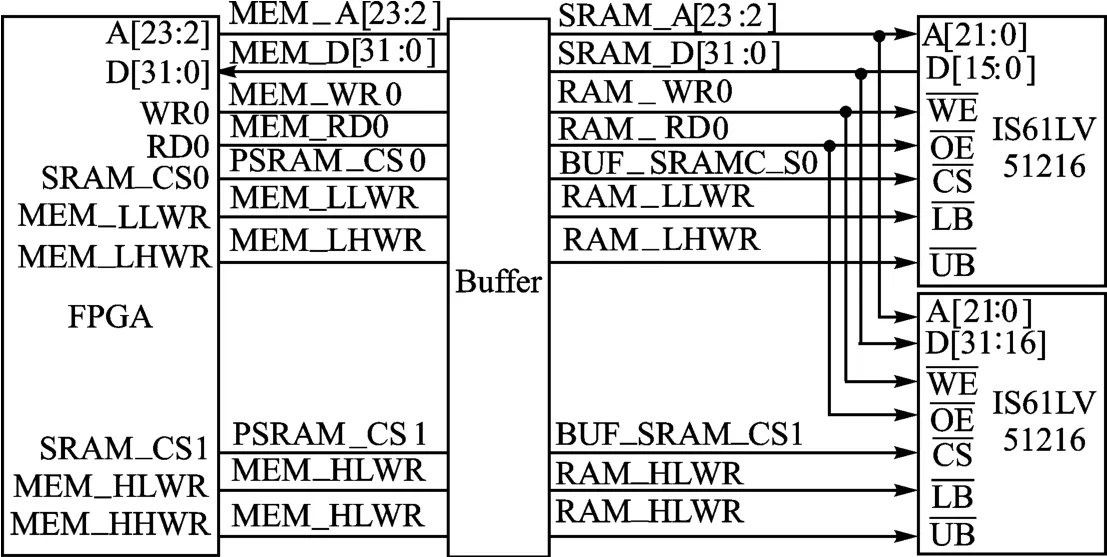

SRAM处理速度快,加电情况下不需刷新,数据不会丢失,常用作高速缓存容量较低的情况。本开发平台采用了ISSI公司的2片1 MB的SRAM IS61LV51216,通过SRAM_CS0和SRAM_CS1信号实现16位和32位操作。由于Flash、SRAM、USB、IrDA、扩展BUS等总线设备均通过内部MemC-trl控制器控制,考虑到FPGA的I/O扇出问题,加入了缓冲芯片Buffer,增加扇出能力。连接框图如图5所示。

图5 SRAM电路连接框图

(3)USB及ⅠrDA部分

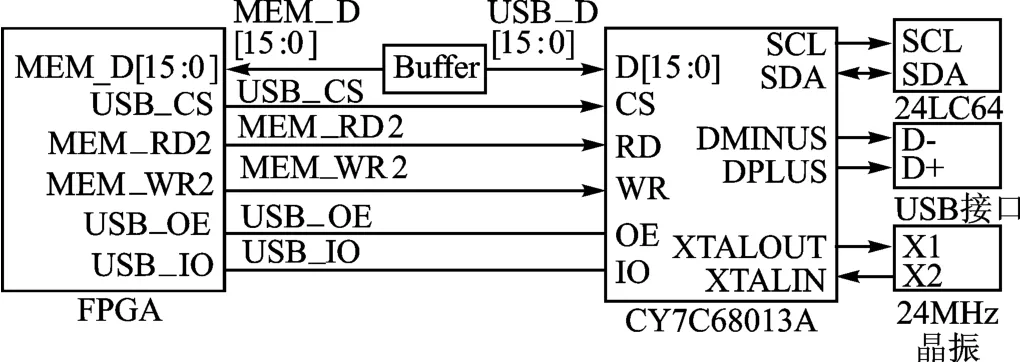

为保证FPGA能与PC侧实现快速的数据交换,通过FPGA的I/O口采用总线方式扩展了USB Host控制器。芯片采用Cypress公司的CY7C68013A来实现,时钟由24 MHz晶振提供,支持USB2.0协议,速度可达480 Mbps,16位数据总线加入Buffer,增加驱动能力。EEPROM芯片24LC64用来存储CY7C68013A启动的程序和数据,数据交换由I2C总线实现。电路结构框图如图6所示。

图6 USB电路连接框图

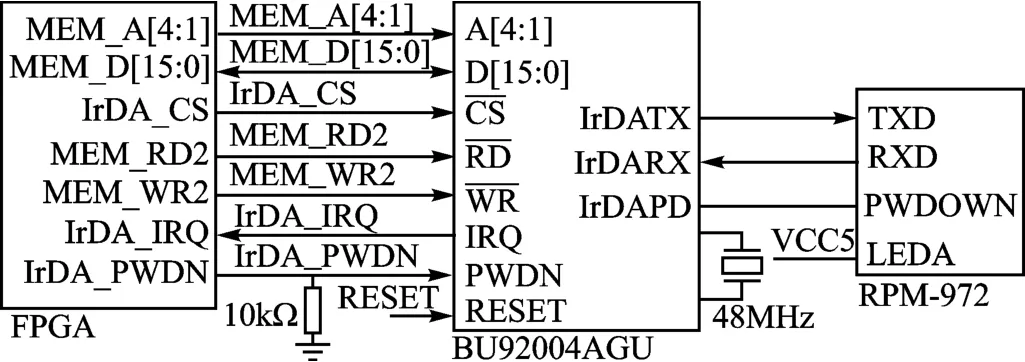

红外通信(IrDA)部分选用ROHM公司的IrDA控制模 块 BU92004AGU 和 通 信 芯 片 RPM972-H14。BU92004AGU内置5 KB的FIFO,以帧为单位分割数据,数据总线16位,且不需DMA控制,分别为读写控制、片选及中断信号,均低电平有效。通过16位数据总线和4位地址总线与FPGA实现数据传输,而其与通信芯片RPM972-H14的数据传输由TX、RX串口实现,工作时钟由外部48 MHz晶振提供,支持SIR和FIR,最高速率可达4 Mbps。由于 RPM972-H14内部发光二极管需要电流较大,约为200~300 mA,因此通过VCC5给内部LED供电,I/O电压为3.3 V,FPGA通过IrDA_PWDN信号对IrDA模块实现功耗控制,由10 k Ω电阻下拉,默认为低电平。IrDA部分电路结构框图如图7所示。

图7 IrDA电路连接框图

(4)外部总线扩展

平台通过64脚连接器扩展了24位地址线、16位数据位、GPIO、各类控制信号,还扩展了 RS232接口、2个JTAG接口(20脚的用于 Cortex-M1调试、10脚的用于FPGA配置)。另外,扩展10个子板连接器,提供I2C总线、SPI总线、UART、GPIO 及 3.3 V 电压。通过这些扩展口可以方便地实现多功能的项目开发。

1.2 GPS子板电路设计

本开发平台的多功能体现在,通过丰富的I/O资源扩展出多个连接器,分别设计了400 M Hz RF、蓝牙、GPS、温度传感器、陀螺仪等多个子板,插拔灵活,支持不同项目开发,可满足多功能开发的需求。由于篇幅有限,本文只介绍GPS子板的设计。

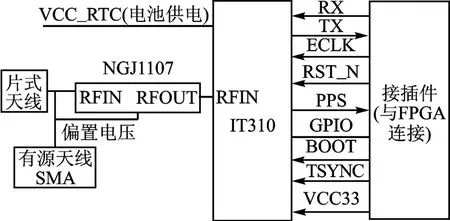

GPS子板采用Fastrax公司的IT310模块。该模块内置RFIC和基带处理IC,固件可从串口更新,内部可产生32.768 kHz的RTC时钟和16.369 MHz的主时钟,工作电压3.3 V,功耗典型值为110 mW,RF输入最大值+15 dBm,电路设计结构框图如图8所示。

图8 GPS子板电路结构框图

GPS天线采用片式天线,中心频率为1 575 MHz,带宽20 M Hz,增益大于1 dB,另外预留了有源天线SMA接头,增加设计灵活性。在RF信号进入GPS模块之前加入了低噪声放大器(LNA)NGJ1107,其内部集成DC隔离电容、偏置电路、放大电路,工作频段在1.5 GHz~2.4 GHz之间,工作电流仅为2.5 mA。GPS子板通过扩展连接器与FPGA主板对接,由串口RX和TX信号实现数据传输,BOOT信号可实现UART和内部Flash启动模式选择,调试方便;FPGA通过RST_N信号对GPS模块复位,ECLK是预留的外部时钟输入,需由10 kΩ电阻上拉至3.3 V;TSYNC是同步脉冲信号,上升沿触发,由FPGA控制同步接收卫星数据,默认为低电平,由10 kΩ电阻下拉至地。子板无独立电源,3.3 V由主板提供,并通过MOSFET实现功耗控制,不用时将其切断,也可由跳线实现。为保证内部RTC持续工作,时间信息不丢失,断电时由3 V/150 mA的锂电池为RTC提供备份电压VCC_RTC。

1.3 PCB设计要点

主板采用8层PCB,叠层结构为:信号层—地层—信号层—地层—电源层—信号层—地层—信号层,复用总线器件采用菊花链布局。叠层中单独设置电源层并对其分割,以降低直流阻抗。FPGA每两个电源引脚加入 1个0.1 μ F电容 ,每一个 bank 加入 1 个 10 μ F 和 1 个1 μ F电容,滤除高频噪声、抑制纹波,电源走线需在0.5 mm以上,按1 A/1 mm的规则计算。对于SRAM、SDRAM等数据线和地址线,走蛇形线,同类走线走一层,使其等长,在时钟周期内时延一致,保证信号完整,但需保证其自身走线之间宽度3倍于线宽,防止串扰。对于时钟、片选和总线信号,应尽量远离I/O线和接插件。晶振走线尽量短而宽,且少打过孔,并用地线包裹,屏蔽辐射,减少干扰。对数据线和时钟线进行SI仿真,修改优化布线规则,尽量做到一次投板成功,缩短开发周期。

GPS子板采用4层PCB,叠层结构为:信号层—地层—信号层—地层。RF信号及低频信号走Top层,其他关键信号走中间层,保证关键走线屏蔽良好。RF信号需进行50 Ω阻抗匹配,与铺铜地网络距离要大于6 mm,可减小耦合衰减与串扰。LNA的地引脚应多点有效接地,为RF信号提供较好的屏蔽。

2 FPGA逻辑设计

2.1 SoC平台搭建

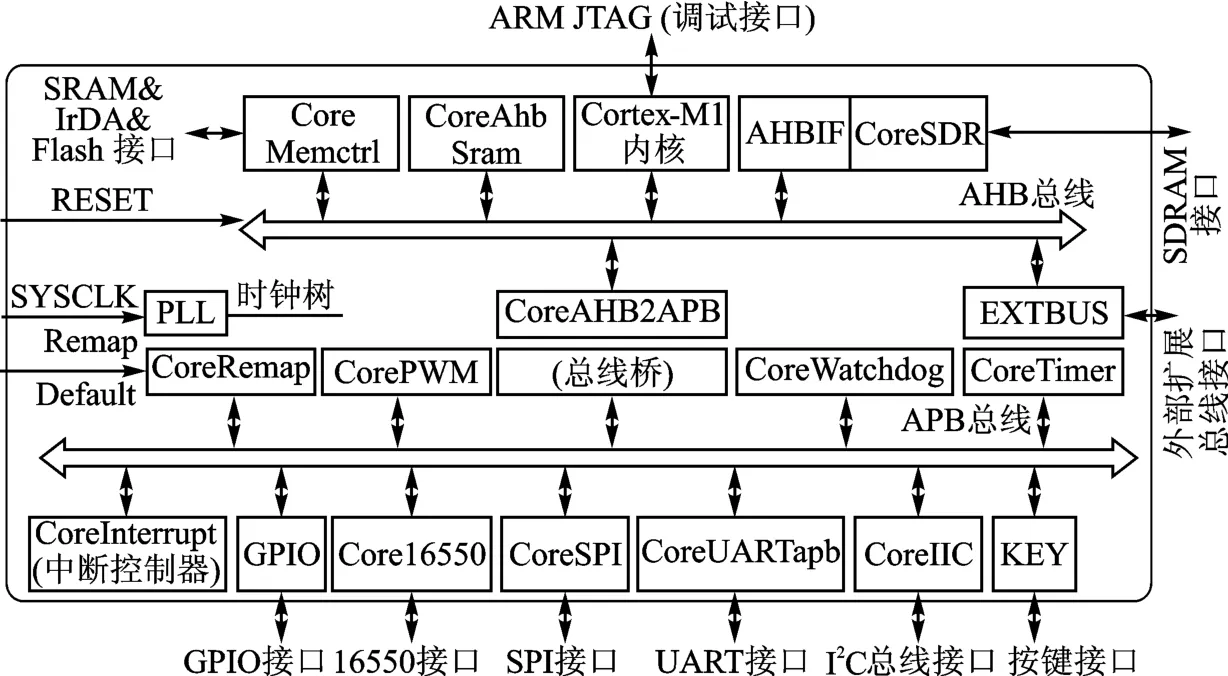

M1A3P1000内部集成了Cortex-M1处理器,该处理器内核是基于ARM公司推出的AMBA总线架构,包括AHB和APB。AHB是片内高速总线,主要用于挂载高性能高时钟频率模块,支持多主控制器,可配置32~128位总线宽度;APB主要用于挂载低带宽低频率的周边外设,不支持多主模块,唯一的主模块是AHB2APB桥。M1A3P1000内部的SoC是在 Libero8.5平台上搭建的,具体结构如图9所示。

图9 SoC结构框图

基于 AHB和 APB挂载了 Cortex-M1、CoreAhb-Sram 、CoreRemap、CoreInterrup、CorePWM 、CoreWatchdog 、CoreSPI、CoreIIC 、Core16500 、CoreUART 、CoreSDR 、GPIO、CoreMemctrl等多种 IP核,AHB与 APB之间以AHB2APB桥连接,主要用来锁存来自AHB系统总线的地址、数据和控制信号,并提供二级译码以产生APB外设的选择信号,实现 AHB协议到 APB协议的转换,也是Cortex-M1对外设控制的桥梁。通过JTAG接口调试Cortex-M1内核。CoreInterrupt核可支持32个IRQ和8个FIQ中断源。由外部复位电路输入RESET信号为系统复位,通过PLL硬核作为时钟分配器,只需1个14.745 6 MHz的板级晶振输入系统时钟SYSCLK,即可配置参数产生多种时钟,由时钟树给系统及各模块提供时钟,避免了在板级加入多个晶振所带来的SI问题,减小PCB设计难度,增强平台的稳定性。

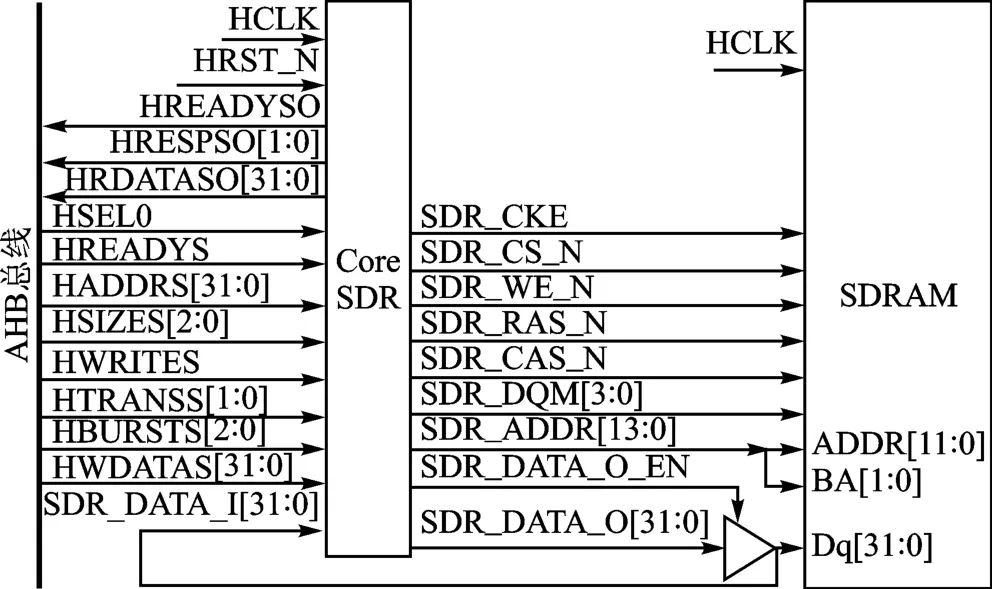

2.2 SDRAM控制器设计

Actel公司提供的CoreSDR模块没有提供AHB slave接口,无法直接操作外挂SDRAM,因此在Libero8.5平台上,由Verilog语言实现了简单的CoreSDR设计,并通过Modelsim前仿,可对SDRAM正确读写,成功进行平台协同验证。

CoreSDR作为挂载在AHB上的Slave设备,是 AHB与SDRAM数据读写的纽带,包括控制、刷新、数据通路3个模块。其作用分别为:控制模块接收来自AHB总线的命令、地址等信息,对刷新请求、读写请求等进行仲裁,产生接口控制命令、时序参数和存储器访问地址,对SDRAM器件进行操作;刷新模块产生周期性的刷新命令请求,根据不同的SDRAM设置刷新计数器值,当计数器减到0时,产生刷新请求信号REF_REQ;数据通路模块控制数据以正确的时序在AHB与SDRAM之间有效传输。CoreSDR结构框图如图10所示。右端为SDRAM常用信号,左端作为Slave设备与AHB的连接情况。其中HCLK为系统时钟;HRST_N为复位信号;HREADY为传输状态,1表示传输完成,0表示传输未完成,需延长传输时间;HRESP表示传输响应信息;HRDATA表示读数据总线;HSEL为从设备选择信号;HWRITES表示写数据信号;HSIZES为AHB传输宽度指示(字、字节、半字等),本系统中位宽为32位,设置为010;HTRANS表示当前传输数据的类型;HWDATA 表示写数据总线,支持32比特传输。

CoreSDR的状态机主要分3个操作:初始化、写操作、读操作。在上电复位后进行初始化操作,首先配置寄存器(sdr_cfg),主要包括设置刷新计数器值、定义延时参数 Tcl、tRAS、设定 SDRAM大小、bank数目、列的位宽,然后执行初始化操作,包括对所有bank执行预充电、执行模式寄存器写命令、启动自动刷新、进入正常读写状态。

图10 CoreSDR结构框图

编者注:本文为期刊缩略版,全文见本刊网站www.mesnet.com.cn。

[1]ProASIC3 Flash Family FPGAs Datasheet[EB/OL].[2009-08-16].http://www.actel.com/documents/PA3_DS.pdf.

[2]周润景,袁伟亭.Cadnec高速电路设计与仿真[M].北京:电子工业出版社,2007.

[3]IT310 specification[EB/OL].[2009-08-16].http://www.Fastrax.com.

[4]李瑞,赵建明,等.基于SOC的SDRAM 控制器的分析与设计[J].信息技术,2007(12).