PAL一体化摄像机设计

2010-06-05张起贵

郑 静,张起贵

(1.山西综合职业技术学院 计算机工程系,山西 太原 030006;2.太原理工大学 信息学院,山西 太原 030024)

一体化摄像机因其体积小巧、价格低廉,安装简便等特点广泛应用于监控、教育、医学等领域。一体化摄像机根据使用对象的情况和要求来进行设计[1]。基于FPGA器件的可并行处理能力及其可重复编程的灵活性[2],提出了一种以DSP+FPGA+ASIC为架构的系统解决方案,改善了以往一体化摄像机功能扩展困难的问题,提高了图像的质量,扩大了其应用范围。

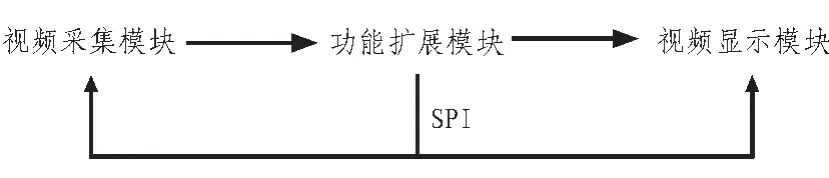

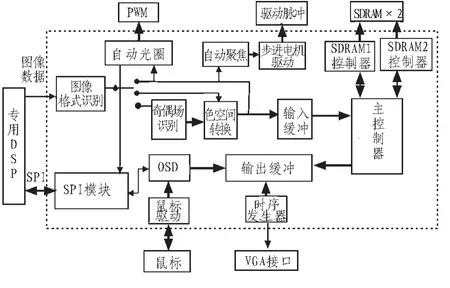

图1 系统硬件框图Fig.1 Diagram of system hardware

1 系统硬件设计

系统硬件框图如图1所示。视频采集模块采用SONY公司摄像机套件,主要包括470 K像素PAL制CCD ICX229AK,AFE (模 拟 前 端 )CXA2096N和 专 用 DSP CXD4103。该模块先将CCD采集到的图像数据经DSP处理后, 输出分辨率为 748×584的 PAL制 YUV (422)ITUREC656格式的数字视频信号,同时输出行、场参考信号和像素时钟信号。这些信号先经过FPGA图像处理模块,实现自动聚焦、4幅图像存储、鼠标驱动及划线功能、实时图像与存储图像上下左右对比、OSD叠加、图像冻结、负片显示、镜像、彩色黑白选择输出等功能。处理后的信号最终送到视频显示模块,经过专用集成电路(PW1226)处理后产生RGB图像信号及标准SVGA格式的行、场同步信号,使图像传感器采集的图像可在VGA显示器上实时显示。

1.1 视频采集模块

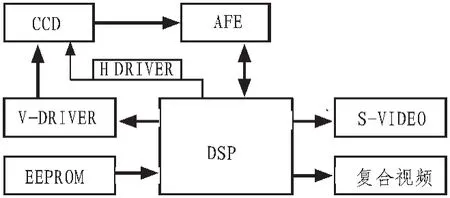

图2为视频采集模块硬件框图。系统上电后,DSP从EEPROM中读取初始化信息。初始化完成后,DSP产生CCD行、场时序信号,同时产生AFE(模拟前端)的采样时序信号。CCD在行、场时序作用下,送出采集的原始图像数据,在AFE经过CDS(相关双采样)、AGC(自动增益控制)后,将量化后的信号送入DSP。DSP内置10 bit的ADC将量化信号转为数字信号,对其进行噪声滤波、电平箝位、自动白平衡、边缘增强等处理后,输出PAL制YUV(4∶2∶2)格式的数字视频信号。同时DSP直接输出复合视频及S-VIDEO。

图2 视频采集模块硬件框图Fig.2 Hardware diagram of video module

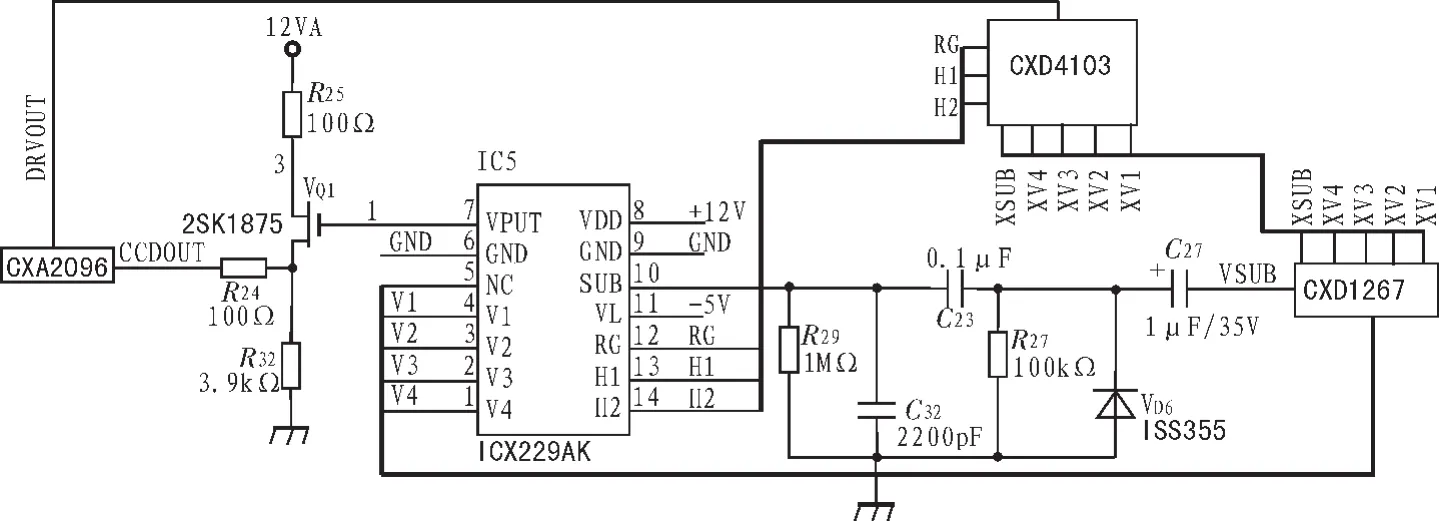

CCD周边电路设计如图3所示。ICX229AK为1/4英寸PAL补色图像传感器,其有效分辨率为PAL制752(H)×582(V),工作电压为12 V,采用14引脚DIP封装;采用超 HAD技术,具有很高的灵敏度并能获得高饱和度的视频信号;具有画质细腻、色彩鲜艳、信噪比高等优点。

该CCD采用12 V和-5 V电源供电,DSP时序发生器同时发出行、场时序驱动信号,场驱动信号通过CXD1267进行放大整合后生成供给CCD的场时序驱动信号V1、V2、V3、V4,与DSP发出的行信号H1和H2同时送到CCD,使其开始正常工作,采集到的电信号经过场效应管2SK1875放大,得到模拟输出信号CCDOUT,该信号送至采样电路CXA2096。

C27,R27,VD6,C23构成自举升压电路, 把 CXD1267 发出的VSUB信号转换为CCD可接受的电压幅值,即SUB信号,它是电子快门控制信号,通过控制传感器像素表面的电荷积累时间操纵快门。当电子快门关闭时,对于PAL摄像机,CCD电荷累积时间为1/50 s,电子快门则以311步的基本单位覆盖,其范围1/50~1/10 000 s。当电子快门速度增加时,在每个视频场允许的时间内,聚焦在CCD上的光减少,结果将降低摄像机的灵敏度。

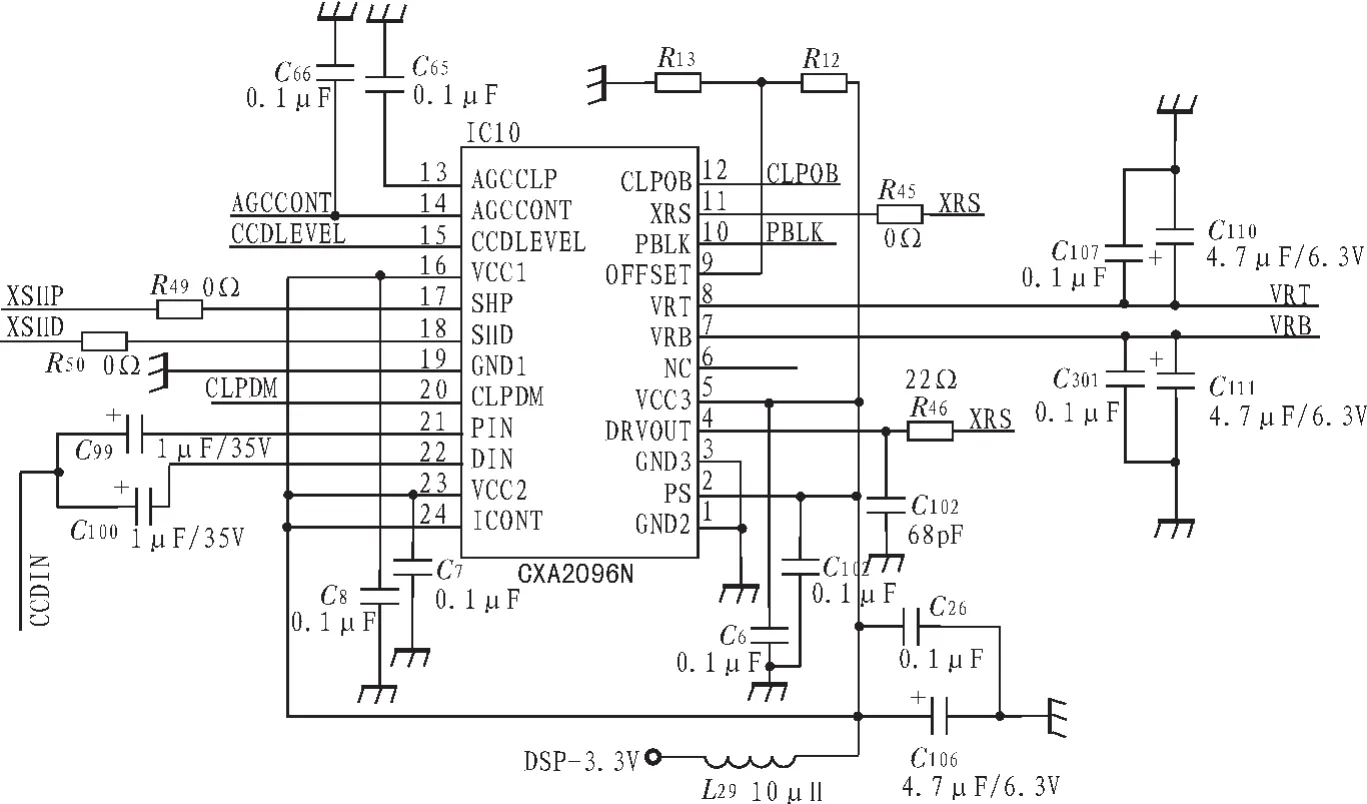

AFE周边电路设计如图4所示。

图3 CCD电路原理图Fig.3 Principle diagram of CCD circuit

图4 CXA2096N电路原理图Fig.4 Principle diagram of CXA2096N circuit

CXA2096N采用3.3 V供电,其主要作用是对模拟电信号进行采样、保持、放大,封装是24引脚SSOP(Plastic)。CCD送出的模拟信号CCDOUT,经2SK1875放大后传输给CXA2096N,经CXA2096N采样、保持、放大后得到 DRVOUT信号传输给DSP。CXA2096N是信号进行模数转换前的最后一个环节,其重要性不言而喻,同样地,CXA2096N也是在DSP时钟发生器的时序驱动信号下完成其一系列工作的。其中最重要的3个信号分别是CCDLEVEL、OFFSET和AGCCONT。

CCDLEVEL是CXA2096N的输出信号,这个信号直接反映了CCD采集到信号的电平大小、变化程度和范围。CCD正常情况下采集到的黑电平信号约2.7 V。

OFFSET是CXA2096N的输出信号,变化范围1.5~3 V,这个信号反映的是一个偏移量,DSP可以通过它改变CXA2096N的采样偏置电压,这一改变直接反应在视频显示处理板中,体现到最终的图像显示效果上。OFFSET越大,图像整体向明亮的区域变化,反之,则往黑暗的区域变化。因为OFFSET信号使得图像整体偏移变化,用一个形象的比喻,它是一个“加”的关系,即图像数据整体增加了一个偏置电平。AGCCONT也是CXA2096N的输出信号,变化范围1.5~3 V,这个信号反映的是一个增益量,所有一体化摄像机都有一个来自CCD的信号放大到可以使用水准的视频放大器,其放大量即增益,等效于较高的灵敏度,可使其在微光下灵敏,然而在亮光照的环境中放大器将过载,使视频信号畸变。为此,需利用一体化摄像机的自动增益控制(AGC)电路去探测视频信号的电平,适时地开关AGC,从而使摄像机能够在较大的光照范围内工作,即动态范围,在低照度时自动增加摄像机的灵敏度,从而提高图像信号的强度来获得清晰的图像。外部单片机或DSP可以通过改变CXA2096N的放大增益系数,直接反应在视频显示处理板中,体现到最终的图像显示效果上。AGCCONT越大,图像整体向明亮的区域变化,反之,则往黑暗的区域变化。因为AGCCONT信号使得图像整体偏移变化,即图像数据整体“乘”增益系数。

CXA2096N的采样需要一个基准电压,否则采样的数据会有偏差,这对将来的视频数据处理影响非常大的。采样校准电压VRT和VRB一定要保证准确,VRT为2.35 V,是采样上限;VRB为1.35 V,是采样下限。同时VRT和VRB输出给A/D转换器,作为其量化的参考电平。

1.2 FPGA图像处理模块

该模块的逻辑结构如图5所示。该模块基于FPGA设计,实现自动聚焦、自动光圈控制、帧率提升、OSD以及SPI通信功能。FPGA采用XILINX公司的XC3S250E。内部功能采用自顶向下的层次式设计方法[3],并用VHDL硬件描述语言实现,最终由ISE 6.0综合生成位流,固化在外部的存储器中。

图5 FPGA图像处理模块的逻辑结构Fig.5 Logical structure of FPGA image

FPGA将接收的YUV(4∶2∶2)格式的信号进行格式识别和转换,然后在SDRAM中把连续2场图像缓冲为一帧图像,下一帧图像缓冲在另一片SDRAM中,形成了连续切换视频双缓冲结构。当其中一片SDRAM输入图像时,另一片在VGA显示控制器的控制下通过输出FIFO以SVGA@60 Hz的点速率输出图像,具体过程如下:

该模块首先对输入信号进行奇偶场识别,奇场扫描的第一行有374个像素,偶场扫描的第一行有748个像素,通过对一场的第一行数据计数判断,可知当前场为奇场或偶场,然后从下一个奇场开始接收数据。这样确保了相邻两场为一帧完整的图像。此模块为深度748、宽度16 bit的异步FIFO(先进先出),写地址计数器为0到748的循环计数器,当其计数到300或700时,给主控制器发送读信号,主控制器随后产生FIFO的读使能信号,使读使能信号在连续的374个读时钟周期内一直有效,即可连续读出374个数据。本设计读时钟频率大于写时钟频率,不会产生数据写满溢出的现象。

主控制器通过对输入缓冲的读请求信号和输出缓冲的写请求信号处理,实现对2个SDRAM的读、写操作切换。该模块首先完成对SDRAM的初始化,SDRAM被设置成连续的全页迸发模式。然后SDRAM进入正常工作状态,准备接收读、写命令。当SDRAM在空闲状态下,为保持其数据不丢失,必须对其定时刷新,一般要求64 ms内刷新4 096次,但是当SDRAM在进行读、写迸发时,自动刷新命令会打断读、写,从而造成数据丢失。该设计在64 ms内对SDRAM至少进行4 096次读、写操作,所以可以不必对其刷新。当SDRAM读、写到374时,发出预充命令来停止迸发,同时关闭当前行,为下一次读、写作好准备。SDRAM被设置成迸发模式,迸发长度为374。

首先时序发生器利用40 MHz的主时钟产生符合VESA标准的行、场同步信号,同时在行、场参考信号都有效,且 39<行计数器<788、19<场计数器<604时产生输出缓冲的读使能信号。输出模块为深度748、宽度16 bit的异步FIFO。写时钟和读时钟同为40 MHz的主时钟 ,当读使能有效时,启动读计数器从0到799循环计数。该设计每隔10个数据将前一个数据重复读出,直到输出800个数据。当读计数器计到100或500时,该模块向主控制器模块发写请求命令。在行、场消隐期间,读使能信号无效,所以不会产生读空现象。

经过PW1226视频显示模块进一步滤波,消除行场间闪烁效应,提高画质,并可平滑放大到1 024×768的分辨率,最终输出SVGA或XGA的标准的VGA视频接口信号。

同时FPGA还可以通过内部的SPI模块实现对DSP和CXD4103的寄存器设置,使其正常工作。

1.3 自动聚焦

首先,FPGA通过对图像亮度信号Y的处理来实现自动聚焦功能。选择常用的灰度差分法作为聚焦评价函数[4],选取中心像素过去的4个像素(左侧、左上侧、右侧、右上侧4个像素)计算差分值。

由于聚焦评价函数需要用中心像素所在行及上一行临近的4个像素,所以需要在FPGA内部使用2个双口RAM做相邻两行数据缓存区,每个双口RAM容量为800×8 bit。读写选择模块将一帧图像的第1行数据写入RAM1,将第2行数据写入RAM2。在写入RAM2一个时钟周期后,开始读出RAM1和RAM2中的数据,送到聚焦评价函数算法实现模块,以RAM2中的图像像素为中心像素计算亮度差值绝对值和,当第3行图像数据到来时再次写入RAM1,同样在写入RAM1一个时钟周期后,读出RAM1和RAM2中的数据并送到聚焦评价函数算法实现模块,同样以RAM1中的像素为中心计算亮度差值绝对值和,如此循环,得到一场的亮度差值绝对值总和。

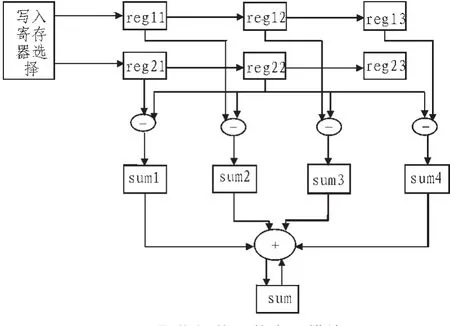

图6为聚焦评价函数实现模块。图中,聚焦评价函数实现模块读取的2行数据,由写入寄存器选择模块来选择中心像素所在行,写入第2列寄存器。在时钟同步作用下,每时钟将像素右移进入下一个寄存器,同时寄存器reg11,reg12,reg13,reg21中的数据同reg22中的数据作减法,取得差值sum1、sum2、sum3、sum4,相加得到和 sum。 当一帧图像结束,sum中的数据成为该帧的亮度差值和。当前帧计算的结果与前一帧的计算结果相比较,若当前帧的函数值大于前一帧的函数值,说明当前图像比前一帧图像清楚,则输出结果OUT为‘1’,反之则输出‘0’。

图6 聚焦评价函数实现模块Fig.6 Module of auto-focusing function realization

采用爬山搜索算法确定光学聚焦位置。在自动聚焦使能信号有效后,驱动马达从初始位置正转8步,反转8步,然后再反转8步,正转八步,回到初始位置。每转1步检测聚焦评价函数模块的输出out值,将4个8步内检测到‘1’的个数分别保存为 sum1、sum2、sum3、sum4, 接下来进行统计分析,如果sum1≥6,则认为正转方向为聚焦方向;若sum2≥6则认为反转方向为聚焦方向;如果sum1、sum2都未大于等于 6,则计算 sum1+sum4和 sum2+sum3;如果sum1+sum4≥sum2+sum3,则认为正转方向为聚焦方向,否则认为反转方向为聚焦方向。确定出聚焦方向后驱动步进马达带动镜头向聚焦方向一步一步转动,每转一步检测聚焦评价函数算法模块的输出OUT值,若连续转的2步输出out都为‘0’,则认为超过最清晰位置,则驱动步进马达倒退2步,镜头达到最佳聚焦位置。

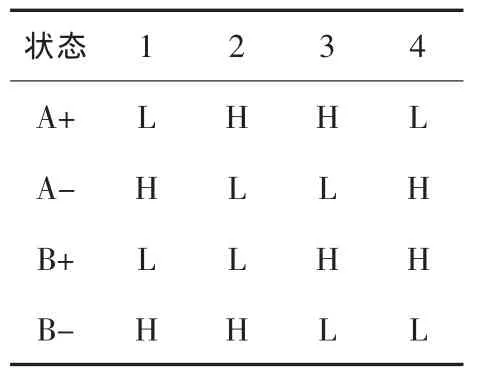

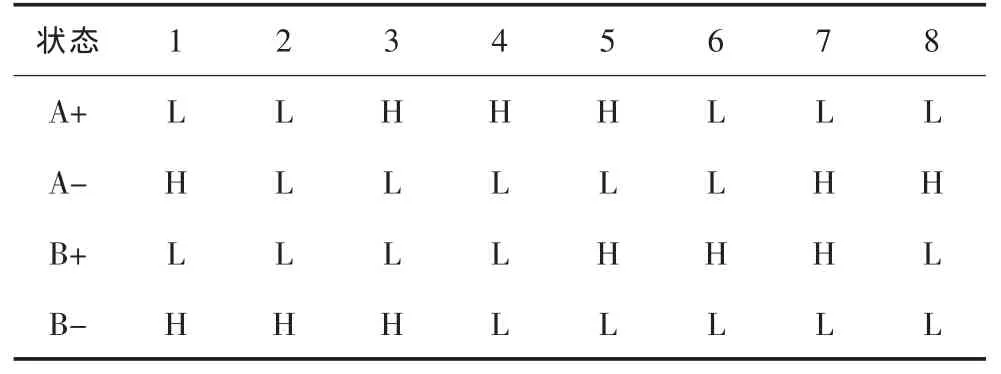

步进马达[5]驱动包括变焦马达驱动和聚焦马达驱动,变焦马达实现变倍,聚焦马达用来聚焦。变焦马达和聚焦马达的励磁方式不同,变焦马达采用2相励磁方式,见表1。聚焦马达采用的是1.2相励磁方式,见表2。其中A+、A-分别代表A相绕组正端和负端功率桥控制信号,B+、B-分别代表B相绕组正端和负端功率桥控制信号。按照表中所示的电平信号,外加在步进马达的两组线圈上,利用线圈间脉冲的相位差产生的扭矩来驱动马达步进工作。按照表中所示的脉冲顺序,从左向右变化可实现步进马达的反转;反之则实现正转。以变焦马达驱动为例,在FPGA内设计一个状态机,实现4个状态间的状态转移,每一次变倍使能有效时,根据当前状态转移,变倍方向转移到下一个相邻状态,输出该状态时对应的4个控制电平信号,驱动马达转动,实现变倍功能。需要注意的是,由于FPGA输出脉冲信号的驱动电平和电流与步进马达的驱动要求不匹配,应在FPGA输出引脚外接驱动桥电路。

表1 2相励磁方式Tab 1 2-phase excitation

表2 1-2相励磁方式Tab.2 1-2-phase excitation

1.4 自动光圈控制

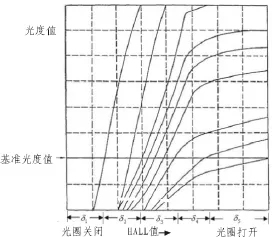

图像的亮度与外界光照和光圈有关。自动光圈控制是在特定光照度下,通过计算图像的亮度确定目标光圈孔径,从而得到曝光合适的图像。通过实验,给出光照度(对应图像亮度)与 HALL电压值(δ1~δ5)之间关系曲线,如图 7所示。 改变光圈孔径并计算相应图像亮度值,得到曲线上2点的坐标,便可确定对应当前光照度的曲线,曲线与基准光度值所对应直线的交点即是目标HALL电压值(目标光圈孔径)。

图7 光度值与霍尔值对应关系Fig.7 Relationship between illuminance and HALL-voltage

由于曲线是非线性的,在FPGA中通过建立查找表存储曲线。将横轴分割为δ1~δ55个区域,每个区域内可近似用直线表示,查找表中只要存储直线的斜率和起点坐标。光圈孔径值(对应电路HALL电压值)和对应光度值决定的2点即可确定当前的控制曲线。若光圈孔径值处在 的边界点,光圈马达应向该区域的内部运动,以便2次取点都是在同一区域,保证2次取点落在一条直线上。

确定了光度值曲线,就可以沿着曲线调整光圈的开度。基准光度水平线与已确定的光度曲线交点必然对应一个特定的光圈开度值(特定的HALL电压值)。在具体操作中,只需驱动光圈马达来改变光圈孔径,直至CPU得到指定的HALL电压值,即为最佳曝光状态。

1.5 OSD(On Screen Display)模块

OSD设计最重要的是视频鼠标,以SVGA格式下的鼠标显示为例。该模块首先利用40 MHz的主时钟产生符合VESA(视频电子标准化协会)标准的分辨率为800×600、帧频为60 Hz的标准SVGA格式的行、场同步信号,同时在行、场参考信号都有效时,产生一个使能信号给输出缓冲模块,作为输出缓冲的读使能。当行场计数器等于鼠标在屏幕中的坐标时,则显示鼠标,否则显示插值后输出的图像。

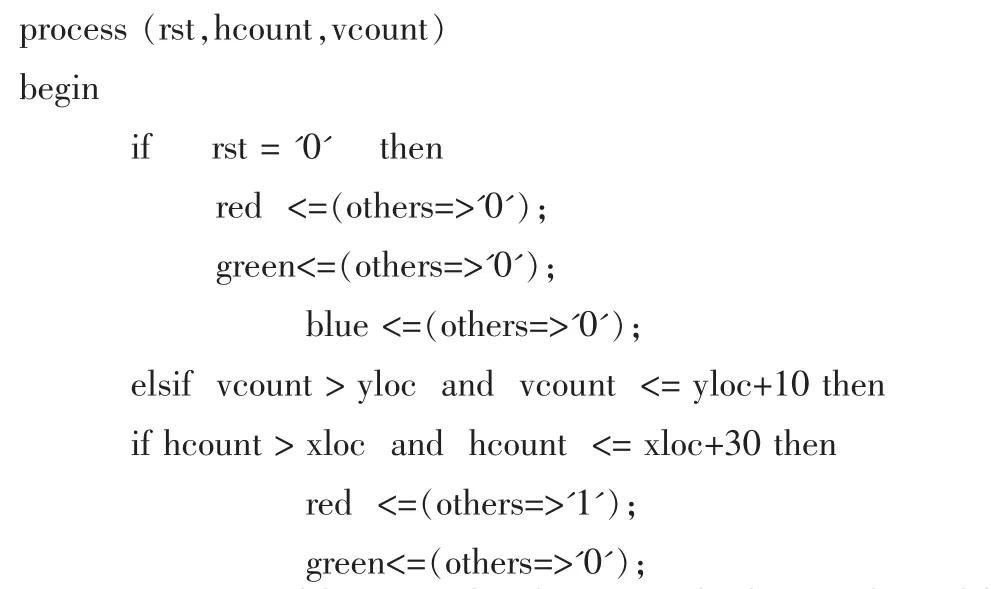

如将鼠标显示成一个红色的长方形,其长包含30个像素,宽包含10个像素,左上方为鼠标在水平和垂直方向的位移确定的坐标。该部分实现的VHDL描述为:

根据实际需要,还可将鼠标显示成其他颜色和形状,同时适合XGA等显示格式。

2 结 论

基于FPGA设计了具有多输出接口的一体化摄像机,采用FPGA实现了高分辨率图像的实时显示,增加了自动聚焦、自动光圈控制、图像冻结、负片显示、图形文本选择、彩色黑白选择、OSD显示等功能。并且FPGA还留有许多端口进行功能扩展。该系统设计把多种图像处理算法以及系统控制功能集成到单片FPGA中,使得视频输出同时具有3种输出接口形式,扩大了一体机的应用范围。该系统在硬件结构和FPGA内部逻辑功能实现方面都具有良好的可升级特性。在PCB设计过程中,应注意高速数字信号的完整性问题以及模数混合设计的噪声干扰问题[6],避免产生硬件设计带来的不良影响。

在进一步研究中,还可实现图像翻转等功能,并可以通过改进图像放大算法,以期得到更好的图像质量。该设计可应用到实时监控、数字视频展台等方向,具有实时性高、图像质量较好、功能可扩展等优点。

[1]范敦浩.图像监控系统摄像机和镜头的选择[J].通信电源技术,2003(4):23-27.FAN Dun-hao.The choosing of video camera and lens in surveillance system[J].Telecom Power Technologies, 2003(4):23-27.

[2]徐欣,于红旗,易凡,等.基于FPGA的嵌入式系统设计[M].北京:机械工业出版社,2005.

[3]孟宪元,钱伟康.FPGA嵌入式系统设计[M].北京:电子工业出版社,2007.

[4]任四刚,李见为,谢利利.基于灰度差分法的自动调焦技术[J].光电工程,2003,30(2):53-55.REN Si-gang, LI Jian-wei, XIE Li-li.Automatic focusing technique based on gray scale difference method[J].Opto-Electronic Engineering,2003,30(2):53-55.

[5]刘宝廷,程树康.步进电机及其驱动控制系统[M].哈尔滨:哈尔滨工业大学出版社,2003.

[6]Bogatin E.信号完整性分析[M].北京:电子工业出版社,2005.