基于FPGA嵌入式系统的研究与应用

2010-05-18崔健,刘晋

崔 健,刘 晋

(辽宁师范大学 计算机与信息技术学院,辽宁 大连 116081)

半导体工业和嵌入式领域所面临的主要课题之一就是设计片上系统,片上系统可以在单芯片上集成嵌入式CPU、DSP、存储器和其他控制功能,从而可大大降低产品的开发周期,提高产品的安全性、可靠性,缩小产品的物理尺寸,降低成本[1]。片上系统:(1)可以包含:微处理器,数字信号处理器,数字、模拟及混合电路模块,总线,时钟,电源分布,测试结构等;(2)支持标准的工业接口和通信协议。基于现场可编程门阵列器件(FPGA)的片上系统与基于ASIC的片上系统相比,具有风险小、开发周期短、成本低、可擦写等优点,是当今业界在快速原型技术和系统解决方案上的流行趋势之一。目前,FPGA器件不仅是逻辑门、布线资源和I/O可编程,而且随着半导体工艺的发展,在FPGA中还增加了许多硬件核,如存储器、时钟管理和算法功能,甚至增加了嵌入式处理器硬核和软核等,即在DSP和嵌入式处理器等关键领域发展可编程技术,FPGA已经成为在单片器件上同时提供可编程逻辑、高性能DSP和嵌入式处理器的系统芯片[2]。在密度和性能提高的同时,极大地降低了成本和功耗,使得FPGA在更多的应用领域成为市场的主流。

1 FPGA嵌入式系统

1.1 基本原理

FPGA其技术的关键在于用户可编程性,利用FPGA作为高度并行处理器件来设计嵌入式系统可以提供高信号处理的能力,满足样机开发周期短和产品上市快的要求,方便、快速地构造和仿真复杂的系统,根据用户需要的变化或设计出现错误时,可以随时升级或修改[3]。目前,围绕嵌入式系统展开研究和开发,已经成为计算机软、硬件技术发展最有潜力的方向之一。利用FPGA设计嵌入式系统已经成为制造业的核心技术,并广泛地应用到医疗仪器、系统仿真、工业控制、信息家电、通信设备等领域。本文在介绍FPGA作为设计平台实现嵌入式系统基本原理的基础上,研究了利用FPGA实现嵌入式系统的设计方法,并利用嵌入处理器软核,构造和裁剪嵌入式系统,在单个FPGA芯片上合理配置资源,实现多处理器的嵌入式系统。嵌入式处理器分为:嵌入式微处理器、嵌入式微控制器、嵌入式DSP处理器以及嵌入式片上系统等[4]。随着FPGA逻辑门密度的不断提高和设计工具软件的不断加强、优化,并出于对可编程的特性以及集成度等方面的考虑,以FPGA实现可配置的嵌入式系统已越来越广泛。FPGA已经从最初的可编程逻辑器件发展到当今的可编程系统,以其丰富的可编程资源成为系统设计的平台[5]。因此,基于FPGA的嵌入式系统设计方法实际上是一个基于可编程片上系统的设计过程。设计出来的是一种特殊的嵌入式系统:(1)它是片上系统,由单个芯片完成整个系统的主要逻辑功能;(2)它是可编程系统,具有灵活的设计方式,可裁剪、可扩充、可升级,并具备软硬件在系统可编程的功能。这种设计一般有如下特征:至少包含1个以上的嵌入式处理器IP Core;具有小容量片内高速RAM资源;丰富的IP Core资源可以灵活地选择;足够的片上可编程逻辑资源;处理器调试接口和FPGA编程接口共用或并存;可能包含部分可编程模拟电路;单芯片、低功耗、微封装。典型的基于FPGA的嵌入式系统如图1所示。

图1 基于FPGA的嵌入式系统结构示意图

1.2 性能分析

要实现各种应用领域的新的复杂算法,需要有更高性能的信号处理引擎。FPGA通过并行方式可以提供极高性能的信号处理能力,可编程的灵活结构降低了设计风险。对于不断更新和变化的标准和协议,可以通过移植设计来应对。FPGA支持DSP性能的主要机制与指令集结构的信号处理器完全不同,利用FPGA器件实现高性能的DSP功能是一种硬件实现数字信号处理的方法,因此,在处理速度上可以超过指令集结构的通用DSP。FPGA实现DSP处理时,其并行性使FPGA成为多引擎的乘法累加器,完全的并行性可以使数据的流量达到最大化。FPGA利用分布在器件内丰富的DSP资源来换取性能的提高,这些分布的DSP资源包括:查找表结构,可以实现组合逻辑、分布RAM和串行移位寄存器;嵌入式乘法器、进位链和乘法,专用于加速乘法运算能力;真正双口块RAM存储器的多种用途,可以与嵌入乘法器配对使用;多个具有更高乘法和累加性能的DSP处理片。

1.3 FPGA实现DSP的结构变换

FPGA实现数字信号处理,一般主要通过其硬件资源、算法变换和结构变换来体现[6],而其中的难点和关键也在于结构变换上,而FPGA突出的优点就是能够进行流水线和并行处理的结构变换。流水线处理是在数据通道中引入流水线寄存器来减少有效的关键路径,在增加时钟频率的情况下也增加采样速率;并行处理是利用重复的硬件来增加采样速率,使得多个输入可以并行地同时处理,多个输出可以在同一时间产生。

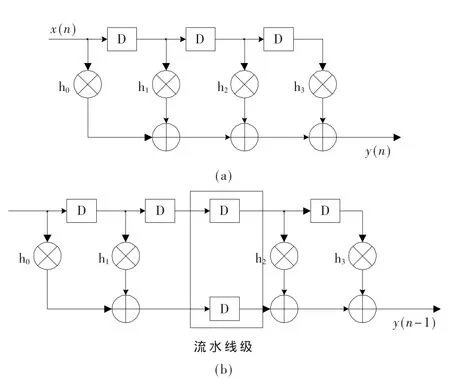

寄存器是流水线的每个功能部件所必须的[7],各流水段的时间应尽量相等,否则会引起流水线的阻塞和断流等。DSP算法的流水线转换时在数据通道中添加寄存器,这样使得算法可以进行流水线处理。例如在2个乘法运算单元之间放置1个寄存器,其关键路径可缩短一半,关键路径上的分布电容也可减少一半,从而使得电源电压可以降低,可相应地减少功耗。图2为2种形式的FIR滤波器,图 2(a)为直接形式的、N=4阶的 FIR滤波器,其输入数据的速率受限于关键路径的处理速度。关键路径包含3个加法和1个乘法,故其处理时间的迟滞为:Tcritical=Tmultiply+(N-1)Tadd。 其中,Tcritical为临界处理时间,Tmultiply为累加器处理时间,Tadd则为加法器处理时间。而图2(b)则是利用割集重新定义定时,在前馈割集边上添加寄存器,在输入输出的任何路径上延时元件的数目比原始的时序电路增加了数倍,从而实现流水线处理和运行。

图2 2种形式的滤波器

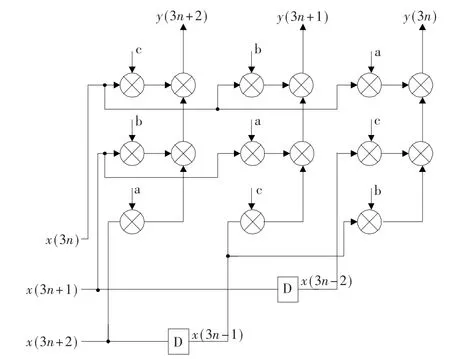

并行处理在结构上采用复制硬件的方法,几个输入并行地进行处理,在1个时钟周期内同时进行计算,并同时产生几个输出,因此采样率增加数倍,如二级并行处理结构则增加2倍的采样率[8]。在并行处理系统中,关键路径保持不变,如图3所示。时钟周期必须满足:Tclk≥Tmultiply+2Tadd,Tclk为符合要求的时钟周期。然而因为3个采样是在1个时钟周期内处理的,所以其迭代周期为:Titeration=Tsample=Tclk/L=(Tmultiply+2Tadd)/L。其中,Titeration为迭代周期,Tsample为采样周期,Tclk为在任意1路使用寄存器产生有效延时为L个采样率的时间。

图3 三阶并行处理结构

2 具体应用

图4 乘法累加驱动模式

如图4所示的乘法累加驱动的滤波器,实际上是一个简化的DSP处理器,其N个抽头的计算必须在采样周期T内执行,乘法累加的速率最小应是N倍的采样率,时钟速率必须比采样率更高。RAM需要与抽头一样多的字,其位宽由采样尺寸设定,而ROM则要满足系数要求。另外,采样和系数数据是每个周期都改变的,所以需要1个完全乘法器,其位宽是由采样数和最大系数尺寸设定。总之,滤波器的采样频率完全由处理全部滤波器组合所花费的时间来设定,即性能不是由器件的计算能力来决定,而是由存储器的带宽来限制。保持分布的RAM用来支持具有对称性的乘法累加驱动,带有1个预先加法器,由分布RAM提供系数。当数据写入时,总是向右移位,但是可以读进任何次序。单个译码器可以由几个查找表来形成,后半个或这个抽头则按照相反的次序读入,并输入到加法器。该译码器也保证奇数抽头滤波器的中间抽头没有任何数据加到它上面。存储器要输出2个操作数到乘法累加器,并且要顺序地读出这对数据,每2个存储器读出周期进行1次乘法累加操作,计算结果保持或存入存储器,以便累加器可以被复位并开始新的计算。

FPGA具有极高并行度的信号处理引擎,能够满足算法复杂度不断增加的应用要求,通过并行方式提供极高性能的信号处理能力。本文针对FPGA的特性,分析和研究了FPGA实现嵌入式系统的基本原理和实现方式,并通过应用来进一步解释和分析其设计实现过程。

[1]KAMAI R.嵌入式系统:体系结构、编程与设计[M].陈曙晖等,译.北京:清华大学出版社,2005.

[2]RANDALL S.Specification and design methodology for real-time embedded systems[M].Janka Kluwer Academic Publishers,2002.

[3]DESCHAMP J P, BIOULG J A, SUTTER G D.Synthesis of arithmetic circuits: FPGA, ASIC and embedded systems[M].Hoboken, John Wiley, &Sons, Inc.2006.

[4]JANTSCH A.Modeling embedded system and SoC:concurrency and time in modes of computation[M].Morgan Kaufmann Publishers,2004.

[5]刘明章.基于 FPGA的嵌入式系统设计[M].北京:国防工业出版社,2007.

[6]孟宪元,钱伟康.FPGA嵌入式系统设计[M].北京:电子工业出版社,2007.

[7]ATKINSON C.Component-based software development for embedded systems:an overview of current research trends[M].Springer Verlag New York Inc,2005.

[8]BAESE U M.数字信号处理的FPGA实现[M].刘凌,译.北京:清华大学出版社,2006.