基于MPC8568E的高性能通信处理器模块研究

2010-05-15潘晨昕周玉娟

潘晨昕,周玉娟

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

0 引言

随着IPv6技术的不断成熟及发展,它已经成为下一代网络的主要技术。由于IPv6协议的复杂性以及通信设备对CPU的处理能力要求越来越高,同时对通信协议、接口类型等要求也越来越强,迫切需要处理速度更快、性能更高的系统支持,为适应这一发展趋势,目前处理器厂商相继研发出速度快,集成度高的高性能通信处理器产品来支持下一代网络技术,在某课题设计中,应用FreeScale公司生产的PowerQUICC III MPC8568E处理器,它是目前电信和网络市场最先进的集成通信微处理器系统芯片之一,应用该芯片设计了高性能集成通信处理器模块,主要满足下一代网络应用对高性能通信处理器的需求,该模块也可以应用于复杂的协议处理系统及网络互连互通设计中。

1 MPC8568E芯片的硬件特性

MPC8568E具有很强的功能扩展能力,其内核为高性能的36位地址嵌入式PowerPC e500v2,时钟频率最高可达1.33GHz;2个增强的三速以太网控制器(eTSECs),支持10/100/1000M以太网/802.3网络协议;可灵活配置的高速缓冲存储器和可提供最大16G字节的主内存的内存控制器;32bit PCI控制器,支持66MHz的速率。与上一代PowerPC相比较,MPC8568E在芯片的内部集成了用于实现复杂协议处理的QUICC机和与IPSec应用相关的用于实现安全的安全机(SEC enginee)。

2 设计与实现

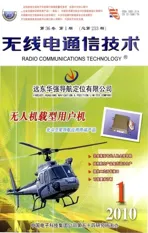

图1为高性能通信处理器模块的实现框图,该模块主要完成了以下功能:系统存储、10/100/1000M以太网接口、与IPSec应用相关的基于硬件的加密及解密功能、串口驱动器以及通过板间连接器实现的ATM、POS、以太网、PCI总线等的扩展功能。

图1 高性能通信处理器模块实现框图

2.1 高性能通信处理器模块的设计

MPC8568E是高性能通信处理器模块的主要芯片,所以它的外围芯片的选型及连接设计至关重要。MPC8568E的外部存储器件包括Micron公司的SDRAM存储器、DDR2 SDRAM存储器及Intel公司的flash。MPC8568E采用66MHz外部时钟,内核工作时钟频率不小于1.0GHz。SDRAM存储器挂接在MPC8568E的LOCAL总线,总线数据宽度为32位,主要完成数据的存储功能;DDR2 SDRAM存储器挂接在MPC8568E的DDR2 SDRAM控制总线上,总线数据宽度为64位,具有8位的ECC数据控制功能,主要完成数据的存储及实现QUICC机相关功能应用所需的表存储功能;64MB的FLASH存储器,用于存储操作系统内的引导程序、存储操作系统内核和数据掉电保存等功能。

MPC8568E的QUICC机外接MARVELL公司的88E1111 10/100/1000M以太网PHY芯片,可实现千兆以太网的接口功能。其他的ATM、POS、PCI总线等的扩展功能主要通过板间连接器实现。

2.2 QUICC机实现10/100/1000M以太网口

QUICC机是MPC8568E内部集成的功能模块,它是通用的通信集合体,集成了多个通信外围控制器,可提供在线系统设计并能够满足多种应用需求,特别是在通信与网络系统中得到了广泛的应用。通过系统片上(SoC)设计方法来实现设计结构的可扩展性。QUICC机应用SoC设计方法能够方便地应用在多种产品中,而只需设置不同的配置参数。应用多RISC内核扩展因子能够同时运行多个任务。而且由于它的频率及技术上具有可扩展性,因此它的性能可随着应用需求进行变化。

此外,QUICC机能够配置为单一RISC或双RISC通信处理机。对于较高性能的接入可配置为双RISC通信机而且也可以扩展到多RISC结构。

QUICC机内部包含了如图2所示的2个同样的组,每个组包含4个UCC。这2个组都可由RISC机控制。公共的多用户RAM可用于存储RISC机的参数,每个RISC有一个与其相联系的ROM,包含代码映像,通过指令RAM可有选择地用于运行附加代码。QUICC机主要包括:可支持256个通道的MCC;8个通用通信控制器(UCCs),支持以太网、UART、ATM、HDLC、QMC;2个UTOPIA/POS-PHY L2控制器(UPC);2个SPI控制器以及8TDMs的时槽分配器(TSA)及串行接口(SI)等。

图2 QUICC机模块单组结构图

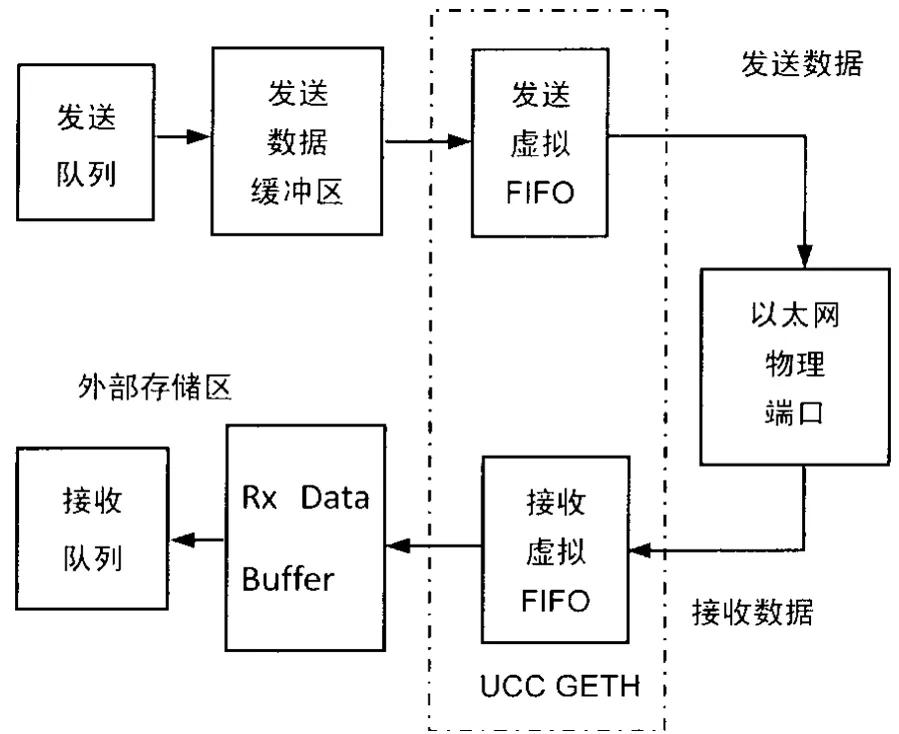

由于版面的限制,本节主要对通过配置QUICC机模块并外接88E1111实现的10/100/1000M以太网接口功能进行详细的介绍。图3为以太网的数据流框图,无论发送和接收方向的数据都主要流经3个模块:Data Buffer、UCC Virtual FIFO和physical port。数据流经过QUICC机UCC的路径需要将UCC配置为以太网的协议类型。其具体配置方法如下。

图3 UCC Ethernet Data Flow数据流框图

①设置必要的默认参数。包括maxFrameLength、numQueuesTx、numQueuesRx、typeOrLen、minFrameLength、vlanT ype、vlanTci、maxRxBufLength等寄存器的设置,例如maxFrameLength代表最大帧长度寄存器,通常将此值设为1 518;vlanType代表VLAN类型,建议设置为0x8100;

②设置buffer descriptor(BD)。最好设成标准的以太网格式,以TxBD为例,前16 bit代表BD的状态,中间16个bit代表数据长度,最后 32个bit代表传送数据缓存区的指针;

③设置寄存器的初始化参数及RAM区参数。包括GUEMR、UPSMR、MACCFG1、MACCFG2、IPGIFG、HAFDUP、MIIMCFG、CECDR、CECR、SQPTR、TSTATE、RQPTR、MRBLR、MFLR、MINFLR、RBDQPTR等寄存器,例如GUEMR控制UCC是工作在快速模式还是慢速模式,此寄存器中的第7位是URMODE,代表UCC接收模式,设置为0时,代表UCC接收被配置为低速协议,设置为1时,代表被配置为低速协议,此寄存器中的第8位是UTMODE,代表UCC发送模式,设置同URMODE;SQPTR,代表Base address of the send queue memory region,此值需根据 Tx buffer descriptor的需要进行设置;MRBLR,代表Maximum receive buffer length,通常将此值设为1 536;

④初始化并行口。此步骤是通过配置CPDIR1E、CPDIR2E、CPODRE、CPPAR1E、CPPAR2E等寄存器来实现。例如CPDIR1E的比特位分别为DIR0至DIR15,通过对这些比特位的设置来达到并行口初始化的目的;

⑤使能并进行数据的发送和接收,此步骤通过设置GUMR寄存器来实现。GUMR的第27位和第28位分别是ENR和ENT,将这两位置1即可。另外还可以通过将GUMR的DIAG位置1来设置环回。

3 结束语

高性能通信处理器的处理速度较快并且支持多种通信协议接口,为下一代网络技术的实现提供了通用的系统平台,本设计采用MPC8568E实现了高性能通信处理器模块,提供了多种通信接口,充分应用了其内部集成模块的功能,发挥了MPC8568E优秀的通信控制和处理能力,为今后实现更为复杂的协议处理系统及网络互连互通设计提供了方便,缩短了设备的研发周期。目前,本设计已在工程中得到应用,工作稳定可靠。

[1](美)Rich Seifert著.千兆以太网技术与应用[M].郎波等译.北京:机械工业出版社,2000.

[2]FreeScale Corp.MPC8568e PowerQUICC IIITM Integrated Processor Hardware Specification[S],2007.

[3]QUICC Engine Block Refernce Manual[S],2007.

[4]FreeScale Corp.MPC8568e PowerQUICC IIIIntegrated Processor Family Reference Manual[S],2007.