低功耗能量回收时钟发生器和触发器的设计*

2010-04-17蔡艳慧钟传杰

蔡艳慧,方 赟,钟传杰

(江南大学 信息工程学院,江苏 无锡 214122)

1 引言

在数字集成电路的设计中,时钟功耗是制约电路设计发展的重要因素。文献[1]中的一种高性能处理器的功耗分析表明,30%~50%的功率消耗在时钟分配网络(Clock Distribution Network,CDN)上。 因此,降低时钟分配网络功耗,成为降低电路功耗的关键。近年来,人们提出了一种由四相正弦时钟控制的能量回收时钟触发器——传输门能量回收时钟触发器(PGER)[2]。它能够利用设计能量回收时钟的方法来回收时钟分配网络中电容里存储的电荷。但其缺点是时钟信号产生电路复杂,增加额外功耗。同时,传输门的延迟时间较大,导致赋值时间减少[3]。Aliakbar Ghadiri等人提出了预取值静态脉冲触发器(PCSP)[4],其缺点是结构复杂,造成的版图面积增大。基于以上文献,笔者提出了静态差分能量回收触发器(SDER),可大大改善上述缺点。

门控时钟技术是另外一种降低时钟功耗的方法,近年来得到广泛应用[5-8]。传统的插入逻辑门的方法并不适合能量回收技术,因此笔者提出在触发器上添加时钟门控逻辑门。

2 能量回收技术与能量回收时钟发生器

2.1 能量回收技术

目前,降低功耗的设计思想主要有:减小电路的节点翻转因子,降低电源电压,减小负载电容,使用动态电源管理系统使系统在空闲时自动进入休眠状态。但是,这些方法从电源中吸收的能量在被耗尽之前只能被使用一次。为了减少能量浪费,使从电源中吸收的能量得到充分的利用,可引入再循环的措施。这就是另外一种降低功耗的方法——能量回收技术。能量回收电路利用交流功率时钟驱动,可以在整个工作过程中使导通器件两端的电压保持在很低的数值,从而降低了电路功耗[9]。

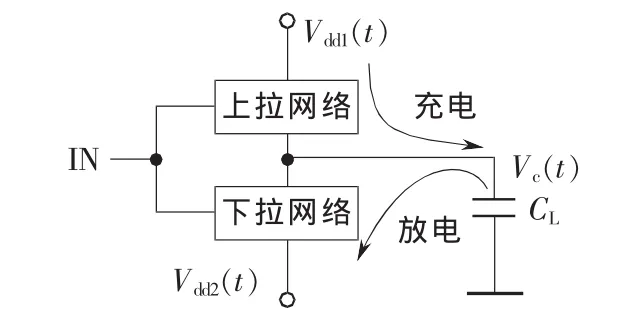

图 1 为静态逻辑电路能量回收过程。 Vdd1(t)和 Vdd2(t)均为可变电源。充电时,由于 Vdd1(t)缓慢上升,使 Vc(t)随着Vdd1(t)的变化而缓慢变化,减小两者之间的差值,从而减少消耗在上拉网络上的功耗。放电时,Vdd2(t)缓慢下降,Vc(t)随着 Vdd2(t)的下降而减小,这样消耗在下拉网络上的功耗也减小,从而使储存在CL上的能量回收到电源,反复使用,从而降低总功率的消耗。在同步数字电路中,由于时钟信号是容性信号,因此,在时钟分配网络中利用能量回收技术可以节省大量能量[11]。

图1 静态逻辑电路能量回收

2.2 能量回收时钟发生器

在数字集成电路中,时钟信号遍布芯片的每个角落。为了形象地描述它的分布和工作情况,提出了时钟树分布网络模型——集总π型RC模型。根据时钟树在芯片内的分布特征,将时钟分配网络定义为H树型结构。这是因为,H树型结构从时钟信号的起点到各个时钟终点的距离是相等的,时间理论上也相等,时钟偏差理论值应为0。能量回收时钟信号发生器通过H时钟树分配网络驱动触发器。

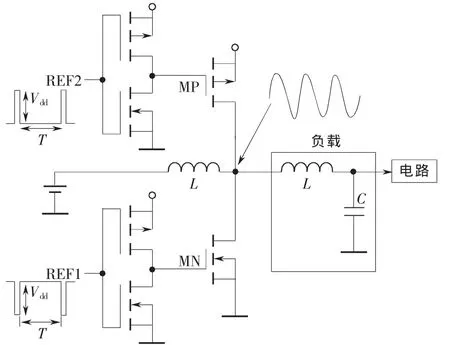

采用的能量回收时钟发生器是一个单相正弦振荡时钟发生器[12],如图2所示。之所以采用正弦信号波形,是因为正弦信号波形平滑,不在某个时刻发生突变,可以起到能量回收的作用。

图2 能量回收时钟发生器

能量回收时钟发生器由LC振荡电路、晶体管MP、MN和几个反相器组成。实际应用时,它的负载就是一个RC网络。DC供电电压为Vdd/2。晶体管MN,MP分别有参考信号REF1和REF2驱动。参考信号REF1和REF2频率相同,相位相差180°。当晶体管MN的参考信号REF1达到最小值时,MN作为电路的下拉管子把振荡信号拉到最小至0,这样可以保证振荡电路的幅值,因此这个管子的尺寸要相当大,而且有反相器驱动。为了使电路不受温度和工艺的影响,保证波形的稳定,大尺寸且受反相器驱动的MP起着至关重要的作用。当晶体管MP的参考信号REF2达到最大时,激活上拉管子MP,使时钟信号的振幅拉到 Vdd。

时钟发生器的振荡频率为

式中:C为连接时钟树的总电容,包括时钟树的寄生电容和触发器时钟的输入电容;L为集总电感。为了得到C值,需要仿真时钟发生器和触发器。首先给出L值,得出电路的固有频率f0,然后求出C值。L值要根据需要的频率来确定。

3 静态差分能量回收触发器和门控时钟技术

3.1 电路结构

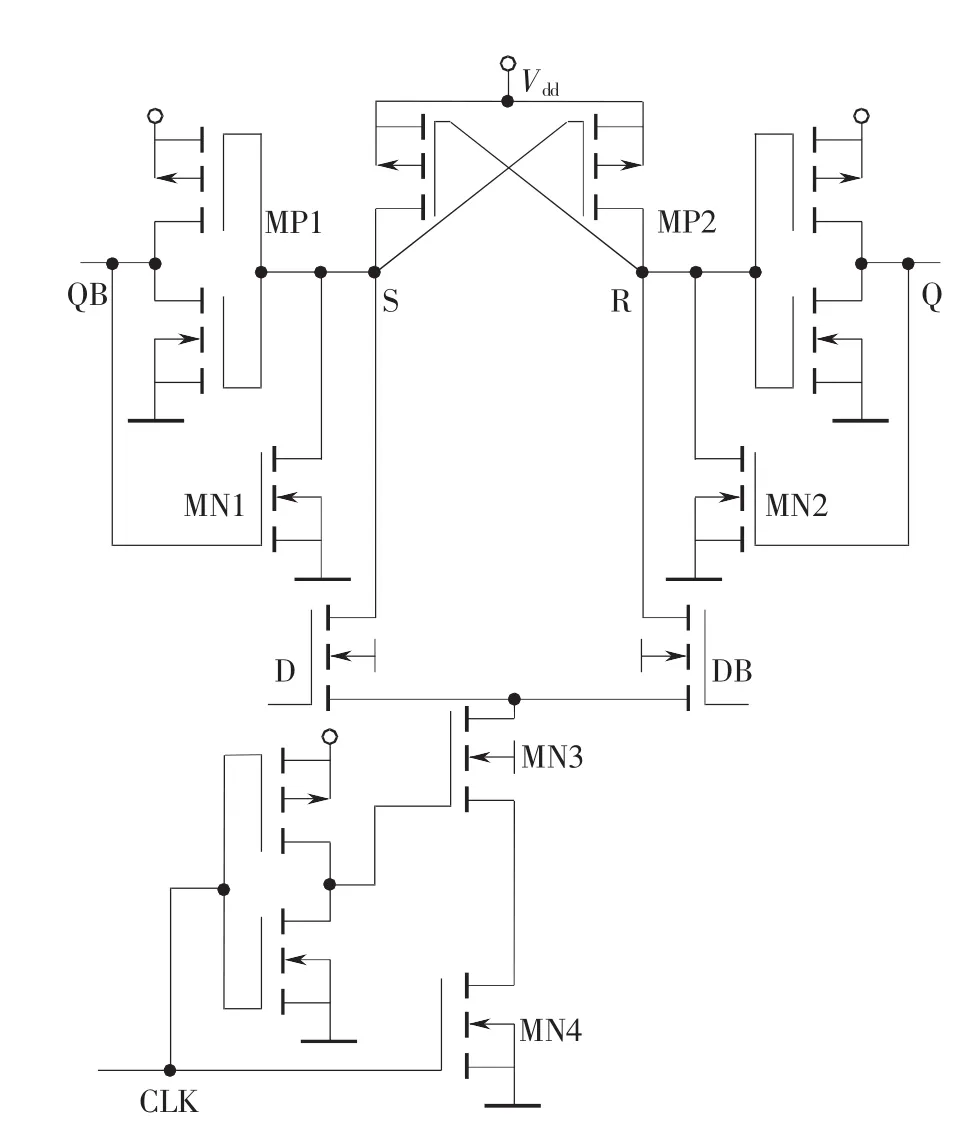

图3为静态差分能量回收触发器(SDER)。该电路为比例逻辑电路,主要由 MP1、MP2、MN1、MN2、MN3、MN4、反相器等组成。差分逻辑要求每一个输入信号都有相应的互补信号作为另一个输入,并且产生一对互补的输出信号,同时也使电路很容易上拉到Vdd。输出的正反馈保证了在不需要电路工作时,把负载PMOS管关掉,这样有效地降低了静态功耗。S和R节点经过输出缓冲器分别输出信号QB和Q。触发器的输出Q和QB分别反馈给接地的MN2和MN1,这样设计可以避免内部节点S和R受干扰,使输出信号稳定。电路的另一个特点在于减少电荷分享的2个接地的管子MN3和MN4。在电路的赋值阶段,为了减少电路的电荷分享降低功耗,把MN3和MN4的参数设置得很大,并把MN3和MN4接地。时钟信号CLK为正弦信号波形,它直接控制MN4和经过反相器以后控制管子MN3。MN3和MN4为串联的NMOS管,理想情况下,MN3和MN4不可能同时导通,但是在实际的电路中,时钟信号CLK经过反相器后总会有时间的滞后,这就形成了必定使MN3和MN4同时导通的短脉冲。

图3 静态差分能量回收触发器

电路的工作过程简单介绍如下。当时钟信号CLK上升沿到来,并达到管子的阈值电压,且D=1,MN4导通取值,由于反相器的作用,存在短的高电平脉冲使MN3也导通,下拉网络有足够的下拉能力把节点S下拉到低电平,从而使MP2导通。由于DB=0,节点R到地之间没有通路,所以输出Q和QB分别为低电平和高电平。这时MP1截止,节点S继续下拉,且由于MP1截止,不再有静态电流从Vdd流到地,从而降低了静态功耗。

3.2 门控时钟能量回收时钟触发器

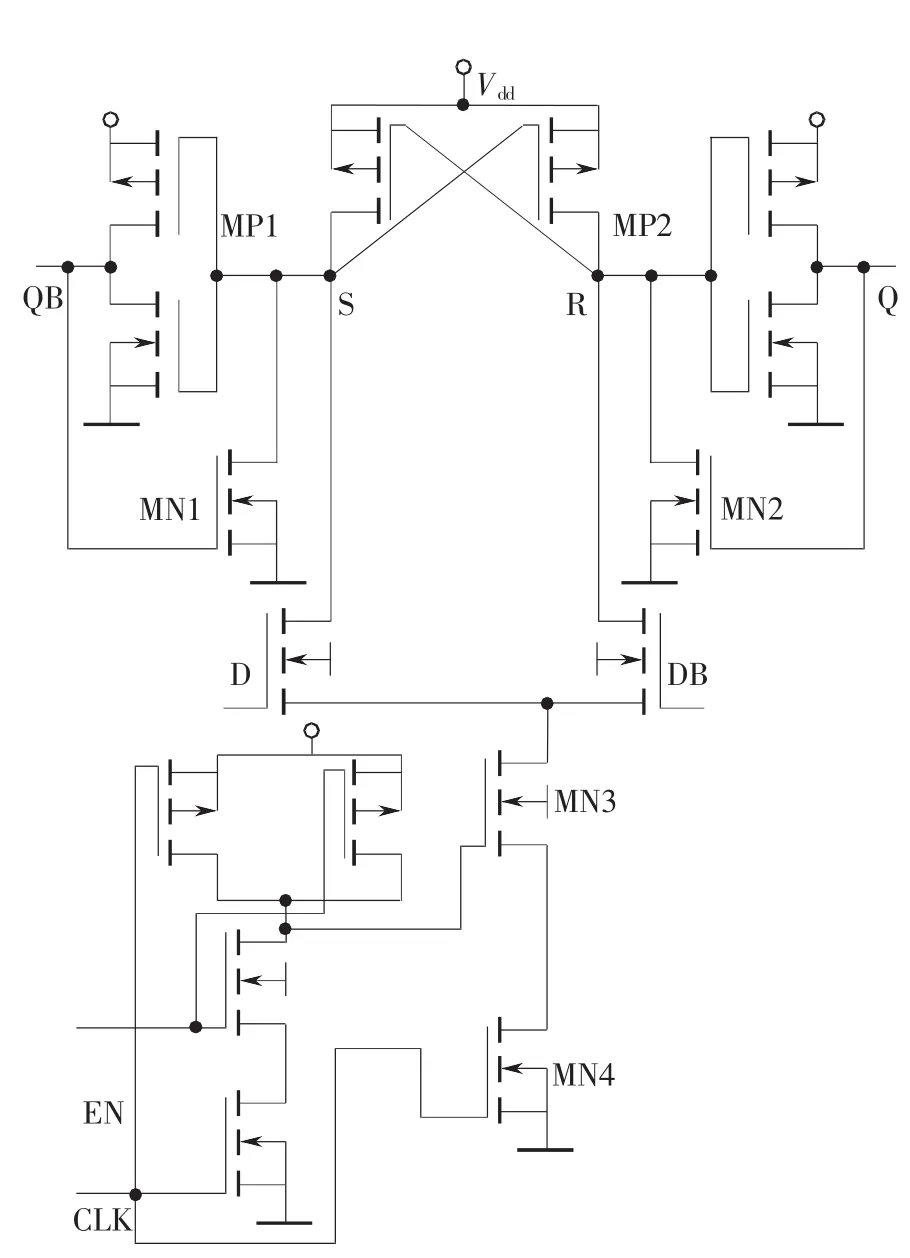

在系统的睡眠状态,门控时钟技术是降低功耗的好方法。时钟网络包括两个部分,一部分是由时钟缓冲器组成的时钟树本身,另一部分是时钟树节点所驱动的为数众多的寄存器。相对于方波时钟,门控时钟技术在能量回收电路中的应用要讲究得多,这是因为在正弦时钟网络中插入逻辑门会破坏波形,从而减少能量回收电路回收能量。这里,提出的门控时钟技术如图4所示。

门控时钟技术使用的或非逻辑门来取代图3所示的反相器[12]。或非逻辑门有2个输入:时钟信号CLK和使能信号EN。在激活模式下,使能信号EN=0,或非门相当于一个反相器。在睡眠状态下,使能信号EN=1,即使CLK=1,或非门的输出也为0,从而避免触发器工作。

4 仿真结果和比较

图4 门控时钟能量回收时钟触发器

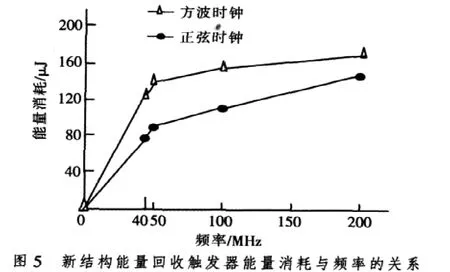

为了更好地说明能量回收技术的优点,分别对2个单元电路进行局部仿真。一个是带有能量回收的单元,即利用设计的时钟发生器通过H时钟树分配网络来驱动触发器;另一个是不带有能量回收的单元,即利用方波时钟信号通过H时钟树分配网络来驱动触发器。这2个单元电路均是在SMIC 0.35 μm CMOS标准工艺下实现,供电电源为3.3 V,温度为27℃,用Spectre软件仿真。用HSPICE从版图中提取寄生电容的网表,所有触发器的输出负载电容取为30 fF。图5为提出的能量回收时钟触发器有能量回收和无能量回收能量消耗与频率的关系。

从图5可以看出,随着频率的增加,回收能量的幅度有所下降,如果频率特别大,能量回收电路将无优势而言。当时钟频率为40 MHz时,方波时钟控制的触发器消耗的能量为133.7 μJ,而正弦时钟控制的触发器消耗的能量仅为76.4 μJ,同比下降了42.86%;当时钟频率为200 MHz时,方波时钟控制的触发器消耗的能量高达181.6 μJ,而正弦时钟控制的触发器消耗的能量为150.8 μJ,同比下降幅度约为17%。

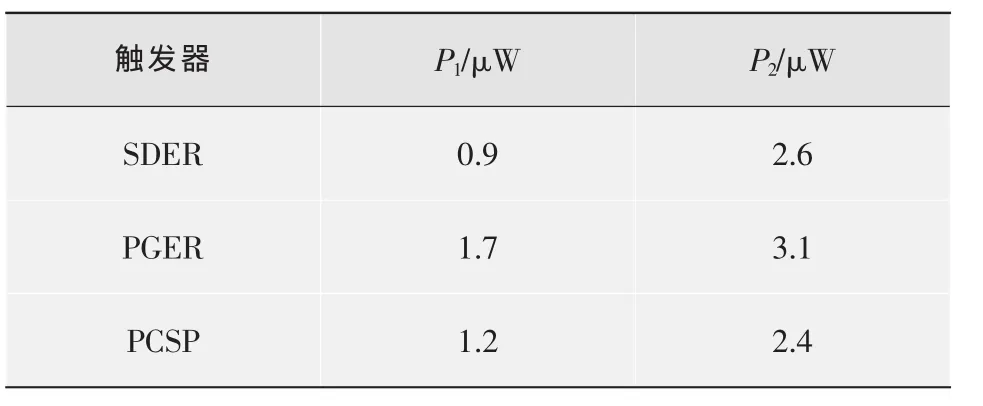

门控时钟技术的应用,对降低触发器的功耗起到了很大作用,特别是在系统睡眠状态下。在睡眠状态下,50%数据转换行为时,分别对各触发器仿真,功耗结果如表1所示。其中,P1表示利用门控时钟技术的功耗,P2表示没有利用门控时钟技术的功耗。

表1 利用门控时钟技术前后各触发器系统功耗情况

时钟频率为40 MHz,数据转换行为50%时,新型触发器和传统触发器利用能量回收技术和不利用能量回收技术情况比较如表2所示。其中,P3表示利用能量回收技术的功耗,P4传统代表没有利用能量回收技术的功耗,t表示延时。

表2 利用能量回收前后各触发器功耗、管子数和延时比较

由表2得知,时钟频率为40 MHz,50%数据转换行为时,SDER常规情况下需要消耗133.7 μW,而利用能量回收技术以后功耗仅为76.4 μW,同比下降了42.86%。PGER需要消耗的功率最大,为147.1 μW,而PCSP消耗的功率最小,仅为112.4 μW。和SDER相比,PGER和PCSP利用能量回收技术功耗下降幅度较小,分别为39.29%和28.29%。虽然PGER的管子数最少,只有4个,但其致命的是延时较长,约为SDER的2倍。PCSP则需要24个管子,比SDER多用了10个管子,需要较大的电路板面积。

5 小结

笔者针对如何降低功耗问题展开讨论,提出适用于能量回收技术的正弦时钟发生器结构和静态差分能量回收触发器。在SMIC 0.35 μm CMOS标准工艺下,利用Spectre软件仿真的结果表明,利用能量回收时钟触发器与传统技术相比,功耗下降幅度达到42.86%,延时也降低了约31%。系统睡眠模式下,提出对触发器添加门控时钟逻辑门,功耗下降了约65%。因此,能量回收和门控时钟技术大大降低了时钟分配网络的消耗,同时,对设计高性能、低功耗、高速度的计算机系统有很大的推动作用。

[1] 常晓涛,张明明,张志敏,等.应用于片上系统中低功耗IP核设计的自适应门控时钟技术[J].计算机学报,2007,30(5):823-830.

[2] VOSS B,GLESNER M.A low power sinusoidal clock[C]//Proc.the 2001 IEEE International Symposium on Circuits and Systems.Sydney,Australia:IEEE Press,2001:108-111.

[3]MAHMOODI H,TIRUMALSHETTY V,COOKE M,et al.Low-power clocking scheme using energy recovery and clock gating[J].IEEE Trans.Very Large Scale Integration (VLSI) Systems,2009,17(1):33-44.

[4] GHADIRI A,MAHMOODI M.Pre-capturing static pulsed flip-flops[C]//ISCAS 2005.[S.l.]:IEEE Press,2005:2421-2424.

[5] WU Q,PEDRAM M,WU X.Clock-gating and its application to low power design of sequentialcircuits[J].IEEE Trans.Circuits and Systems,2000,47(3):415-420.

[6] HOU L,LUO R,WU W.Low power grating detection system chip for high-speed low cost length and angle precision measurement[EB/OL].[2010-03-20].http://cat.inist.fr/?aModele=afficheN&cpsidt=18885606.

[7]TROYA A,MAHARATNA K,KRSTIC M,et al.Low-power VLSI implementation of the inner receiver for OFDM-based WLAN systems[J].IEEE Trans.Circuits and Systems,2008,55(2):672-686.

[8]VISWANSTH V,VASUDEVAN S,ABRAHAM J A.Dedicated rewriting:automatic verification of low power transformations in RTL[C]//Proc.2009 22nd International Conference on VLSI Design.New Delhi,India:IEEE Press,2009:77-82.

[9]ZIESLER C H,JOOHEE K,PAPAEFTHYMIOU M C.Energy recovering ASIC design[C]//Proc.IEEE Computer Society Annual Symposium on Energy Recovering ASIC Design,2003.[S.l.]:IEEE Press,2003:133-138.

[10]SUHWANK,ZIESLERCH,PAPAEFTHYMIOUMC.Charge-recovery computing on silicon[J].IEEE Trans.Computers,2005,54(6):651-659.

[11]GHADIRI A,MAHMOODI H.Comparative energy and delay of energy recovery and square wave clock flip-flops for high-performance and low-power applications[C]//Proc.the 15th International Conference on Microelectronics.[S.l.]:IEEE Press,2003:89-92.

[12] TIRUMSLASHETTY V,MAHMOODI H.Clock gating and negative edge triggering for energy recovery clock[C]//Proc.IEEE International Symposium on Circuits and Systems,2007.New Orleans,LA,USA:IEEE Press,2007:1141-1144.