基于FPGA的嵌入式图像边缘检测系统设计

2010-04-17甘振华

甘振华,应 骏

(上海师范大学 信息与机电工程学院,上海 200234)

1 引言

Sobel边缘检测算法是分析视频图像场景的常用算法,应用于诸多领域,如安全监控、人工智能和计算机图形学等。数字图像处理常用的硬件平台是嵌入式DSP系统和专用集成电路(ASIC)。随着网络多媒体和通信技术的发展,数字图像携带的信息量也在不断增加,传统的DSP技术难以满足图像处理的实时性要求,而ASIC由于不够灵活,在图像处理领域的运用也比较少。近年来,FPGA技术快速发展,具有高效的并行处理能力,可采用流水线技术来设计,处理速度与DSP系统相比可提高100倍以上,因此采用FPGA来搭建数字图像处理平台有其独特的优越性[1]。鉴于此,笔者提出用FPGA设计嵌入式图像边缘检测系统。

2 Sobel算子

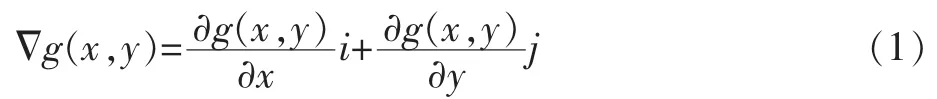

图像 g(x,y)的梯度定义为

梯度的模为

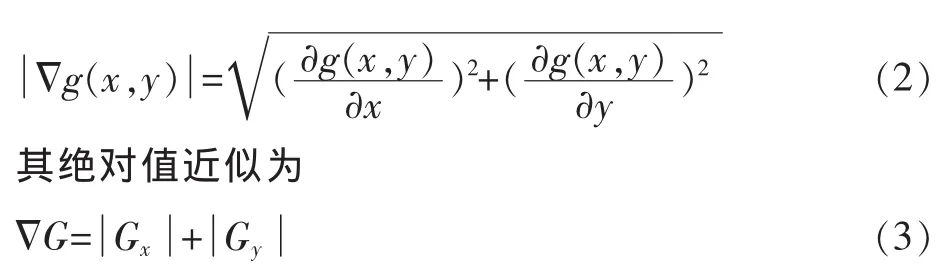

Sobel算子对图像的每个像素以检测像素点为中心,使用如图1所示的卷积模板来计算导数值Gx和Gy。当ΔG≥T时,在该位置的像素是一个边缘像素,其中T是一个指定的阈值。Sobel算子的本质是一种改进的梯度算法,相当于进行一次平滑滤波处理,实现了除噪。

图1 x方向和y方向的卷积模板

3 系统结构设计

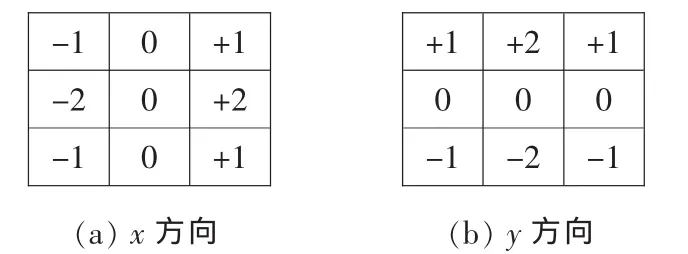

系统基于Altera公司的Cyclone系列芯片中的EP1C12Q240C8型FPGA和TMS320C55x系列DSP处理器,设计采用OpenCores制定的Wishbone总线,其位宽为32 bit,时钟频率为100 MHz。加速器是嵌入式系统中为高速执行某些操作而设计的专用定制硬件,它可以进行直接内存访问(Direct Memory Access,DMA),也就是在内存中自主存取数据,不需要处理器来发起内存访问,从而大大提高了传输速度。加速器既可以作为主模块向CPU发起访问总线的请求信号,也可以作为从模块来响应处理器对其进行的操作。为了能与嵌入式软件互动,加速器应自带控制寄存器,处理器只需给控制寄存器提供起始内存地址,加速器便能自动执行任务。由于加速器和处理器共享对内存的访问通路,而内存同一时刻只能执行一次访问,因此需在系统中设置一个仲裁器(arbiter)来确保子系统能够轮流访问内存[2]。嵌入式Sobel边缘检测系统的总体框图如图2所示[3-4]。

图2 系统总体框图

其工作过程如下:存储在主机中的原始图像信号通过总线传输到处理器,处理器在接收到来的图像信号时,并不对图像进行处理,而是给Sobel加速器的控制寄存器提供起始内存地址。与此同时,加速器向仲裁器发起访问总线的请求信号(request),当处理器向加速器写完基地址后,仲裁器便给加速器发出准许信号(grant),此时加速器则占有总线使用权,便可以按照DMA的方式在内存中读写数据。根据处理器放入加速器控制寄存器的地址,用加速器本身携带的计数器可以产生DMA所需的后续地址电路。图像数据经过输入FIFO缓存,然后经过Sobel加速器处理,产生的导数数据,经过输出FIFO缓存,以DMA的方式把导数数据写入内存。与此同时,处理器向仲裁器发起访问总线的请求信号,当加速器处理完一幅图像数据后,仲裁器便给处理器发出准许信号,此时处理器则占有总线使用权,等待下一次处理。

4 Sobel边缘检测的硬件设计

4.1 Sobel算子的并行处理设计

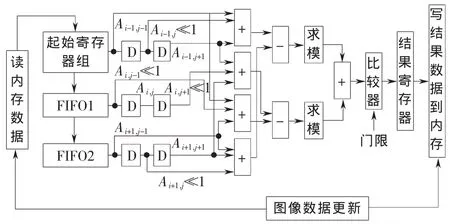

加速器是嵌入式系统中的一部分,如何最大限度地减少其占用的内存带宽,提高与系统的互动性,是需要考虑的问题。本设计处理的图像的分辨力为640×480,图像每像素到达需要100 ns,存储原始图像和导数图像的内存位宽为32 bit,内存每次读写需花费20 ns,则读写每个像素并存储到内存中,会消耗可用内存带宽的20%。若把4个像素值合起来,用一次读写操作来存储这些像素,消耗的可用内存带宽减少到5%[2]。由Sobel边缘检测算法可知,原始图像的像素一旦被读取,就可以用来计算像素相邻域的导数值,为使每计算4个像素只读取1次,可在数据输入端设置1个4×8寄存器组和2个FIFO来存储从主存中读取的前2行像素,并设计一个地址产生电路来更新图像数据。Sobel算子并行处理框图如图3所示。其中乘法器用加法、减法和移位代替,Ai,j为要计算的像素点[5]。

图3 Sobel算子并行处理框图

Sobel算子流水线过程如下:首先将图像数据的第1行,第2行分别读入2个FIFO中,然后从内存中逐次读取图像第3行的4个像素点到起始寄存器组中,并行输出3行图像数据,由9个D触发器进行时延,形成3×3像素窗口数据。由于FIFO可同时进行读写,FIFO1和FIFO2在读出数据时,将分别写入起始寄存器组读进的数据和FIFO1读进的数据,以便重复利用内存读入的数据。根据并行处理的特点,起始寄存器读取数据的同时,边缘值计算模块也开始工作,计算输入的窗口数据,产生结果像素值,送入4×8结果寄存器组,经4个计算周期,结果寄存器组中4个像素值都准备好后,随即被写到内存中。当计算到一行的结尾时,流水线中有3个像素值,结果寄存器组中有4个像素值,此时应把4个结果像素值写入内存,忽略起始寄存器组读操作,执行4个计算周期排出流水线中的3个像素值,并利用嵌入式软件将最后排出流水线的结果像素值清0。同理,由于一行最左边位置的像素也没有一组完整的相邻像素点,所以也用嵌入式软件对其清0。

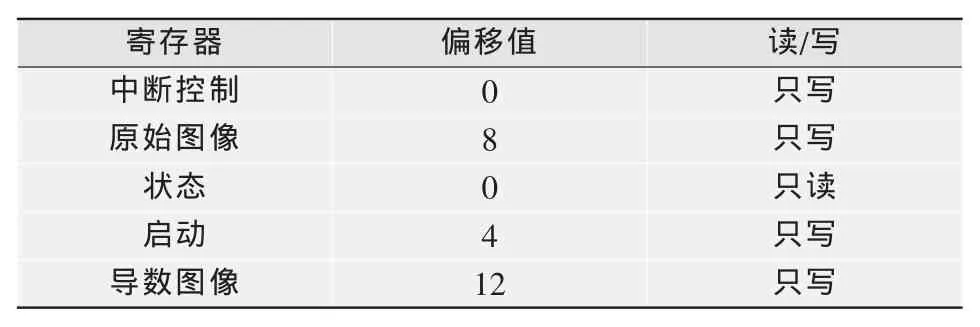

在电路设计中,为使嵌入式软件控制加速器提供同步,需在加速器的设计中添加控制寄存器和状态寄存器,为简化总线接口,把这些寄存器映射到32位地址总线的相邻地址,其寄存器地址映射如表1所示。当处理器把启动偏移地址写入启动寄存器时,加速器便开始工作,状态寄存器的第0位是完成标志位,当处理器处理完一幅图像时,将该位设置为1,其他位读为0。如果此时中断使能位也为1,加速器便发出中断请求。

表1 Sobel加速器的寄存器地址映射表

4.2 仿真结果与分析

本文用Verilog HDL语言编写程序,在Quartus II 9.0中进行编译,在ModelSim SE 6.1f平台下进行仿真,结果如图4所示。原始图像和导数图像存储地址分别为0000600016和0005000016,Sobel加速器寄存器基地址为20000016。系统复位后,处理器执行总线写操作,对加速器进行初始化,将地址、数据和控制信号分别从cpu_adr_o和cpu_dat_o写到sob_adr_i和 sob_dat_i。完成初始化后,处理器让出总线使用权给加速器,启动加速器,其对应地址为20000416。在光标处,开始读取原始图像数据,每次读取4个像素点值,每隔32 bit读取1次,由总线bus_dat_o写到sobel_dat_i,再由sobel_dat_i传输给寄存器组curr_dat_o,计算当前读出的数据与FIFO1和FIFO2中开始存储的数据,计算结果写到result_dat_i,阈值门限为110。从仿真结果中可以看出,设计达到了所需的要求。

5 小结

FPGA与嵌入式技术相结合,已经在很多工程领域得到了广泛应用,目前嵌入式图像处理正向着高速、微型化方向发展[6]。鉴于此,笔者设计了基于FPGA的嵌入式边缘检测系统,并成功地进行了仿真。结果表明,该嵌入式Sobel边缘检测系统对图像进行边缘检测速度非常快,在100MHz的时钟频率下,计算1个像素点只需40ns,计算1幅640×480×8 bit的图像只需12.8 ms,其处理速度比DSP提高了2个数量级以上,完全可以满足图像实时性的要求,具有一定的实用价值。

[1] HUSSMANN S,THIAN H H.A high-speed subpixel edge detector implementation inside a FPGA[J].Real-Time Imaging,2003(5):361-368.

[2] ASHENDEN P J.Digital design:an embedded systems approach using verilog[M].[S.l.]:Morgan Kaufmann,2007.

[3] KALOMIROS J A,LYGOURAS J.Design and evaluation of a hardware/software FPGA-based system for fast image processing[J].Microprocessors and Microsystems,2008,32(2):95-106.

[4] 初秀琴,曾祥永.一种新型的实时图像处理机结构及Sobel电路设计[J].仪器仪表学报,2003,24(5):508-511.

[5] KORNAROS G.A softmulti-corearchitecture for edge detection and data analysis of microarray images[J].Journal of Systems Architecture:the EUROMICRO Journal,2010,56(1):48-62.

[6]BOURIDANE A,CROOKES D,DONACHY P,et al.A high level FPGA-based abstract machine for image processing[J].Journal of Systems Architecture,2007,31(8):809-824.

甘振华(1987-),硕士生,主研嵌入式系统,视频处理;

应 骏(1973-),博士,硕士生导师,主要研究方向为嵌入式系统、视频处理。