在FPGA上实现视频码流的信道编码与扩频过程

2010-04-11郝红

郝 红

HAO Hong

(青岛港湾职业技术学院,青岛 266404)

在FPGA上实现视频码流的信道编码与扩频过程

In the FPGA to achieve video stream of the process of channel coding and spread spectrum

郝 红

HAO Hong

(青岛港湾职业技术学院,青岛 266404)

本文分析了在高性能FPGA上实现视频码流的信道编码与扩频过程,所用FPGA为美国ALTERA公司的EPM7512AEQI208-10,在整个图像编码过程中主要实现了对串行的视频码流的相应处理,主要包括:I、Q分路、差分编码、格雷编码及扩频调制,最终完成了中频发射单元FPGA程序的研制。通过整机的调试及多次检验,证明了系统性能的优越性,达到了国内同类产品的较高水平。

FPGA;信道编码;扩频

0 引言

扩频通信技术是当今通信系统中的一个主流,以其诸多优点在各个通信领域里面得到了广泛的应用,本文的图像编码传输过程就是基于移动通信中的扩频通信技术,所用FPGA为美国ALTERA公司的EPM7512AEQI208-10,在整个图像编码过程中主要实现了对串行的视频码流的相应处理,主要包括:I、Q分路、差分编码、格雷编码及扩频调制,最终完成了中频发射单元FPGA程序的研制。

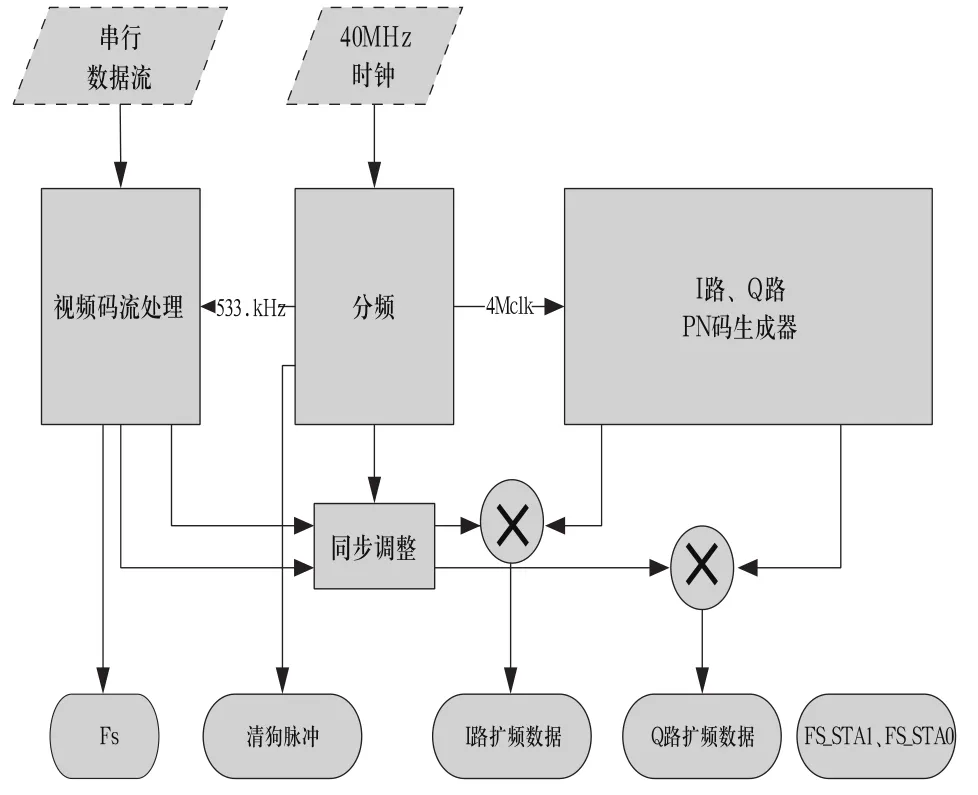

图1 中频发射单元信号流程图

1 中频发射单元FPGA程序设计

1.1 中频发射单元FPGA程序运行流程

中频发射单元的运行流程如图1所示。FPGA上电程序加载完毕后,中频发射单元开始运行:首先对输入的40MHz的基准时钟进行10分频,降为4MHz,再将4MHz的时钟分成四路,两路作为码时钟分别送到I路和Q路的PN码发生器,一路送到计数器产生40ms的清狗信号,一路经过7.5分频降为KHz,再次分成两路,一路作为同步Fs信号计数器的时钟,一路2分频后,作为I路和Q路的串行码采样时钟。

PN码是由本地产生的,采用八级移位寄存器,序列长度为255,码速率为4Mbps,具有较好的互相关系数和较强的随机性。

1.2 视频串行数据流的处理

当视频串行码流输入后,首先要用正交分路将数据分为I、Q两路。外部输入的视频串行码流的码速率为kbps,对该串行码的采样周期为串行码码片周期的二倍,即为串行码时钟的二分频。这样串行码流就分别在采样时钟的上升沿和下降沿被分成I、Q两路。

然后分别对I路、Q路进行差分编码和格雷编码,最后用本地产生的PN码进行扩频,最终将处理过的I、Q两路扩频数据输出给发射通道单元完成串行码的QPSK调制。

2 中频发射单元FPGA程序说明

2.1 差分编码模块

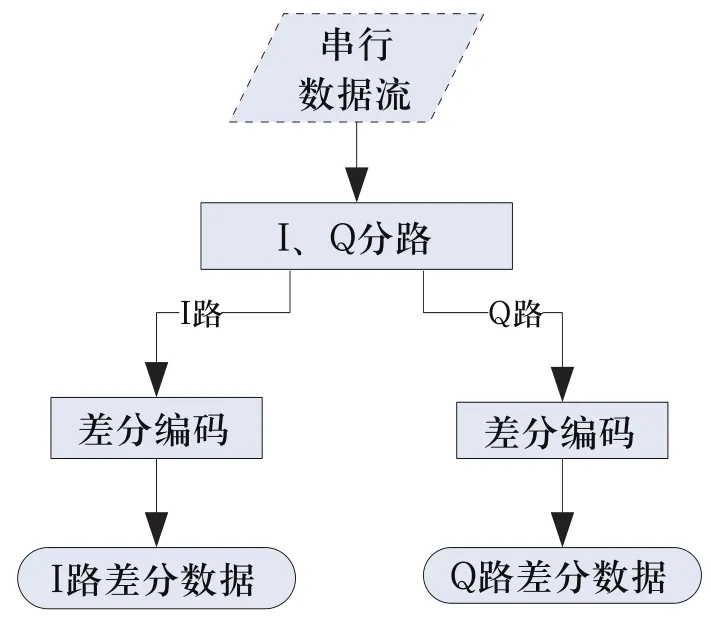

图2 差分编码模块程序流程图

差分编码模块程序程序图如图2所示,串行数据流输入后先进行I、Q分路,然后再分别对I、Q两路数据进行差分编码。差分编码:差分编码是I路或Q路的输入数据延时1比特,再与自身进行异或,最后把结果传给下一级格雷编码模块进行处理。

2.2 格雷编码模块

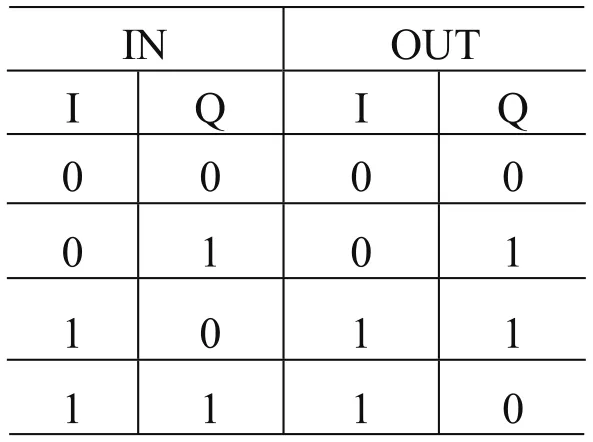

图3 格雷编码模块程序流程图

图3所示为格雷编码模块程序流程图。格雷编码是对I、Q两路同时进行编码。格雷编码是对I、Q两路同时进行编码,其基本原则是相邻十进制数编码以后的二进制码字只有一位不同,具体码映射如表1所示:

表1 格雷码映射表

格雷码通常用于数据变化较慢或者比特错误率比较低的系统或通信链路中,在输出数据变化慢的场合,如本发射单元所处理的串行数据流,格雷码具有很好的检错性能,如果在解码时发现相邻的数之间有多余两位的变化,则接收电路会认为数据传输出错。

2.3 PN码生成模块

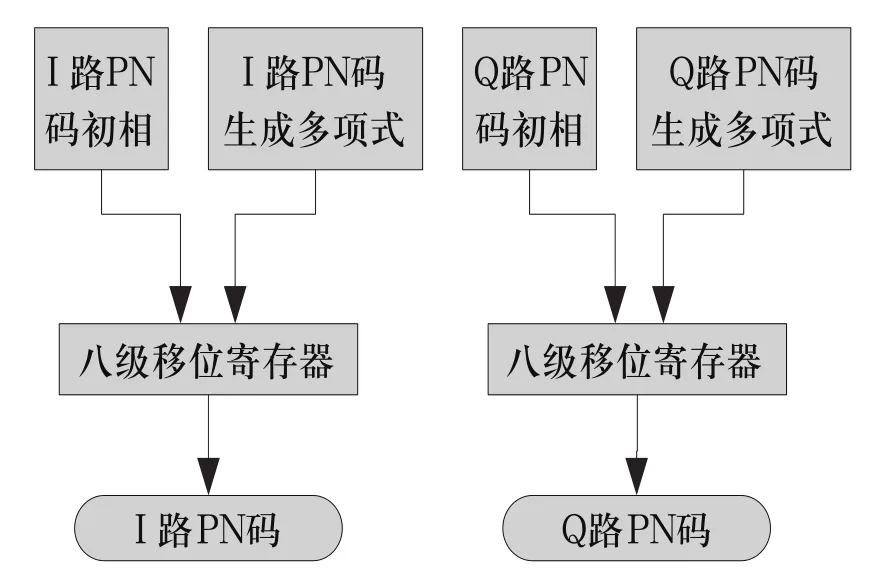

图4 PN码生成模块程序流程图

图4所示为PN码生成模块程序流程图。PN码由本地产生,做为串行码的扩频码。码时钟上升沿触发产生I路PN码,下降沿触发产生Q路PN码,故 Q路PN码要比I路PN码延时半个码片周期。

码时钟是由输入的基准时钟信号10分频后得到的,频率为4MHz,占空比为50%。

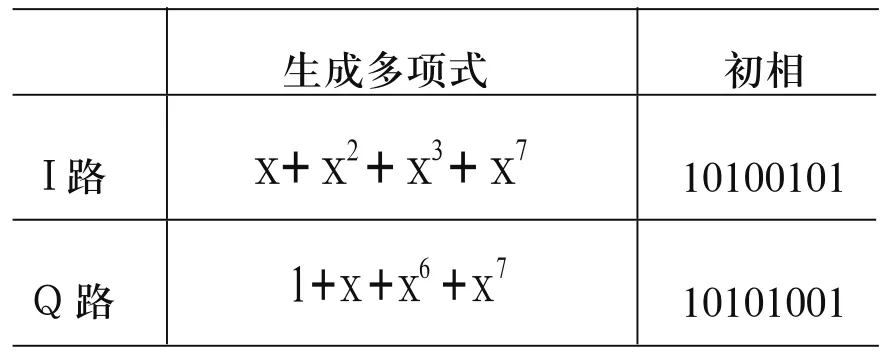

码生成多项式及初相如表2所示。

表2 PN码生成多项式及初相表

将寄存器初值设为码的初相,由生成多项式对寄存器中的值进行模二和,所得数值补到寄存器最低位,高位输入,循环操作即可生成所需的PN码。本单元采用八级移位寄存器,产生的序列长度为255,码速率为4Mbps,其中每15个扩频码对一个串行数据进模二和,每个PN序列可对17个串行数据进行扩频。经仿真测试这17组扩频码的互相关系数大都在8以下,最高不会超过10,故PN码有较好的互相关系数,其随机性也较强,具有到很好的抗干扰能力。

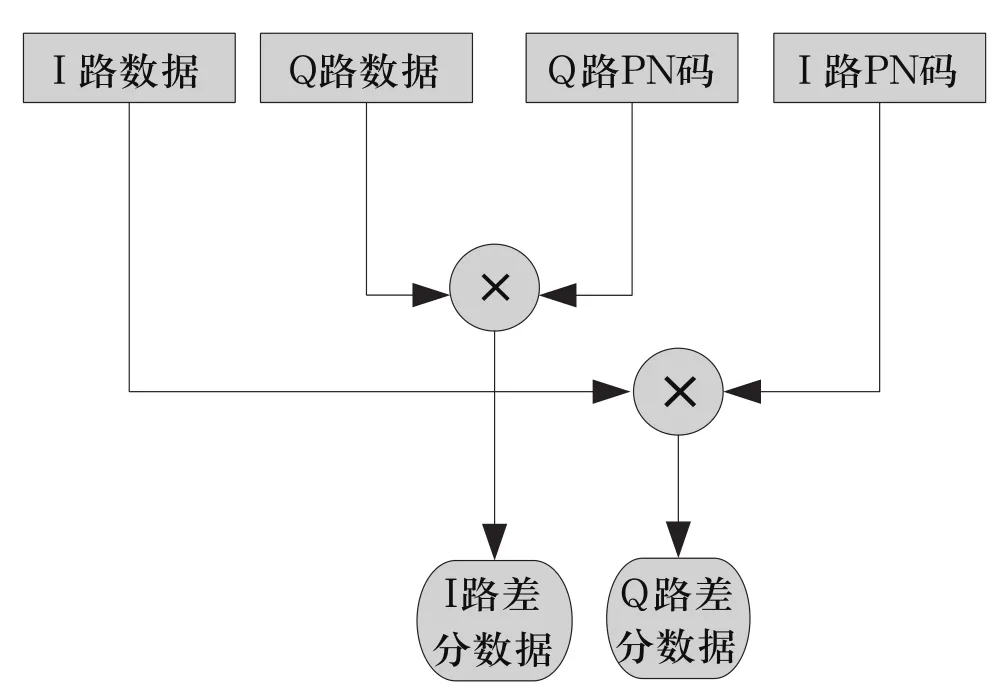

2.4 扩频模块

图5 扩频模块程序流程图

图5为扩频模块程序流程图。扩频模块对输入信号所作的处理就是在扩频码的码时钟的作用下将扩频码与输入信号进行模二和,处理之后输出的信号就为上文所要求的扩频码了。

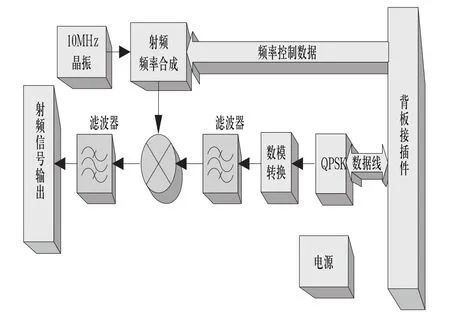

3 联机调试结果分析

图6 调制发射单元组成图

图6所示为中频调制发射单元组程图。FPGA处理后输出的I、Q两路扩频信号通过接插件传给调制发射单元,数据先后经过QPSK调制、数模转换、带通滤波、中频调制等处理,最终输出给功率放大器后经天线发射出去。发射的中频信号频率为650MHz±5MHz,功率为50W。

联机调试为中频发射单元与中频接收单元通过衰减器联接调试,通过调节衰减器的值来模拟中频信号在无线信道中传输。分别针对信道衰减量及有无信道编码两种情况进行调试。第一种情况是在有信道编码时信道的衰减值分别为70dB、80dB时发送图像与接受图像的对比;第二种情况为同样的信道衰减无信道编码与有信道编码的情况下所接收的的图像的对比。有信道编码时不同信道衰减下的图像对比

测试结果是第一种情况有信道编码时,信道衰减为70dB时接收图像与发射图像基本一致,视频数据准确传输, 信道衰减为80dB时收受图像中虽然出现了少量的马赛克,但并不影响整体效果,误码率在可接受范围内;第二种情况在无信道编码的情况下,信道衰减为70dB时的图像就出现了马赛克,而同样情况下有信道编码所接收到的图像就很清晰基本上不存在误码。信道衰减为80dB时有信道编码的情况下所接收到的图像,图中只有极少部分出现马赛克现象,而相同的信道衰减下无信道编码时所接收到的图像,图像出现跳跃、不连续、马赛克等现象。因此,由上面的两组对比可见,通过信道编码这一环节,对数码流进行相应的处理,使系统具有一定的纠错能力和抗干扰能力,可极大地避免码流传送中误码的发生。

通过整机的调试及多次检验,证明了系统性能的优越性,达到了国内同类产品的较高水平。

[1] 阮秋琦.数字图像处理学[M].北京:电子工业出版社,2001.

[2] 李雷鸣,张焕春.一种基于FPGA的图像中值滤波器的硬件实现[J].电子工程师,2004,2.

[3] 张博,吴芝路,等.基于FPGA的电子稳像平台的研究[J].电子技术应用,2004,5.

[4] 王诚,等.FPGA/CPLD设计工具[M].北京:人民邮电出版社,2003.

[5] 徐欣,于经旗,等.基于FPGA的嵌入式系统设计[M].北京:机械工业出版社,2005.

[6] 杨坤明.一种基于FPGA技术的高速码型数据发生系统的设计与实现.北京:制造业现代化.2009.10.

[7] 赵永新,夏荣,等.基于高性能FPGA的快速并行FFT及其在谐波监测上的应用,北京:制造业现代化,2008,08.

TP211+.5

A

1009-0134(2010)12(上)-0226-03

10.3969/j.issn.1009-0134.2010.12(上).72

2010-08-29

郝红(1973 -),女,山东潍坊人,讲师,硕士,主要从事机电技术的教学及研究工作。