基于VHDL的简易CPU的设计和实现

2010-03-27宋沛罗琼

宋沛 罗琼

(广州大学物理与电子工程学院,广州番禺510006)

1.引言

现代电子设计技术的核心是EDA(Electronic Design Automation)技术。EDA技术是依赖计算机作为硬件平台,以大规模可编程逻辑器件及集成电路为设计载体,设计者在EDA软件平台上,使用以描述硬件电路的功能、信号连接关系及定时关系的语言HDL(即硬件描述语言)完成文件设计,再经由计算机自动地完成逻辑编译、逻辑化简、逻辑分割、逻辑综合、优化、布局布线、以及逻辑优化和仿真测试,直至完成对特定目标芯片的适配编译、逻辑映射和编程下载等工作,最终形成集成电子系统或专用集成芯片的一门技术[1]。

本文采用EDA技术,以VHDL为硬件描述语言,以QuartusII6.0[2]为开发环境,采用“自顶向下”[3]的设计方法,选用Altera公司CYCLONE[4]系列的EP1C6Q240C8N芯片作为目标芯片,设计实现了一个简易微处理器。在使更多人理解并接触微处理器的同时,为设计和使用IP核打下基础。此简易微处理器,虽在性能上不能与商用CPU相提并论,但“麻雀虽小,五脏俱全”。

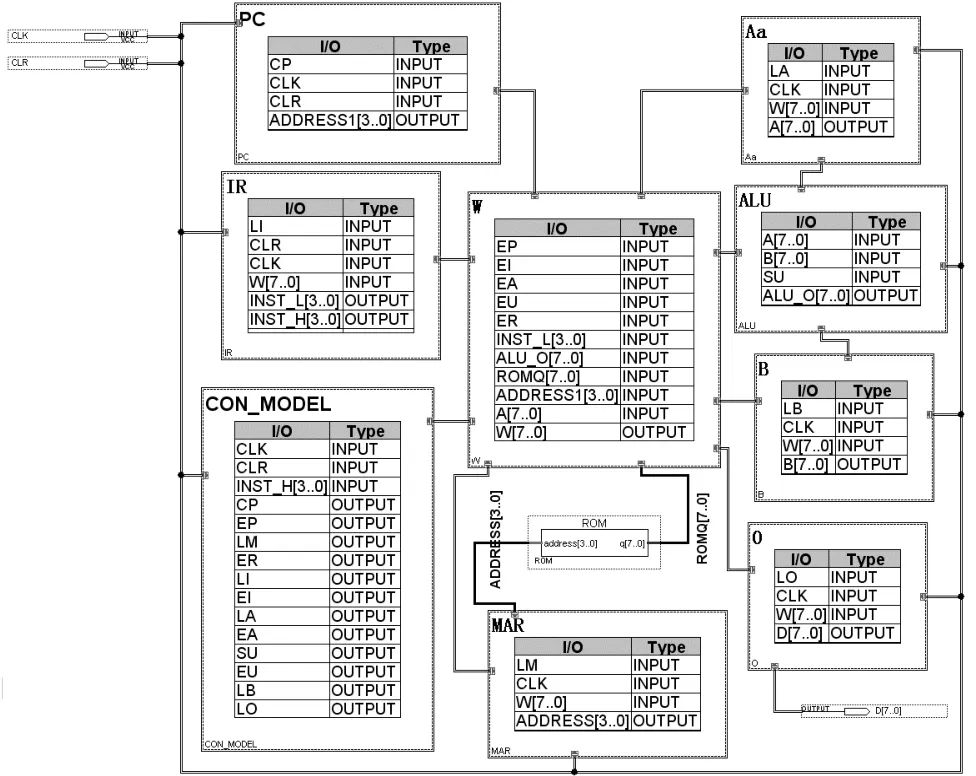

2.简易CPU的系统结构

此简易微处理器的结构特点是:功能简单,只能做两个数的加减法;内存量小,只有一个16×8ROM;字长为8位,输出用二进制8位显示。简易微处理器的总体结构如图1所示。简易微处理器共分十个部分。PC是程序计数器,每次运行之前,先复位至0000,当取出一条指令后,PC加1,为了简化,将其计数范围设定为0000~1111。也就是说,存储指令和数据的PROM的地址范围为0000~1111,共16个存储单元,每个存储单元是8位。MAR是存储地址寄存器,接收来自PC的二进制程序号,作为地址码送至PROM去。IR是指令寄存器,从ROM接收到指令字,同时将指令字分送到控制部件CON_MODEL(高4位)和W总线(低4位)上去。CON是控制部件,主要负责将指令寄存器IR送来的高4位译成12位的控制信号,由此控制信号指挥其它功能部件的运作。A为累加器,用以储存计算机运行期间的中间结果,它能接收W总线送来的数据,也能将数据送到W总线上去。它还有一个数据输出端,将数据送至ALU去进行算术运算。ALU为算术逻辑部件,将其简化为一个二进制补码加法器/减法器。寄存器B,将要与A相加减的数据暂存于此寄存器。输出寄存器O,计算机运行结束时,累加器A中存有答案。如要输出此答案,就得送入O。D为二进制显示器,这是用发光二极管(LED)组成的显示器。每一个LED接到寄存器O的一位上去。当某位为高电位时,则该LED发光[5]。

图1 简易微处理器结构[6]

3.基于VHDL的简易CPU的设计和实现

用VHDL分别实现图1中的所有部件,其中最重要的是控制部件CON和总线部件W的设计和实现,其它部件实现较简单(其它部件多为在时钟下降沿触发的异步清零同步使能的寄存器或计数器),这里不做详细介绍。

3.1 控制部件的设计和实现

控制部件CON的功能如下:

每次运行之前,发出CLR=1,使有关的部件清0。此时:PC=0000 IR=0000 0000

能根据IR送来的指令发出12位的控制字:

根据控制字中各位的置1或置0情况,计算机就能自动地按指令程序有秩序地运行。

3.1.1 简易CPU的指令系统

为了简化系统我们将此微处理器的指令精简为5条,都采用直接寻址的方式。具体指令见表1。

表1 简易微处理器的指令系统

3.1.2 每个指令在6个节拍中的控制字

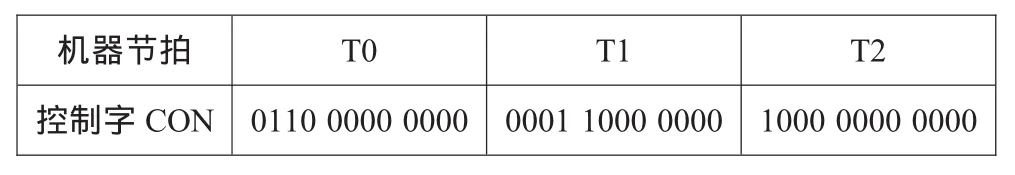

执行一条指令的时间为一个机器周期。机器周期又可分为取指周期和执行周期。取指周期的过程需要3个机器节拍,每个指令的取指周期都是相同的,其每个节拍的控制字如表2。

表2 取指周期3个节拍的控制字(CON=CPEPLMER LIEILAEA SUEULBLO)

(1)地址节拍T0:控制部件发出的控制字为CON=CPEPLMERLIEILAEASUEULBLO=0110 0000 0000,即Ep为高电平,Lm为高电平,其它与总线W相连的输入为高阻状态,从而将PC的内容送入MAR(并通过MAR到达PROM)。

(2)存储节拍T1:从表2可知ER为高电平,LI为高电平,将ROM中由PC送来的地址码所指定的存储单元中的内容送到IR,同时IR立即将其高4位送至控制部件。

(3)增量节拍T2:从表2可知Cp为高电平,使PC加1,做好下一条指令的取指准备。

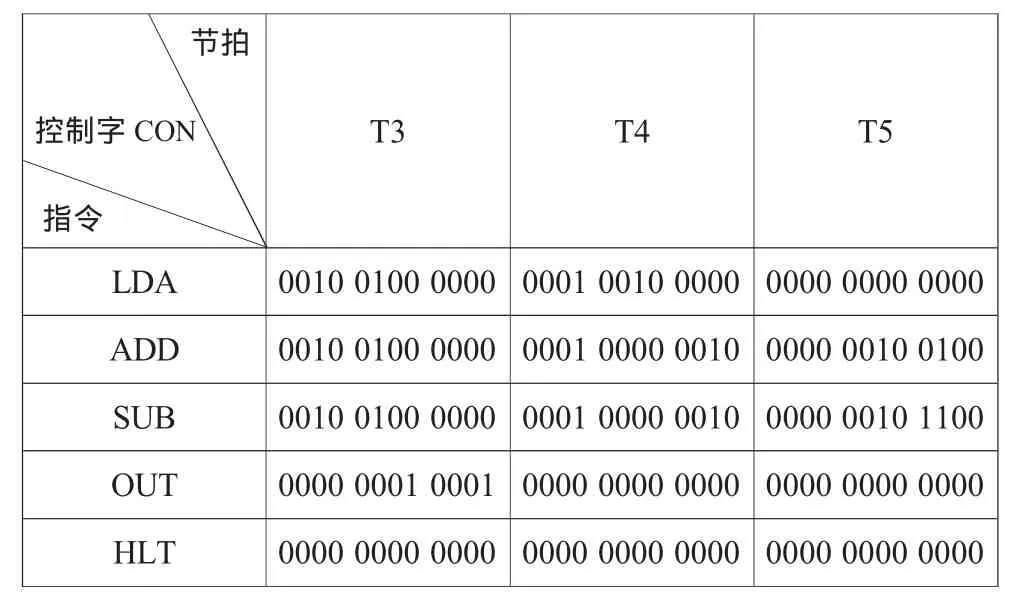

紧接着就进入执行周期,不同的指令执行周期都是3个节拍,但是发出的控制字不尽相同。表3针对五个指令分别列出执行周期中3个节拍所对应的控制字。

下面以ADD指令为例,说明执行周期的控制字的设置。ADD指令的执行周期的第1个节拍T3,从表3中可以看出发出的控制信号CON中,LM=1,EI=1。将IR的低4位数作为地址并立即送至MAR(PROM分为指令区和数据区,在取指周期中,访问的是指令区;在执行周期中,访问的是数据区)。ADD指令的执行周期的第2个节拍T4,发出的控制信号使ER=1,LA=1。将PROM数据区的存储单元的内容送入累加器A。ADD指令的执行周期的第3个节拍T5,发出的控制信号使LA=1,EU=1,将算术逻辑部件的计算结果存入累加器A中。

表3 执行周期3个节拍每个指令所对应的控制字(CON=CPEPLM ER LIEILAEA SUEULBLO)

3.1.3 控制器部件的VHDL实现

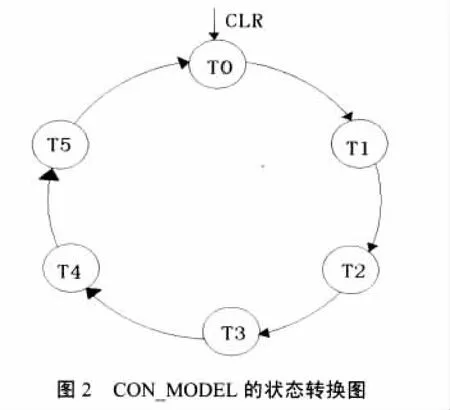

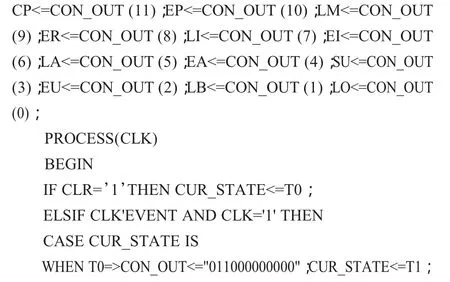

采用有限状态机实现上面的控制功能。由于无论什么指令都需要6个节拍(最后的3个节拍根据具体的操作不同而输出不同的控制信号),因此对应地设计有限状态机共有6种状态,状态之间的转换由时钟控制(如图2所示),在每个状态下发出相应的控制字,从而实现根据指令进行控制各部件完成指令所要求的操作。控制部件的输入数据来自指令寄存器IR的高四位INST_H[3..0]。同样具有异步清零信号CLR,可以使整个系统复位。控制部件根据指令的高4位决定其他部件的使能信号和锁存信号共12个信号,从而控制整个系统的运行情况。

在CON_MODEL的结构体的说明部分定义数据类型,使状态符号化:

3.2 总线模块的设计和实现

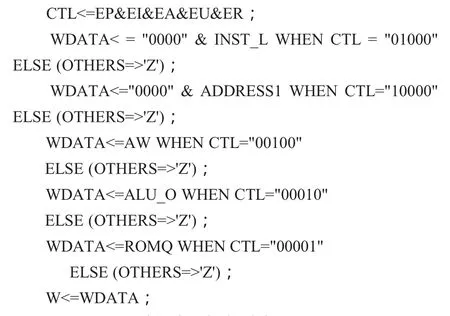

总线可以使多个模块之间沟通信息,为了避免信息在公共总线W中乱窜,必须规定在某一时钟节拍,只有一个寄存器L门为高电平,和另一个寄存器的E门为高电平。其余各门的L和E控制信号必须为低电平。这样,E门为高电位的寄存器的数据就可以流入到L门为高电平的寄存器中去。实现总线结构的主要VHDL代码如下:

3.3 顶层文件仿真分析和测试

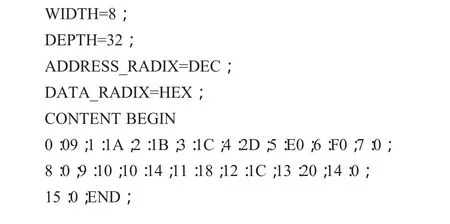

为了对整体进行测试,我们需在ROM中放入要执行的程序段和要处理的数据。由于整个系统只支持5种指令,而且寻址空间只能是0~f,因此我们仅设计了一段程序计算16+20+24+28-32,并将相应的二进制代码(此段代码可参照参考文献[4])存入PROM中。由于PROM是由LP_ROM产生,要存储内容,只需设定它的存储内容的文件rom.m if即可。下面是rom.m if文件的内容如下:

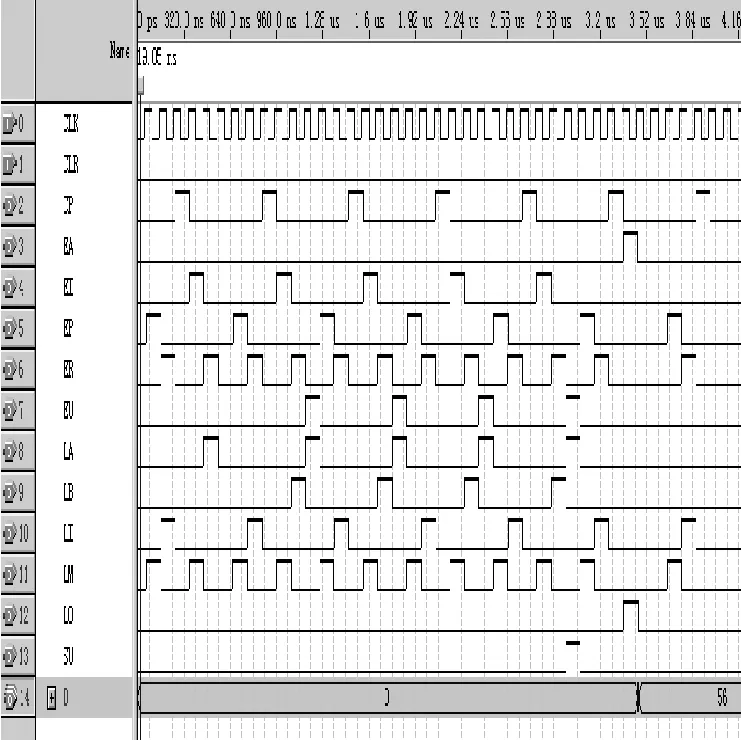

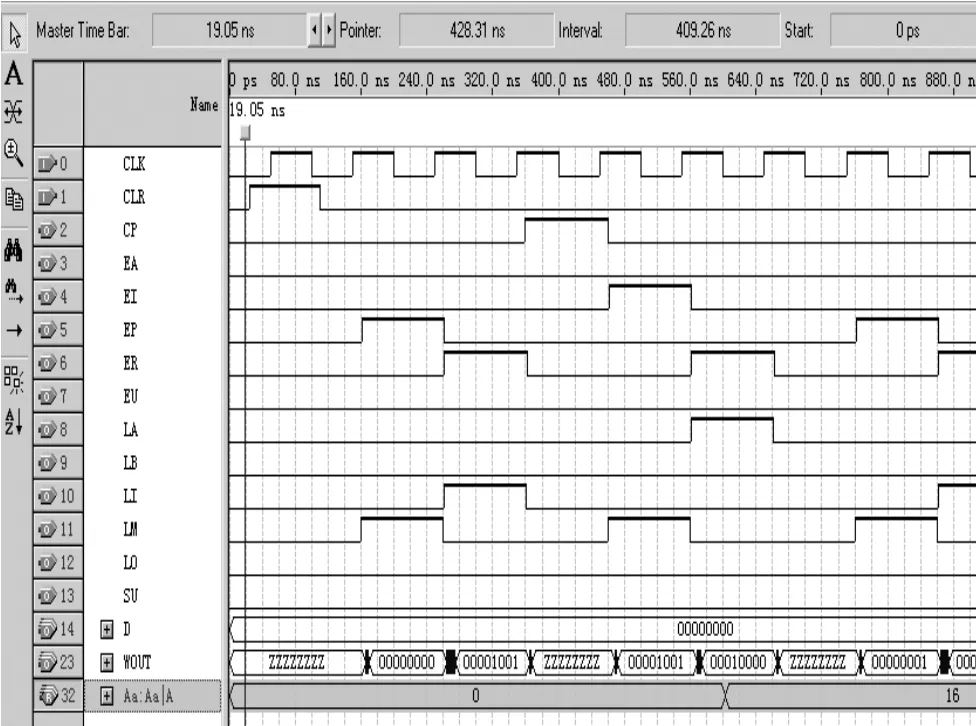

图3 顶层文件仿真与分析

图4 第一个指令的仿真分析

图3为使用QuartusII6.0进行仿真分析的结果。由图3可知,输出结果为56,是正确的。图4加入了中间信号的输出,便于分析第一个指令周期。从图4可看出,CLR信号使当前状态为T0,第一个CLK上升沿到,发出EP=’1’和LM=‘1’控制信号,程序计数器PC发出了数据并且存入地址寄存器MAR,这时数据线上的数据是PC的“0000”,因此W出现“00000000”;第二个CLK上升沿到,进入状态T1,于是ER=‘1’和LI=‘1’,于是ROM发送地址为“0000”单元存储的指令到总线,并且存入指令寄存器IR,此时的总线W是ROM发出的数据“00001001”(即LDA 9H指令对应的二进制代码);当第三个CLK上升沿到,进入状态T2,出现CP=‘1’,此时的计数器PC加1,这时的总线变为高阻状态;当第四个CLK上升沿到,进入状态T3,EI=‘1’和LM=‘1’,IR送低4位到总线,MAR接收此低4位数,此时的数据总线为“00001001”;当第五个CLK上升沿到,进入状态T4,ER=‘1’且LA=‘1’,因此ROM将数据送到总线,然后在时钟下降沿存到寄存器A中;当第六个CLK上升沿到,进入状态T5,E和L端全部为低电平,即是一个空节拍(为的是使每条指令的机器周期都一样长),此时的总线的数据是高阻状态。自此,完成了第一个指令LDA 9H,即将ROM中数据区的地址为9H的存储单元中的数据放存入A累加器中。之后由进入下一个机器周期,依次类推。由时序仿真可知设计正确。最后使用EDA工具和软件QuartusII6.0,将设计配置到A ltera公司的CYCLONE系列的EP1C6Q240C8N芯片,运行正确。

4.结束语

本文使用VHDL语言,采用“自顶向下”设计方法,实现了一个简易微处理器。并以EP1C6Q240C8N芯片为目标芯片,用QuartusII6.0产生的配置文件配置目标芯片,运行正确。此简易微处理器的设计和实现可以起到抛砖引玉的作用,为进一步扩展CPU,实现更多更复杂的指令,扩大存储器容量,实现中断等深入设计打下基础。

[1] 潘松,黄继业.EDA技术实用教程[M].第三版,北京:科学出版社,2006.

[2] Introduction to the Quartus II Software Version 10.0[EB/OL].http://www.altera.com.cn/literature/manual/intro_to_quartus2.pdf

[3] Cyclone Device Handbook,Volume 1[EB/OL].http://www.altera.com.cn/literature/lit-cyc.jsp

[4] 郑学坚,周斌.微型计算机原理及应用[M].第三版,北京:清华大学出版社,2001.

[5] IEEE Standard VHDL Language Reference Manual,IEEE Standard 1076-1987,New York,1988.

[6] Altera Quartus II 6.0 reference manual,A ltera Corporation,San Jose CA,1992.