光电色选机高速数据采集系统的设计

2010-02-22朱体高刘铁根张海顺

朱体高 刘铁根 张海顺

(1.天津大学精密仪器与光电子工程学院 ,天津,300072;2.天津市华核科技有限公司七室,天津 ,300180)

引 言

光电色选机是一种检测物料颜色深浅的设备,由若干个滑槽组成,每个滑槽内有若干个通道,每一个通道前后各有一个光电二极管作为传感器检测物料表面的颜色深浅。每个传感器的信号经过变换、放大、滤波等处理后得到一个范围为-2.5~+2.5 V的模拟电压信号,信号的最高频率为 800 Hz。此信号要被送到数据处理系统进行处理。对一个厂家的色选机而言,每个滑槽内的通道数是一定的,如32个,滑槽数量的多少决定一台色选机通道的多少。一个滑槽内的某一侧的信号在一块线路板上,形成一个数据采集系统。现在的光电色选机通道数量的增多是一个趋势,如 192通道、256通道、320通道,它们需要检测、传输和处理的数据点的数量分别为 384,512,640,每一个点的数据为模拟量。而且不同的数据采集系统之间、信号采集系统和信号处理系统之间在空间上有一定的距离,最远的距离有5 m。

对于这么多的模拟信号,有以下几种处理方式:

(1)逐个传输和处理,这种方式最直接和简单,但是它的缺点是传输线特别多,处理系统的数量特别多,可靠性差,信号传输不可靠,产品的成本增加;

(2)模拟信号的扫描,它对一定数量的模拟信号进行扫描式处理,其特点是:各个模拟信号的模拟开关打开、A/D转换、数据传输是分时进行[1],与逐个传输和处理相比有一定的改善,但对于信号数量特别多的系统来说如果采用此方式,循环采集一次的时间将特别长;如果要满足对信号采样频率的要求,则循环一次处理的数据量有限。

1 系统总体设计

由于本设计应用到具体的产品中,因此要考虑产品的可靠、成本的低廉以及工艺的简单。

为了解决信号采集系统中传输和处理的速度问题,将并行技术[2]应用到设计中,将有效解决系统的时间和空间问题。本系统采用了数字扫描信号采集和传输方式。在设计中一共采集和处理了256点的模拟信号,256个点分布在 8块数据采集系统线路板上,每块数据采集系统线路板上有 32个模拟信号。如果在实际的色选机中有大于256个点的信号点需要处理,可以采用多套同样的系统完成。

由于被采集的模拟信号的频率最高为800 Hz,因此系统的采样频率最少为 1.6 kHz,为了保证数据的不失真,本系统采用5 kHz。在任何一个采样周期内要将256个信号全部扫描一次。

2 硬件组成

系统的硬件组成如图1所示。数据处理系统通过控制总线向采集系统发送控制信号,同时处理数据采集系统通过数据总线发送的数据信号。控制总线有两个信号,一个是同步信号,另外一个是时钟信号。同步信号的频率为 5 kHz,即信号的采样频率,时钟信号的频率为 1.5 MHz。因此一个同步周期内最多有 1.5 M Hz/5 kHz=300个时钟信号,在同步信号有效阶段有263个时钟信号。在这263个时钟内对256个模拟信号进行扫描。数据总线中是8个数据信号,表示一个字节数据的 D0-D7。信号采集系统与数据处理系统最远有 5 m的距离,因此数据传输使用差分的方式。

图1 系统的组成图

单个采集系统如图2所示,信号切换部分由四片74HC4051组成,用于切换一个采集系统内32个通道的模拟信号。 A/D转换部分由一片 A/D转换器芯片 MAX153组成,用于对切换到的信号进行模数转换,它的最小转换时间为 660 ns[3],实际系统的转换时间为3 333 ns,留出足够的时间保证系统的稳定可靠。选择M AX153的另外一个重要原因是它不需要调整就可以适合于负电压信号的模数转换。数据传输部分由两片 MC3487组成,它在需要传递数据的时候通过差分的方式将 A/D转换后的数据送到数据总线上,不需要传输数据的时候,将数据总线设置为高阻态。 MC3487最高工作速度为 10 M[5],足够保证系统工作在 1.5 M的要求。CPLD根据控制总线的控制信号控制通道切换部分、A/D转换部分和数据传输部分的工作,因为对于不同采集系统的信号要加以区别,在每块采集系统的线路板上有一组三位的拨码开关,用来表示该采集系统的位置。 CPLD采用的 ALTERA公司的 EPM7064S,它内部有 64个宏单元,5 V的供电电压,最高工作频率达到 175.4 M Hz[6],用它来控制此系统有足够的速度裕量。

图2 单个采集系统组成图

3 控制流水线设计

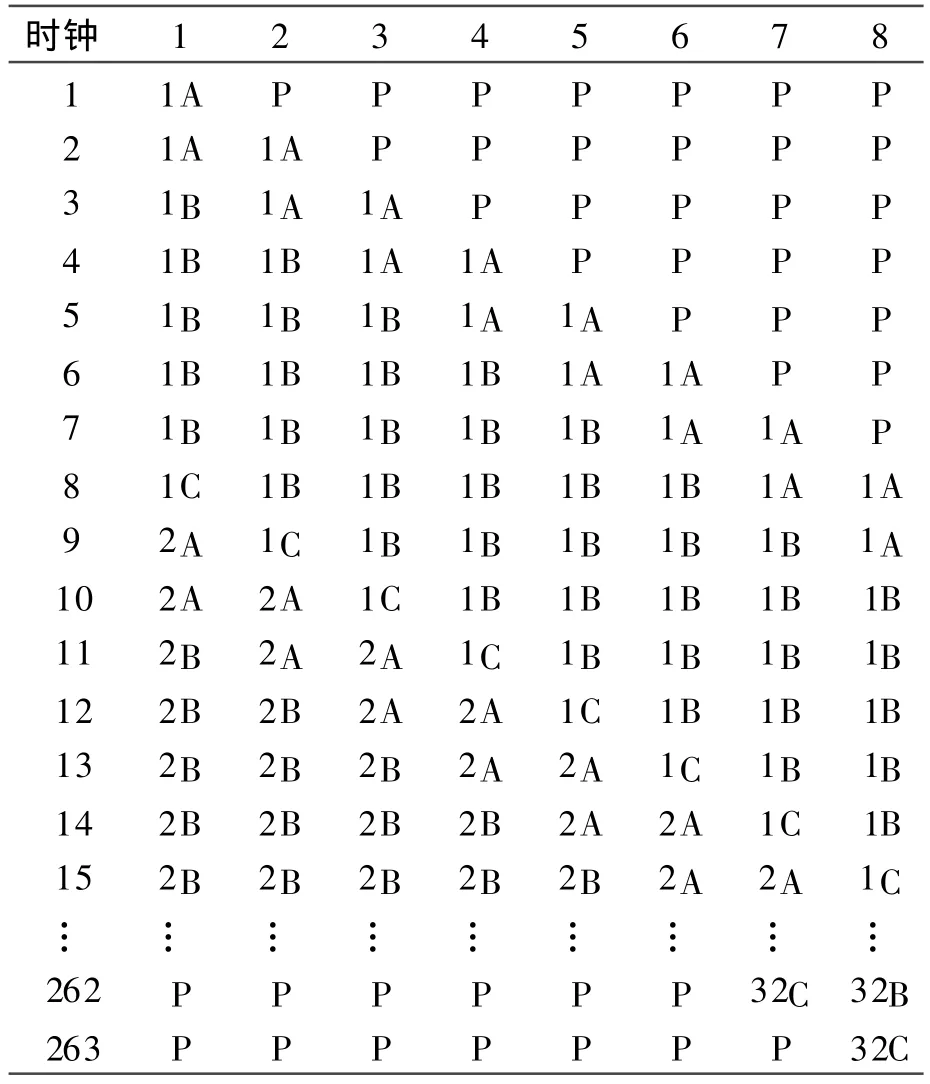

流水线如表1所示。对单个通道的模拟信号处理需要 8个时钟,时钟信号的频率为 1.5 M Hz,周期为 667 ns,当选定某个通道后,该通道的数据通过高速模拟开关 74HC4051选中,在 (VCC=4.5 V;VEE=-4.5 V)电压点上,模拟开关的数据延时时间最大为 77 ns[4],而且电压越高延时时间越短,本系统工作在(VCC=5.0 V;VEE=-5.0 V)电压点上,为了保证数据的准确,消除通道切换时的噪声和通道切换的延时,将数据稳定两个时钟周期(1 333 ns),开始进行 A/D转换。由于控制 A/D转换的是CPLD,而不是MCU,因此 A/D转换的过程中的各个过程必须保证有足够的时间,需要 5个周期,整个采集系统的最后一个时钟将它保持并输出。从表中可以看出,对于单个通道,数据传输只占整个 8个流水线周期的一个周期,其余的时

表 1 单个通道数据采集传输流程表

在系统的设计中,为了消除数据采集过程中的等待影响总线的情况,采用了 8级流水线的并行技术,具体的流水线如表2所示,第1~ 8时钟周期,第1个采集系统的第 1通道工作,第 8个时钟周期输出数据;第 2~ 9时钟周期,第 2个采集系统的第 1通道工作,第 9个时钟周期输出数据。依次类推……一直循环到第 256~263个时钟周期,第8个采集系统的第32通道工作,第263个时钟周期输出数据。至此所有 256个通道的数据处理并传输完毕,共需要 263个时钟周期。

从表2可以看出,在所有的时钟周期中,CPLD都在计数,除了开始和结束的共7个时钟周期外,其他的时钟周期中,每个采集系统中至少有一个通道的信号处于打开状态,所有的 A/D转换器除了在等待数据稳定外都在进行 A/D转换的工作,数据总线都在发送数据。因此这种流水线的方式比逐个模拟量扫描的效率高,处理的模拟量数据点多。

表2 系统流水线表

4 系统软件

设计的内容是用VHDL语言编写 CPLD的程序。包括以下模块:计数模块,A/D转换和数据发送控制模块,模拟开关控制模块。其中计数模块是整个系统的控制核心,包括一个减 1计数器和一个加1计数器。使用减1计数器的目的是为了和采集系统号的载入关联。用下面程序中的CNT控制A/D转换和数据的发送,用 CHANNEL-NUM控制74HC4051的片选和地址信号达到通道选择的目的。

变量 CHANNEL-NUM的低三位产生的信号与 74HC4051地址依次连接,CHANNEL-NUM高三位产生的信号进行2-4译码,控制 74HC4051使能引脚,其中 CHANNEL-NUM最高位控制总的输出 ,它为‘1’时 ,所有的 74HC4051都将停止工作。变量CNT根据表1的要求,按照各个芯片工作特点,确定相应输出引脚的电平信号。实际设计时使用一个case语句进行相应的译码。

5 结束语

本系统通过8级流水线扫描方式将256个点的问题串行化,解决信号处理点数量多连接线复杂的问题。通过流水线的方法将需要高速运行的系统低问题,并通过差分的方式传输,系统的传输在 5 m的长度范围内 ,速度达到 1.5 MB/s。

由于本设计应用到了实际的产品中,因此在速度的设计上保留了很大的设计余量。本系统所选的器件价格低廉,生产工艺简单,现已成功应用到批量生产中,在 128、192、256通道色选机中应用。

[1] 李正岱,刘文怡.多路信号采集器的硬件电路设计[J].微计算机信息.2008,(1/2):220-222.

[2] 米根锁,王瑞峰.基于 PCI总线流水式高速数据采集系统设计 [J].自动化仪表 ,2006,27(8):33-36.

[3] Maxim Integrated Products.M AX153[EB/O L].http://datasheets.maxim-ic.com/en/ds/M AX153.pdf,1993/2010-12-29.

[4] Philips semiconductors. 74HC4051;74HCT4051 Product data sheet:8-channel analog multiplexer/demultiplexer[EB/OL].http://www.nxp.com/documents/data-sheet/74HC-HCT4051.pdf,2005/2010-12-29.

[5] Texas Instruments Incorporated.M C3487:Interface-RS-422-M C3487-TI.com[EB/OL].http://focus.ti.com/docs/prod/folders/print/mc3487.html,2010-12-29.

[6] Altera Corporation.M AX 7000:Programmable Logic Device Family[EB/OL].http://www.altera.com/literature/ds/m7000.pdf,2005/2010-12-29.