基于TMS320VC5410的DES加密系统设计

2010-01-29赵旭东

於 辉,石 涛,赵旭东

(桂林电子科技大学 信息与通信学院,广西 桂林 541004)

数据加密是为了保证所传输信息的安全而在特定参数(称为密钥)的控制下按照某种规律对原始数据进行的人为扰乱,将其转换成秘密形式的信息。数据加密标准(Data Encryption Standard,DES)是第一个广泛应用于商用数据保密的、公开的密码算法,在其公布和正式实施后,成为许多国家政府、银行和标准组织的信息安全处理标准。然而DES实现信息保密的前提是对于密钥的有效管理,这就要求基于DES的加密系统必须提供可靠、方便的密钥保存设备。同时在近20年,DSP处理器的性能得到很大改善,软件和开发工具也得到相应发展,价格大幅下降,应用也越来越广泛。本文选用TI公司TMS320VC54x系列DSP,采用软件方式实现DES加密算法,同时以集成电路卡(Integrated Circuit Card)作为密钥存储设备。为了解决DSP的通用IO口较少的问题,使DSP片上的一些特殊功能引脚工作在通用输入输出引脚状态显得尤为重要。本文结合DSP运算速度快、片上资源多的特点,研究并实现基于DSP的DES加密系统及其与IC卡以及终端PC机之间的通信协议。

1 DES算法简介

DES作为美国国家标准的加密算法,既可用于加密又可用于解密[1]。其加密过程主要分为3个部分,如图1所示。首先把输入的数据比特流以每64 bit为一组进行分组得到明文 x,之后是一个初始置换 IP,记为 x0=IP(x)=L0R0(L0代表左边32 bit,R0代表右边 32 bit);然后以每一组作为加密单元,在16个子密钥(每个子密钥的长度为48 bit)的控制下根据下列规则计算 LiRi(1≤i≤16),进行 16轮的非线性变换:

每轮中都有换位和代替运算;最后再经过一个逆初始置换IP-1(为IP的逆变换)输出一组64 bit长的密文[2]。

图1 DES加密算法流程Fig.1 Flow chart of DES encryption algorithm

对于数据较大的文件加密要求芯片具有很高的处理速度。出于保密通信系统的需求,该系统设计以IC卡作为密钥的存储设备,采用TI公司TMS320VC54x系列DSP实现对来自PC机的明文数据进行DES加密处理。该方案运算速度快、保密性好,具有很高的可扩展性,用于保密的数据采集系统中,对来自数据采集模块的信号进行DES加密后,传输给PC机。

2 系统硬件设计

结合运算速度,外设接口以及性价比等方面的考虑,选用TI公司TMS320VC54x系列16位定点TMS320VC5410型DSP作为实现DES加密的硬件平台。它具有较低的功耗与杰出的性能,时钟最高频率可以达到100 MHz。另外,TMS320VC5410片上提供了3个可以设置为GPIO接口的多通道缓冲串口(McBSP),这对外围设备接口子系统的设计至关重要。系统中除TMS320VC5410基本的工作外围电路如电源晶振模块、Flash模块和JTAG接口模块以外,还主要包括以下 2部分:1)TMS320VC5410与 SLE5542型 IC卡片的接口模块,主要用于系统工作时IC卡向DSP传送用于数据加密的密钥和卡片存储的其他一些用户信息;2)DSP与PC主机的通信接口模块,它是DSP与个人电脑的通信接口,主要用于DSP接收明文数据以及将加密后的数据反馈至PC机。

2.1 McBSP简介

TMS320VC5410片内包含了3个全双工的多通道缓冲串 口(Multichannel Buffered Serial Ports,McBSP),分 别 为McBSP0、McBSP1和McBSP2。它们可以提供全双工通信、连续数据流的双缓冲数据寄存器、接收和发送独立的帧和时钟,可以直接和系统中的其他器件接口连接并可以配置为通用IO口。McBSP与外设的数据交换,通过DX引脚发送,RX引脚接收。通信的时钟与帧信号由CLKX、CLKR、FSX及FSR引脚来控制。TMS320VC5410对McBSP的控制由2个16 bit的串口控制寄存器(SPCR[1,2])和引脚控制寄存器(PCR)来实现。DSP的CPU或DMA从数据接收寄存器(DRR[1,2])读取接收数据;发送时,向数据发送寄存器(DXR[1,2])写数据,数据写入后通过传输移位寄存器(XSR[1,2]),移位输出到DX上。同样,从DR上接收的数据,移位存储到接收移位寄存器(RSR[1,2]),并复制到接收缓存寄存器(RBR[1,2])。然后,再由(RBR[1,2])复制到 DRR[1,2]。DRR[1,2]可以由 CPU 或 DMA 读出[3]。

2.2 DSP与IC卡连接模块

选用西门子公司SLE5542型卡片,其引脚定义和功能说明如表1所示。它是一种按字节操作的多存储器逻辑加密卡,应答复位符合ISO7816-3标准。该型卡片内置了3个存储器:32×1 bit的 PROM 型保护 存储器、256×1 bit的EEPROM型主存储器以及32×1 bit的EEPROM型加密存储器。主存储器可重复擦除使用,按字节操作,并分为保护数据区和应用数据区,读出均不受限制,但应用数据区的擦除和写入则受加密存储器中的密码及密码计数器保护。

表1 SLE5542引脚定义和功能说明Tab.1 Pins definition and functions description of SLE5542

IC卡连接电路如图2所示。

图2 TMS320VC5410与SLE5542连接电路图Fig.2 Circuit connection between TMS320VC5410 and SLE5542

为了提高硬件的利用率和解决DSP片上通用IO口较少的问题,本系统设计将McBSP1配置为通过IO口实现其与IC卡片通信的模块。由于McBSP引脚中的DX只能配置用作通用输出脚,DR只能配置用作通用输入脚,不方便程序编写对引脚状态控制。所以在DSP对卡片读写的硬件电路中选择了 McBSP1的 FSR1、CLKR1、CLKX1、和 FSX1这 4个引脚,它们均可以通过16位的引脚控制寄存器(PCR)配置为通用I/O引脚。FSR1引脚通过CD4066开关电源芯片来控制SLE5542卡片的上电与掉电;由CLKR1连接卡片的RST触点,卡片复位时改变引脚的高低电平状态;CLKX1引脚与IC卡片的时钟触点CLK相连,该引脚状态的高低变化为卡片正常工作提供时钟信号;FSX1连接卡片数据I/O触点,负责DSP与IC卡片之间读写命令字和用户有用数据的传送。注意CLKX1和FSX1引脚要接上拉电阻,且FSX1配置的输入或输出状态要根据DSP与IC卡之间数据流向而定。

为了使McBSP1的相关引脚工作在系统需求的通用I/O状态,首先需要将该串口的控制寄存器SPCR1中的RRST位和 SPCR2中的 XRST位均设置为‘0’,使串口复位,串口操作禁止。然后设置引脚控制寄存器PCR中的XIOEN和RIOEN为‘1’,使串口的接收和发送引脚均工作在通用I/O模式;另外将 FSRM、CLKXM 和 CLKRM 位均设置为‘1’,使FSR1、CLKX和CLKR引脚作为通用输出管脚,将要输出的值分别存储在PCR中的FSRP位、CLKXP和CLKRP;对于FSXM位的设置,则需要根据通信时的具体情况而定。

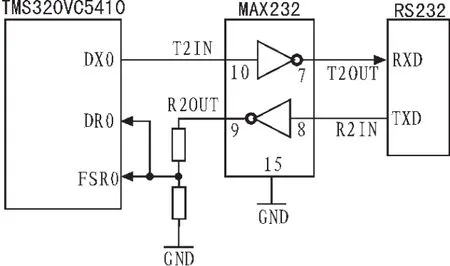

2.3 DSP与PC通信模块设计

系统设计中选择了McBSP0作为TMS320VC5410从外界PC机接收明文数据和输出密文的通道,直接通过PC机的RS232异步串口与TMS320VC5410之间进行加密解密数据的传送。这种方法通过软件实现PC机与DSP之间的串行双工通信,它的硬件设计简单且不会过多占用CPU的时间,可以实现数据的高速传输[4]。

RS232异步串口采用负逻辑传送数据,以10 V电压状态表示数据‘0’,-10 V电压状态表示数据‘1’;而 DSP的 IO口则以3.3 V表示高电平‘1’状态或者无数据传送,以0 V表示低电平‘0’状态。因此为了使TMS320VC5410的多通道缓冲串口与RS232接口进行通信,需要电平转换电路,本文使用了MAXIM公司MAX232电平转换器,如图3所示。

图3 TMS320VC5410与RS232接口通信电路Fig.3 Interface communication circuit of TMS320VC5410 and RS232

3 系统软件设计

选用TI公司CCS(Code Composer Studio)作为该加密系统软件设计时的开发和调试工具,使用C语言和汇编混合编程的模式完成软件设计。由于C语言编程具有便于阅读、维护、交流和可移植性好的特点,因此采用C语言完成整个程序的主框架设计,在对时间要求比较苛刻的地方或对代码运行效率有较大影响的场合采用汇编指令编写。

3.1 DSP读IC卡软件实现

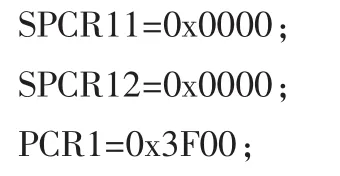

3.1.1 McBSP1串口配置

当把卡片插入卡座时,状态开关选通,并且电路板上提示灯亮表示插卡到位,DSP内存中的读卡状态标志位设置为‘1’。TMS320VC5410开始初始化McBSP1,使其工作在通用IO口状态,采用子地址寻址的方式对SPCR11(映射地址为 0049h,子地址为 00h)、SPCR12(子地址为 01h)和 PCR1(子地址为0Eh)等寄存器进行配置。配置代码如下:

此时FSR1、FSX1、CLKR1和CLKX1均用作通用输出管脚。把 PCR中的 FSRP位设置为‘0’,PCR1&=0xFFFB;则卡片VCC触点电平为低,卡片处于掉电状态;通过语句PCR1|=0x0004把FSR1引脚置高电平给卡片上电。

由于DSP的FSX1引脚与卡片的数据I/O触点相连,要求FSX1引脚具有双向传输的功能,但该引脚在同一时刻只能处于输入或输出一种状态,为此定义了以下两个宏实现引脚在输入与输出状态的改变。

#define set_IOout() SPSA1=PCR1;SPSD1|=0x0800;FSX1 引脚处于输出状态

#define set_IOin() SPSA1=PCR1;SPSD1&=0xF7FF;FSX1 引脚处于输入状态

3.1.2 复位与复位应答

DSP检测到读卡状态位为‘1’时,给卡片上电,CLK和RST保留于状态L,开始运行读卡程序将卡中存储的密钥读取至内存中。首先按照ISO7816-3标准对SLE5542卡片进行应答复位,复位可以发生在操作过程的任意时刻。之后,RST线被置于H状态,并维持至少15μs。在RST状态由高电平到低电平的转换期间CLK提供一个时钟脉冲,卡片内的地址计数器(address counter)清零,I/O引脚输出有效数据的第1位,这一数据可视为复位应答[5];在此后连续31个时钟脉冲的作用下,主存储器中的前4个地址中的32位标头数据被读出;下一个时钟脉冲使I/O引脚变为高阻状态,此时卡片复位与复位应答完成。

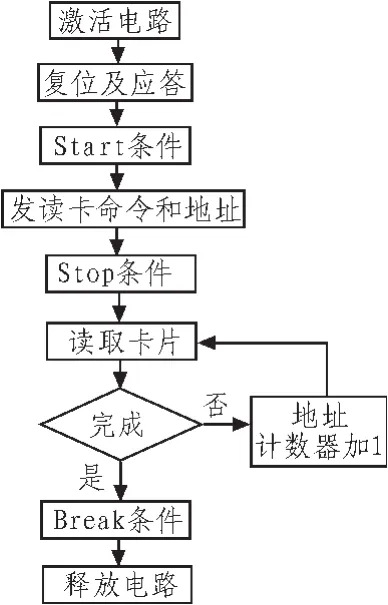

3.1.3 DSP读卡主程序设计

图4为DSP读IC卡主程序设计。卡片复位应答之后,则处于等待指令输入的状态。SLE5542每个指令均由控制字节、地址字节和数据字节组成,传输时从控制字节的最低位开始。控制字节传送完毕之后,依次传送地址字节和数据字节,均为低位在前。每个指令的传输都开始于一个Start条件(在时钟信号为高电平状态,通过DSP发送卡片IO口一个下降沿),结束于Stop条件(在时钟信号为高电平状态,通过DSP发送卡片IO口一个上升沿)。根据指令作用的不同,SLE5542接收完成后可能处于数据输出模式(DSP读卡)或者内部处理模式(DSP写卡)。

图4 DSP读IC卡主程序设计Fig.4 Main program design of DSP reading IC card

通过TMS320VC5410发送读卡命令和所要读取内容的地址(N=0,…,255)后,在CLK信号的作用下卡片将主存储器中的数据按比特移至I/O引脚发送至DSP内存中。读取数据完成后,额外的一个时钟信号将使I/O引脚变为高阻状态,卡片退出输出模式等待接收新的指令,也可以用Break条件(在CLK为低时,把RST信号由低电平变为高电平状态)结束此次操作。

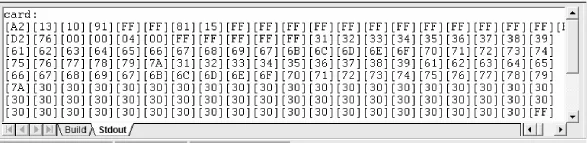

图5显示了TMS320VC5410对SLE5542卡片读卡程序的调试结果,为了验证读卡功能的实现,系统读取了卡片中的所有字节的内容。其中前 8个字节为‘A2131091FFFF8115’为IC卡的厂商标识;之后地址8~20的13个字节全为‘FF’是写保护区;地址21~26是 6个字节的用户代码‘D27600000400’,之后又是5个字节的写保护区;从地址32~255之间的数据是用户数据区,可以在这些地址里存放加密系统的密钥和其他的用户信息。

图5 DSP读卡程序CCS调试结果Fig.5 Debug results of DSP card reader program in CCS

3.2 PC通信软件设计

3.2.1 McBSP0的初始化配置

首先通过 SPCR10=0x0000,SPCR20=0x0000把 RRST与XRST位设置为‘0’,使串口复位。设置PCR0=0x0B0C;采样率由DSP内部产生,接收与发送帧同步信号为低有效,时钟上升沿发送数据、下降沿接收数据。其次通过接收控制寄存器 RCR10(子地址为 02h)和 RCR20(子地址为 03h)来对DSP串口接收模式进行设置,令 RCR10=0x0940;RCR20=0x0004;接收帧长度10字、每字16 bit,忽略除第一个帧同步后的其他帧同步信号。通过传输控制寄存器XCR10(子地址为04h)和XCR20(子地址为05h)来对DSP串口发送模式进行设置,令 XCR10=0x0940;XCR20=0x0004;使数据的发送与接收模式一致。另外,采样率发生器控制寄存器SRGR10(子地址为 06h)和 SRGR20(子地址为 07h)控制采用率发生器的工作模式。本系统中选择PC机的串口工作波特率为38 400,采样率发生器计算公式为[6]:

CLKGDV=CPU 工作频率/(16×波特率)-1

由于TMS320VC5410工作频率为100 MHz,因此CLKGDV=100 000 000/(16×38 400)-1=161,设置 SRGR1=0x00A1,SRGR2=0x2000;最后通过 SPCR1=0x0001,SRGR2=0x2000;对串口使能,处于可操作状态,至此完成了McBSP0的初始化配置。

3.2.2 数据格式的统一

DSP通过McBSP0接收外界PC机数据采用中断方式。这里为了实现TMS320VC5410同步串口与PC机异步串口通信时数据格式的统一,把McBSP的1个16位字等效为PC机串口传送的1个8N1模式数据(1个起始位+8个数据位+1个停止位)的1位。PC机串口每发送1个位的数据,DSP采样16次暂存数据接收寄存器DRR10(地址为21h)中。例如PC机通过RS232串口传送数据为‘1’,则DRR10经过16次采用后接收一个字的数据为‘FFFFh’,同理若前者后‘0’,则后者为‘0000h’。之后触发 McBSP0串口接收中断,DSP执行中断服务程序将DRR10中的有效数据(除去起始位和停止位)取走至内存中,并对计数器加1。当接收到一个完整的帧后,DSP置串口数据解码标志位为‘1’,DSP开始运行解码程序,将‘FFFFh’和‘0000h’分别等效为一个比特位‘1’和‘0’,从而恢复出原始的数据帧。

当DSP对接收到的数据完成加密之后需要反馈输出,TMS320VC5410串口数据向PC机发送的过程与数据接收的过程正好相反。每帧数据都需要进行串口编码之后通过数据发送寄存器DXR10(地址为23h)发出。即把8位有效数据中的‘0’编码为‘0000h’,‘1’编码为‘FFFFh’,按照从低位到高位的顺序重新排列编码后的数据,并在帧首和帧尾分别添加起始位‘0000h’和结束位‘FFFFh’,将每组10个数据作为一帧信号发出。

图6显示了本文设计的加密系统的实验结果。通过PC机和RS-232串口发送字符 ‘11112222’的十六进制形式为‘3131313132323232’共 64 bit,TMS320VC5410 接收到 64 bit明文数据后,通过读取 IC卡中的 64 bit密钥‘3100000000000031’并对明文进行DES加密后,输出密文的十六进制形式为‘96B466D634DE9A2D’。结果显示系统工作稳定可靠,符合设计要求。

图6 加密系统实验结果Fig.6 Test result of the encryption system

4 结 论

本文采用SLE5542型IC卡存储密钥,TMS320VC5410中的McBSP引脚与卡片触点连接并实现对卡片的应答复位和内容的读取,同时通过RS232串口与个人PC机实时交换数据,接收PC机发送的明文并对其DES加密后反馈输出。由于McBSP的工作机制是同步串口,把其当作通用I/O口和异步串口使用时必须注意内部寄存器的设置和输入输出方向的设定。经软硬件调试,实验结果表明该方案完全可以满足大数据量的加密,合理使用了硬件资源,可以进一步升级扩展作为数据采集保密系统的加密模块。

[1]杨晓云.现代密码学[M].西安:西安电子科技大学出版社,2009.

[2]Mao W.现代密码学理论与实践[M].王继林,伍前红,译.北京:电子工业出版社,2004.

[3]彭启琮,李玉柏,管庆.DSP技术的发展与应用[M].北京:高等教育出版社,2007.

[4]张坤,张冠男,王树勋.McBSP在DSP与PC机通信中的研究与设计[J].电子设计应用,2003(7):28-30.ZHANG Kun,ZHANG Guan-nan,WANG Shu-xun.Research and design of McBSP used between DSP and PC communication[J].Electronic Design Application,2003(7):28-30.

[5]王爱英.智能卡技术[M].北京:清华大学出版社,2000.

[6]Texas Instruments.TMS32OVC5410 fixed-point digital signal processor datasheet[EB/OL].(2008-10-01)[2010-03-08].http://focus.ti.com/lit/ds/symlink/tms320vc5410a.pdf.