I2C总线接口的设计及验证

2009-05-12戴立新王泽勇王黎高晓蓉赵全轲

戴立新 王泽勇 王 黎 高晓蓉 赵全轲

摘 要:在视频采集时,摄像机输出的模拟信号需要转换为数字信号,SAA7113芯片可以实现这种模/数转换功能。介绍在开发FPGA图像采集功能时,I2C总线模块的设计思路,并利用Verilog HDL语言实现I2C总线接口的功能;同时利用I2C总线对SAA7113芯片进行配置,为实现视频图像的模/数转换和图像采集搭建环境,在设计SAA7113模块状态机时有意缩小SAA7113寄存器的配置范围,从而节省配置时间。

关键词:I2C总线;Verilog HDL;FPGA;SAA7113

中图分类号:TP334文献标识码:B

文章编号:1004 373X(2009)02 136 03

Design and Verification of I2C Bus Interface

DAI Lixin,WANG Zeyong,WANG Li,GAO Xiaorong,ZHAO Quanke

(College of Sciences,Southwest Jiaotong University,Chengdu,610031,China)

Abstract:When collecting the video image,the analog signals output from the camera need to be converted into digital signal,and SAA7113 chip can realize such analog/digital conversion.The design idea of I2C bus module is introduced when exploiting the image collection function of FPGA.The function of I2C Bus interface is realized by using Verilog HDL language,also the SAA7113 chip is configured through I2C Bus,which builds an environment for the collection and analog/digital conversion of video image.When designing the state machine of SAA7113 module,the disposition range of SAA7113 register is purposively reduced,thus the time of disposition is decreased.

Keywords:I2C bus;Verilog HDL;FPGA;SAA7113

0 引 言

常规的图像采集处理系统利用图像采集卡采集图像到硬盘,再利用计算机以软件方式完成图像处理分析的任务。由于目前计算机自身性能的限制,完成数字图像处理的速度有限,不能达到实时处理的目标。如果采用FPGA处理,将会大大提高处理速度,同时达到实时处理的目标;由于在摄像机端实现了图像信息的数字化,因此图像抗干扰能力强,图像的传输距离进一步增加。这里所做的工作是数据采集的一部分,是后续图像处理的基础,因此具有十分重要的意义。

1 I2C总线

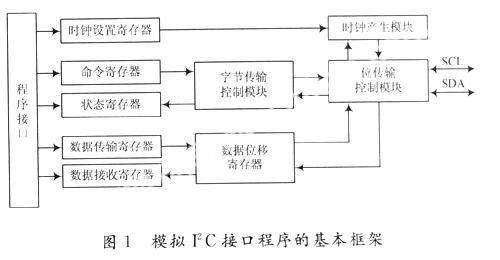

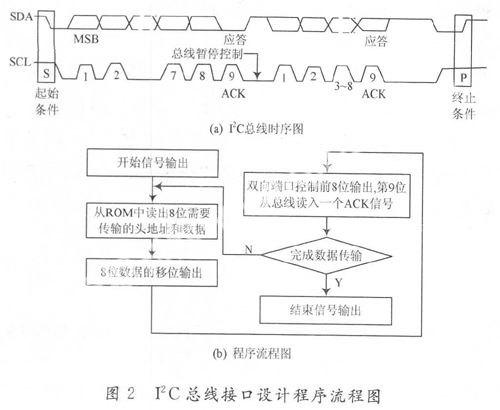

图1为模拟I2C接口程序的基本框架。程序接口用于与应用程序连接,将应用程序的数据按照I2C协议的方式通过SDA传递给外部器件;时钟设置寄存器用于设置时钟信号;时钟产生模块产生4倍SCL频率的时钟信号,它为位传输控制模块中所有同步动作提供触发信号;命令寄存器决定是否在总线上产生各种时序信号等;状态寄存器用来显示当前总线的状态;数据传输寄存器用于保存等待的数据;数据接收寄存器用于I2C总线接收到的最后一个字节内容;数据移位寄存器保存的数据总是与当前的数据传输相关的;字节传输控制模块以字节为单位控制数据传输;位传输控制模块以位为单位进行数据传输和产生各个I 2C协议命令。图2为I2C总线接口设计及程序流程图。I2C总线为双向同步串行总线,分SDA(串行数据线)和SCL(串行时钟线)两种。

1.1 I2C总线接口设计的具体实现

I2C总线接口设计所需的编程模块有:位传输控制模块和字节传输控制模块。编写以上2个模块时还要编写程序主体部分。程序主体部分完成与外部程序的接口;完成与总线上外部节点的连线;完成程序内部各个( I2C总线接口程序框架图中)寄存器的构建;控制字节传输控制模块等功能。

1.2 波形仿真测试图

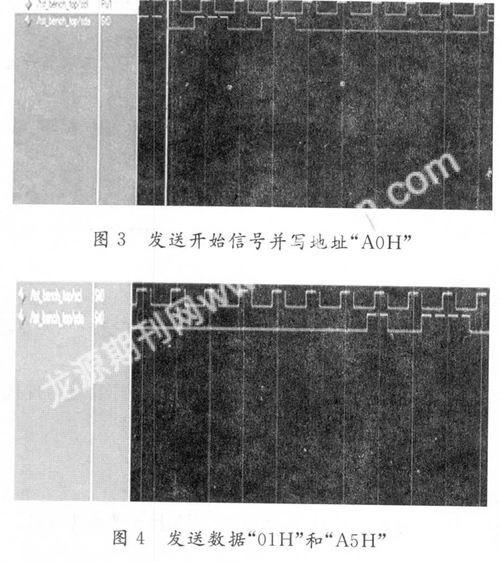

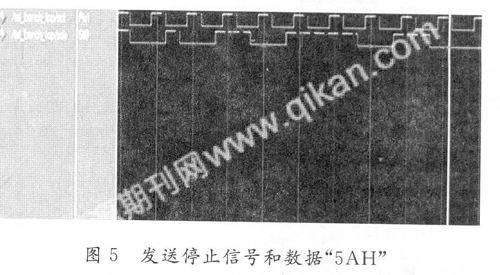

在ModelSim中可以看到仿真的结果。I2C在SCL高电平期间发送单比特数据,低电平期间允许总线上改变信号。图3~图5分别在SCL为高位“1”时,读SDA上的数据,在第9个SCL高电平期间发出应答信号。图中相关数据(A0H,01H,A5H,5AH)是编程时预先输入的地址数据,仿真图验证了本设计程序的正确性。进一步说明I2C程序符合I2C协议的时序和数据格式,可以实现模拟I2C协议的任务。进而完成了总线的接口设计。

2 SAA7113配置

2.1 SAA7113初始化配置值

在用FPGA来实现对SAA7113配置之前,首先必须确定其内部各寄存器的配置值。SAA7113H有256个内部寄存器(Subaddress:00~FFH),其中00H芯片版本信息寄存器是只读的。01H~05H是前端配置状态寄存器。06H~13H,15H~17H是解码部分的工作方式配置寄存器。11H~13H是输出控制寄存器,1FH是只读的解码状态寄存器。40H~60H,60H~62H是行/场图像控制、状态寄存器,用于设置VPO的数据格式等。内部寄存器14H,18H~1EH,20H~3FH及63H~FFH保留使用。在设计时SAA7113大部分寄存器的值采用其默认值“00H”,以“01H”和“40H”为起始地址从SAA7113_ROM取出配置数据分两组对SAA7113进行配置,两组配置数据结束地址分别“17H”和“5FH”。

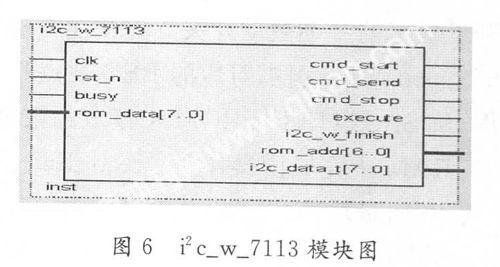

图6为i2c_w_7113模块原理图,其主要接口信号定义如表1所示。

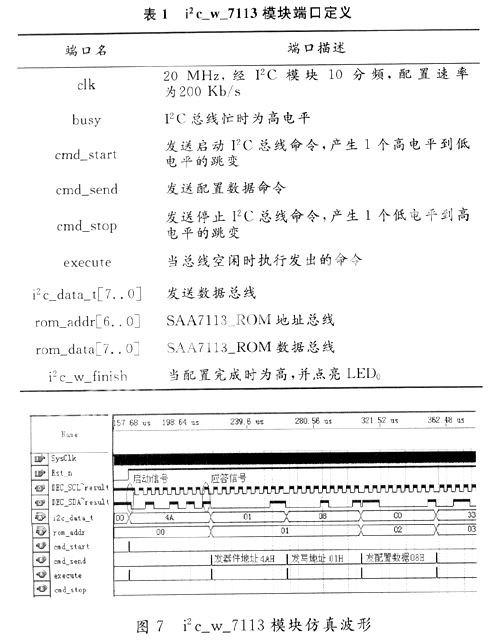

图7是i2c_w_7113模块功能仿真波形图。从图7中可以看出,当发出总线启动命令cmd_start(对应1个高电平脉冲)时,在SCL高电平期间,SDA线上产生1个从高电平到低电平的跳变以启动总线。随后立即发送器件寻址字节,SAA7113的器件地址是4AH,每个I2C器件都有1个惟一的器件地址号,当总线上有多个I2C器件连接时,I2C接口控制器根据这个惟一的地址号来寻址相应的器件。I2C在SCL高电平期间发送单比特数据,低电平期间允许在总线上改变信号。它先发送字节数据的最高位,从图中可以看出,4AH在总线上的比特流为0100_1010,当发送完8位数据且SAA7113正确接收后,在第9个SCL高电平期间SAA7113发出应答信号将总线拉低,即在SDA线上呈现低电平。

2.2 下载验证

整个设计功能仿真通过后就可以下载到FPGA进行实际验证了。对SAA7113的读写操作是通过saa7113_write和saa7113_read两个控制钮实现的,它们对应开发板上的2个微动开关。先使能写操作,完成配置后i2c_write_fine引脚对应的LED被点亮;然后使能读操作,从SAA7113 E2PROM中读取的数据被存入SAA7113_RAM中完成读操作i2c_read_fine引脚对应的LED被点亮;最后在JTAG模式下利用Quartus的In-System Memory Content Editor来查看SAA7113_RAM中的数据。

3 结 语

在进行基于FPGA的硬件图像采集处理系统的视频采集部分的研究时,摄像机输出的模拟信号需转换成数字信号,而SAA7113芯片可以实现转换功能,在此通过I2C总线的接口设计并在实现对SAA7113配置的基础上实现该功能。在设计i2c_w_7113模块状态机时,有意缩小SAA7113寄存器的配置范围,从而节省配置时间。这里所做的工作是数据采集的一部分,是后续图像处理的基础。

参考文献

[1]刘韬,楼兴华.FPGA数字电子系统设计与开发实例导航[M].北京:人民邮电出版社,2005.

[2]何立民.I2C总线应用系统设计[M].北京:北京航空航天大学出版社,1995.

[3]杜慧敏.基于Verilog HDL的FPGA设计基础[M].西安:西安电子科技大学出版社,2006.

[4]袁本荣.用Verilog HDL 进行FPGA设计的一些基本方法[J].微计算机信息,2004,20(6):93-95.

[5]应芳琴.基于I2C总线的视频信息采集系统的IP核设计[D].杭州:浙江工业大学,2005.

[6]Bruce J W.Personal Digital Assistant (PDA) Based I2C Bus Analysis[J].IEEE Transactions on Consumer Electronics,2003(11):1 482-1 485.

[7]马向前.基于FPGA的实时图像采集和去噪系统的研究与设计[D].长春:吉林大学,2006.

[8]常晓明.Verilog-HDL工程入门[M].北京:北京航空航天大学出版社,2005.

[9]林灶生.Verilog FPGA芯片设计[M].北京:北京航空航天大学出版社,2006.

[10]王前.吴淑泉.刘喜英.基于FPGA的I2C总线接口实现方法[J].微电子技术,2002(3):41-43.