基于FPGA的交通灯控制器实验设计

2009-05-11郭耸武俊鹏付小晶

郭 耸 武俊鹏 付小晶

文章编号:1672-5913(2009)08-0099-02

摘要:本文针对计算机硬件课程抽象、难于理解以及学生对其兴趣不高等现状,给出了基于FPGA的交通灯控制器实验设计,将生活中的实际应用与学生所学的硬件理论知识联系起来,极大程度地激发了学生对计算机硬件知识学习的兴趣,促进了硬件课程教学的顺利进行。

关键词:交通灯控制器;FPGA;VHDL;实验项目研究

中图分类号:G642

文献标识码:B

1引言

计算机硬件课程是高等院校计算机科学与技术专业的必修课,这些课程比较抽象,难于理解,因此实验教学起着至关重要的作用。学生通过实验可以对比较抽象的元器件及硬件电路加深理解。同时一些学生对计算机硬件的学习不感兴趣,认为硬件课程用途不大。针对这些,本文给出了基于FPGA的交通灯控制器实验项目设计,将生活中的实际应用与学生所学的硬件理论知识联系起来,让学生感到学有所用,极大程度地激发了学生对计算机硬件知识学习的兴趣,从而促进了硬件课程教学的顺利进行。

可编程器件的广泛应用,为数字系统的设计带来了极大的灵活性。由于可编程器件可以通过软件编程对硬件的结构和工作方式进行重构,使得硬件的设计如同软件设计那样快捷方便。通常使用硬件描述语言,进行数字电子系统设计。用软件设计方法来完成硬件电路的设计,非常容易上手,消除了学生对硬件实验的畏惧感。

本实验使用VHDL语言进行设计,采用自顶向下的设计方法,容易让学生理解和掌握。

2实验相关技术与开发环境

2.1FPGA技术

FPGA(Field Programmable Gate Array)即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA的使用非常灵活,同一片FPGA通过不同的编程数据可以产生不同的电路功能。FPGA在通信、数据处理、网络、仪器、工业控制、军事和航空航天等众多领域得到了广泛应用。随着功耗和成本的进一步降低,FPGA还将进入更多的应用领域。

2.2QuartusII开发环境

Altera的QuartusII设计软件提供一个非常容易适应特定设计所需要的完整的多平台设计环境。它是一个可编程片上系统(SOPC)设计的综合性环境。QuartusII软件包括FPGA设计所有阶段的解决方案。其设计流程包括设计、综合与适配、仿真测试、优化设计和编程下载等。

2.3VHDL语言

VHDL(Very-High-Speed Integrated Circuit Hardware Description Language)超高速集成电路硬件描述语言是IEEE的工业标准硬件描述语言。VHDL具有极强的描述能力,是最具推广前景的硬件描述语言(HDL)。

VHDL具有如下优点:

(1) VHDL是一门标准化语言,它是一种通用优化设计程序语言,已被电子设计界公认为标准的设计语言。

(2) VHDL是一门设计输入语言,它可将复杂的硬件电路运行过程以源程序的形式输入到数字电路设计系统中,进行系统仿真、自动综合。

(3) VHDL是一门网表语言,它的语言结构使它可在计算机的设计环境中,是不同设计工具间相互通讯的一种低级格式,即生成的门级网表文件,可相互替换、兼容。

(4) VHDL是一门测试语言,VHDL 在进行数字电路设计描述的同时,建立测试基准,对所设计的数字电路进行功能模拟和仿真,以验证所设计电路是否满足功能与时序需求。

(5) VHDL是一门可读性语言,既可被计算机接受,也易被人所理解,它具有良好的可读性,易于修改和发现错误。

3实验设计

3.1实验预期目标

在两条干道的汇合点形成十字交叉路口,假设东西方向为主干道,南北方向为支干道。为确保车辆安全,迅速地通行,在交叉道口的每个入口处设置了红,绿,黄色信号灯。

实验具体要求如下:

(1) 主干道绿灯亮时,支干道红灯亮,反之亦然。两者交替通行,主干道每次放行T1s,支干道每次放行T2s。每次由绿灯变为红灯的过程中,黄灯亮T3s作为过渡。这里要求主干道放行时间要大于支干道的放行时间,即T1s>T2s。

(2) 能实现正常的倒计时显示功能。

3.2实验设计方案

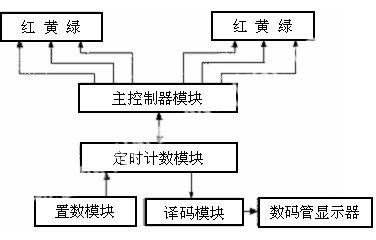

交通灯控制器原理框图如图1所示,包括主控制器模块、置数模块、定时计数模块和译码器模块。主控制器模块是交通灯控制器的核心部分。置数模块将交通灯的点亮时间预置到置数电路中,定时计数模块以秒为单位倒计时,当计数值减为零时,主控电路改变输出状态,电路进人下一个状态的倒计时。

图1 交通灯控制器原理框图

3.2.1主控制器模块

依设计要求,可画出交通灯点亮规律的状态转换表,如表1所示。

为了提高学生的独立自主创新能力,给学生更多的设计和发挥空间,教师只是做适当的引导,让学生根据状态图自行完成主控制器模块的设计及其VHDL实现。这样可以更大程度地锻炼学生设计能力。

表1 交通灯点亮规律状态转换表

3.2.2置数模块,定时计数模块,译码模块

由于要进行T1s,T2s,T3s三种定时,本实验采用一个置数模块由主控制器模块输出的信号对定时时间的选择进行控制。

定时计数模块采用倒计时的方式,由主控制器模块输出的信号控制定时的开始,定时时间结束时输出定时时间结束信号到主控制器模块,通过主控制器模块控制交通灯的开、闭。

译码模块对定时计数模块输出的信号进行译码,输出译码信号;并与数码管相连,由数码管显示器显示当前计数值。

3.2.3顶层原理图设计

本实验的各个模块要求学生用VHDL语言来编程实现,总系统则可以采用原理图实现,学生可以把各个模块定制成元器件,然后再把各个器件相连组成交通灯控制系统。整个过程中,教师只是给出实验要求和设计思路,其他的工作都是由学生自主完成,可以极大程度培养学生的独立思考、自主创新和实践动手能力。

4结束语

本文根据学院具备的实验器材,设计了基于FPGA的交通灯控制器实验系统。该实验锻炼了学生的实践动手能力,加深了学生对理论知识的理解。同时,该实验将实际应用与学生所学的专业知识紧密地联系起来,使学生感到学有所用,极大程度地激发了学生的积极性和主动性,增强了学生学习的自主性和实战性。

参考文献:

[1] 杨贵,郑善贤. 基于FPGA的交通灯控制器实现[J]. 中国仪器仪表,2003(9):41-43.

[2] 孙仁云,李本亮,罗永国. 基于交通灯系统的单片机教学实验[J]. 实验科学与技术,2003(2):26-29.

[3] 翟殿棠,方敏,厉光伟. 基于VHDL 的交通灯控制器设计[J]. 现代电子技术,2007(3):187-188.