基于UART Ip核实现嵌入式微处理器扩展多串口电路的设计

2009-04-09方明林建中

方 明 林建中

[摘要]给出利用FPGA上实现的UART IP核,实现在微处理器S3C2440A总线上动态扩展多串口电路,论述基于发送和接收FIFO下的UART接口模块设计以及各主要功能模块实现。另外,给出节省中断资源的用于实现串口动态扩展的电路。最后,给出WINCE5.0下多串口设备驱动程序的实现框架。

[关键词]UART S3C2440A WINCE 5.0

中图分类号:TP3文献标识码:A文章编号:16717597(2009)0310015-03

一、引言

由于基于FPGA/CPLD实现的电路在灵活性,体积,成本方面都有其优势。本文从实际应用的角度出发,为了满足高速数据传输要求,利用FPGA实现了分别拥有512字节的发送和接收FIFO的UART接口模块,并采用接口电路动态扩展UART,以实现微处理器S3C2440A上实现扩展多串口的目的,在最少改动电路下满足要求高速传输的多串口场合。同时,本文还给出了在嵌入式操作系统WINCE5.0下的多串口驱动实现过程。

二、硬件电路总体设计

硬件电路实现如图(1)所示,主要有微处理器S3C2440A,两片缓冲器74LVTH162245分别用于地址总线/片选和数据总线的缓冲,以及一块FPGA模块组成。微处理器是三星32bit ARM920T内核的S3C2440A,其主频在400MHZ,最高可达533MHZ,可扩展外部存器,具有丰富的I2C,SPI,CAN,以太网,USB等控制接口,还可通过总线扩展其他接口电路,应用层面非常广泛。而FPGA模块的功能是使用VHDL实现了UART IP核以及多串口扩展控制电路,该控制电路通过产生多个串口的片选以及通过微处理器的1个GPIO口作为中断使能信号来高效管理多个串口中断共用一个中断的有效方法来实现多串口的扩展,通过这不仅节约了中断资源,同时,也保证了多个串口中断的无漏检测和服务。另外,通过电平转换芯片,如MAX232,MAX485,MAX491它们可以分别实现RS232,RS485以及RS422接口串口。

(一)微处理器S3C2440A资源分配

S3C2440A中的内存控制器提供了要求外部内存访问的内存控制信号,总共有8个块,地址从0x0000_000~0x4000_0000,每个块的大小为128MB,6个块可以用于扩展ROM,SRAM,其他两个用于ROM,SDRAM。每个块都有一个片选信号nGs0~nGs7,当某块的片选信号有效时,就可以通过读写信号访问该块数据。在扩展多串口的电路,我们采用了第6块内存块,地址从0x2800_0000~0x3000_0000,片选信号为nGs5,来作为访问多串口数据的区域。

(二)UART IP核的设计

采用硬件描述语言VHDL,在ALTERA公司的现场可编程门阵列(FPGA)上实现了拥有512字节接收和发送FIFO的软件上兼容16550的UART核。在UART IP核中主要由读写控制模块,寄存器和发送/接收FIFO模块,接收模块,发送模块,波特率发生器以及中断控制产生模块组成。图(2)显示了UART的数据发送/接收的格式,从CPU端和设备端看,UART接收部分实现在设定波特率下将设备端的串行数据转换成并行数据给CPU,而发送部分实现将CPU端的并行数据转换成串行数据再以设定的波特率发送给设备。其中,在设备端的数据帧格式中,起始位为两个比特宽度,用于在UART接收时的辨别一帧数据开始的判断;通过对UART内部寄存器的配置,可以将配置数据位数5~8位,是否有校验位和校验类型,以及停止位的位数为1或1.5或2。

1.UART实现的各功能描述

(1)读写控制模块主要负责处理与系统处理器那边的通信,所有内部寄存器的读和写通过这个模块完成。

(2)UART寄存器模块处理所有内部寄存器,其他模块的寄存器信息在这个模块中被汇集并且对所有块都可得到。

(3)接收模块接收串行数据,通过预先设置可以识别数据宽度诸如5,6,7,8比特,不同的校验设置比如寄校验,偶校验或无校验,以及不同的停止位诸如1,1.5,2比特。该模块还对接收数据流进行错误检测诸如溢出错误,帧错误,校验错误以及超时错误。如果接收数据没有错误,将其数据放入接收FIFO中。

(4)中断控制模块依赖发送FIFO的状态和它的发送的和接收的数据的状态来发送一个中断信号给处理器。

(5)波特率发生器将输入的时钟信号除以一个可编程的数值,再将其接口除以16就得到了发送和接收用的波特率。

(6)发送模块处理将发送的数据写入到发送FIFO中,并且按照UART的数据格式再数据发送的时候加上开始位,校验位以及停止位,这样保证接收设备可以做适当错误处理和接收。

2.发送模块实现

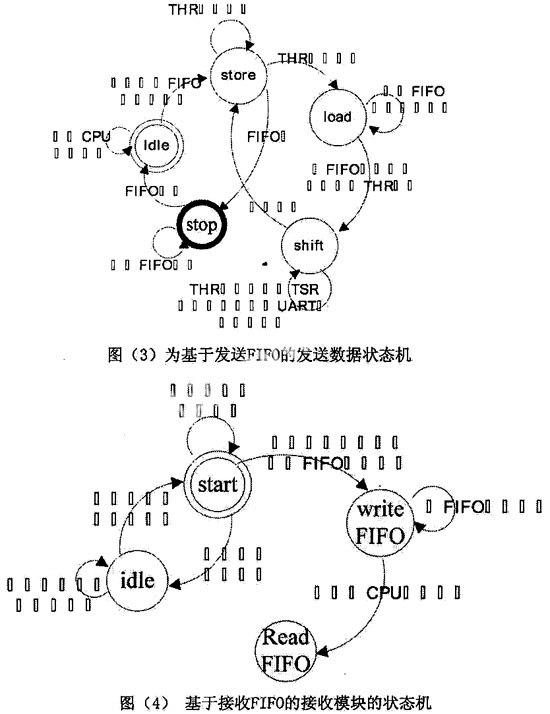

由于微处理器在较高时钟频率上发送数据给UART,为了保证UART在发送保持寄存器(THR)中的数据不被后一帧数据给覆盖,在UART中设计了容量为512字节的发送FIFO,基于FIFO设计的发送数据有限状态机如图(3)所示,一开始,发送FIFO处于空的状态,通过使能FIFO写入信号将数据先放入FIFO(只要FIFO处于非全满状态将一直可以接收来自CPU的数据)。然后,通过地址、片选和写控制信号读取发送保持寄存器的状态,当判断其为空时,在第一时钟周期先使能FIFO读取信号,将FIFO中的一个数据先放在总线上,然后在后面的时钟周期里产生UART的写控制信号,将放在总线上的数据写入到UART的发送保持寄存器,再通过移位寄存器将数据按波特率发送到设备接收端。这样做即可保证发送数据的完整性,同时提高了数据的发送速度。

3.接收模块实现

当处理器由于某种原因,导致在接收来自外部串行设备的数据不被后面的数据给覆盖,在设计中采用了一个512字节的接收FIFO来缓冲接收数据。图(4)显示了基于接收FIFO的接收模块的状态机,当UART检测到起始数据位并将接收到的一帧完整数据去除开始位,校验位和停止位后放入接收缓冲寄存器(RBR),然后,发出接收数据准备信号(TXRDY置位),接着在第一时钟周期产生访问UART的读信号(RDn)将其RBR中的数据读到接收FIFO输入数据线上,在随后时钟周期里再使能接收FIFO写入信号,将FIFO输入数据线上的数据存到FIFO中。当接收FIFO中的数据达到FIFO触发等级(在FIFO控制器中预先设置了触发中断数,通常是1,4,8,14个字节)时发送中断信号给处理器请求接收数据,这时当接收到处理器的读信号有效时,就产生接收FIFO的读取使能信号,将FIFO中的数据按照先入先出的方式放到外部数据总线上以让处理器读取。

(三)多串口扩展控制电路

该电路主要负责对扩展的UART进行片选控制,以及通过微处理器的1个GPIO口作为中断使能信号来高效管理多个串口中断共用一个中断。为了选种扩展的UART,通过处理器的地址访问片选信号nGs5以及地址线addr[15..3]来译码器产生UART的片选信号。对扩展四个UART来说,其地址依次为0x001x,0x002x,0x003x,0x004x。另外中断使能信号(inten)的地址为0x0100。各UART中断采用或运算合并产生一个中断,当中断使能信号有效时,发送中断给处理器。在硬件驱动层处理器响应中断并进入中断服务程序,在中断服务过程中,处理器按顺序逐个检查多个扩展口的串口中断源,有中断请求的就给予服务,并置中断使能信号(inten)无效。当刚刚检测过的中断又出现时,一方面靠扩展控制电路中的移位寄存器将INTR锁存,另一方面,扩展控制电路中的8位状态机保证了一定的延时,使得上一中断服务顺利完成,完成后再将中断使能信号(inten)变为有效以接收后续的中断。在延时中,中断控制程序把堆栈中的内容返回给处理器的寄存器,恢复能获得的响应。这样,即使在多个串口中断密集发生的环境下,扩展的多个串口仍可获得实时性和可靠性较高的中断。具体VHDL实现代码如下:

con_pro : process(nreset,clk)

begin

if ngcs5='0' and a(15 downto 3)="0000000000010" then cs(0)<='1'; else cs(0)<='0';

end if;--片选UART1

if ngcs5='0' and a(15 downto 3)="0000000000100" then cs(1)<='1'; else cs(1)<='0';

end if;-- 片选UART2

if ngcs5='0' and a(15 downto 3)="0000000000110" then cs(2)<='1'; else cs(2)<='0';

end if;-- 片选UART3

if ngcs5='0' and a(15 downto 3)="0000000001000" then cs(3)<='1'; else cs(3)<='0';

end if;-- 片选UART4

add<=a(2 downto 0);--访问UART内部寄存器地址

reset<=not(nreset);--复位UART信号

if ngcs5='0' and a="0000000100000000" then

lck_sel<='1';

else lck_sel<='0'; end if;--中断使能信号

if nreset='0' then LCK<='0';

elsif rising_edge(nwe) then if lck_sel='1' then dffin<=data(0);-- 数据输入到中断锁存寄存器 LCK<='1';-- 中断锁存寄存器时钟信号

elseLCK<='0'; end if; end if;

if rising_edge(clk) then

if(inten='1') then

intr<= not(inta or intb or intc or intd );--中断(inta,intb,intc,intd 分别为四个UART的中断信号)

elseinter<='1'; end if; end if;

end process con_pro;

// 中断有限状态机

Interput_Proc: process(nreset,clk10k)

begin

if (nreset='0') then State <= s0;

elsif rising_edge(clk10k) then

case State is

when s0 =>

if (inten='1') and (intr='0') then

State <= s1;--产生中断

else State <= s0; end if;

when s1 =>

if (inten='0') then

State <= s2; --中断使能无效

else State <= s1; end if;

when s2 =>

if (inten='1') then--中断服务完成,置中断使能有效

State <= s3;

else State <= s2; end if;

// 延时50US保证中断服务程序完全退出

when s3 => State <= s4;--10us

when s4 => State <= s5;--10us

when s5 => State <= s5;--10us

when s6 => State <= s7;--10us

when s7 => State <= s0;--10us

when others => State <= s0;

end case; end if;

end processInterput_Proc;

end beha;

三、WINCE5.0下实现多串口驱动

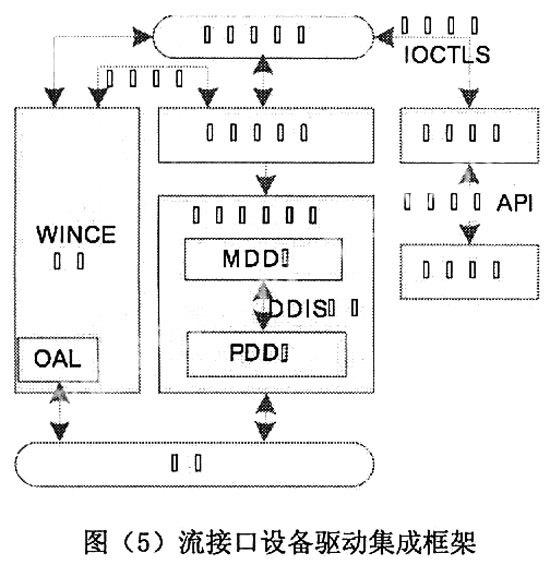

在WINCE 5.0下开发的设备驱动有两种模式:本机设备驱动和流接口设备驱动。而本系统的多串口设备驱动采用流接口设备驱动方式,它以动态链接库(DLL)即文件系统的一个特殊文件形式来实现把外设使用传递给应用程序。图(5)显示了其设备驱动如何下WINCE5.0操作系统中集成的,其中,设备驱动程序分为两层,上层是模型设备驱动驱动程序(MDD),该层驱动对平台和函数来讲是通用的,即是源代码也是库,负责链接PDD层并定义它希望调用的函数以及把不同的函数集提供给设备管理器来统一加载、管理和卸载,这些函数集叫流接口函数;而下层是依赖平台的设备驱动程序(PDD),它是直接访问硬件的驱动程序,同时通过设备驱动程序提供器接口(DDIS)接口提供给MDD层调用。

每一个流接口驱动程序必须实现一组标准的函数,用来完成标准的文件I/O函数和电源管理函数,这些函数提供给WINCE操作系统内核使用,由于篇幅的限制这里只列出多串口流接口驱动程序要实现的DLL接口:COM_Close它是在串口驱动关闭是应用程序通过CloseHandle( )函数调用这个函数;COM_Init它完成串口的初始化;COM_Open在打开一个串口驱动程序时应用程序可以通过CreatFile( )函数调用这个函数;COM_Deinit该函数完成串口驱动程序的卸载;COM_IOControl该函数用于向串口设备发送命令,应用层可以通过DeviceIOControl函数来通知操作系统调用这个函数;COM_Read()在串口处于打开状态时应用程序通过ReadFile( )函数调用这个函数来读取串口数据;COM_Write()在串口处于打开状态时应用程序通过WriteFile( )函数调用这个函数来向串口写入数据;COM_PowerDown由COM_Init创建时生产的句柄,系统挂起前调用这个函数;COM_PowerUp由COM_Init创建时生产的句柄,系统重新启动前调用这个函数。

四、总结

在FPGA上实现UART IP核,占用700个宏单元,共1万5千门系统设计,通过接口模块化设计的UART核来实现嵌入式微处理器动态扩展多串口电路的方法,有利于通过电路的最小更改来实现多串口的扩展,同时也减小开发周期和成本,该设计方法也可以作为其他电路设计的参考。

参考文献:

[1]邰铭、于洪涛,Windows CE.Net内核定制及应用开发,电子工业出版社,2004.

[2]董长富、郭超平、宋渝,基于FPGA的多串口模块的设计和实现,设计参考,2006,Vol.8 No.11.

[3]姜宁、范多旺,基于FPGA/CPLD的通用异步通信接口UART的设计,信息系统与信息化,2006年第1期.

作者简介:

方明,男,硕士,主研方向:嵌入式系统开发,集成电路设计;林建中,男,高级工程师,主研方向:计算机系统开发,集成电路设计。