基于51单片机I〈sup〉2〈/sup〉C总线串行通信的应用

2009-03-30黄灿胜

[摘要]介绍I2C总线技术及其技术标准。结合ATMEL公司具有I2C总线的AT24LCO4,给出AT89S51单片机虚拟I2C总线的硬件设计及软件实现。

[关键词]I2C单片机AT24LC04

中图分类号:TN91文献标识码:A文章编号:1671-7597(2009)0210034-02

一、引言

I2C总线是PHILIPS公司推出的一种双向二线制总线,它包括一条串行数据线(SDA)和一条串行时钟线(SCL)。总线中每个器件都有唯一的地址识别,而且都可以作为一个发送器或接收器。I2C总线是目前常见的一种智能化仪器仪表组成方案,但在很多小型仪表中,使用带有12C总线接口的高档单片机在经济上则是不合算的。51系列的单片机是我国目前流行的性价比高的微控制器之一,而大多数51系列单片机不具备与I2C总线的接口功能。本文以AT89S51单片机为例探究如何在51系列的单片机中实现I2C总线的串行通信和控制外围I2C总线的器件。

二、I2C总线系统结构及时序

(一)I2C总线组成

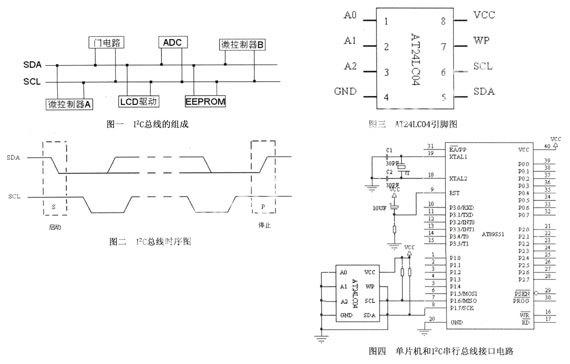

一个典型的I2C总线系统组成结构如图一所示,假设系统中器件均具有I2C总线接口,通过两根线SDA(串行数据线)和SCL(串线时钟线)连接到I2C总线,并通过总线行识别。

I2C总线的器件分为主器件和从器件。主器件的功能是启动在总线上传送数据,并产生时钟脉冲,以允许与被寻址的器件进行数据传送。任何器件均能成为从器件,只有微控制器才能成为主器件。I2C总线允许连接多个微控制器,先控制总线的器件成为主器件。数据在主、从器件间传送,结束后,主、从器件将释放总线,退出主、从器件角色。总线上存在主、从器件时,总线处于忙的状态,反之,总线处于空闲状态。

(二)I2C总线时序

所有主机在SCL线上产生自己的时钟来传输I2C总线上的数据,数据只在时钟的高电平周期有效,每传输一个数据位就产生一个时钟脉冲,数据线的高或低电平状态只有在SCL线的时钟信号是低电平时才能改变,当SCL为高电平时,SDA的改变表示“开始”和“停止”状态,即SDA由高电平转入低电平表示开始,该命令必须在其它命令前执行;SDA由低电平转入高电平表示停止状态,该命令可终止所有通讯。在开始条件后,SCL低电平期间,SDA允许变化,每位数据需一个时钟脉冲,当SCL为高时,SDA必须稳定,主控器在应答时钟脉冲高电平期间释放SDA线,转由接收器控制。相同总线上的设备在收到数据后,以置SDA为低电平的方式对其确认。总线不忙时,数据线和时钟线保持为高电平。I2C总线的时序如图二所示。

三、51单片机系统中I2C总线的实现

51系列单片机上并不带I2C总线,因此必须根据I2C总线的时序用单片机上的I/O口模拟I2C总线时序实现其功能。现以单片机应用系统中较为常见的E2PROM中AT24LC04为例,介绍在51系列单片机上利用普通I/O口实现I2C串行总线的方法和软件设计。

外围I2C器件选用AT24LC04是EEPROM。其具有512×8位的存储容量,工作从器件方式,其引脚排列如图三所示。

其中AO、A1和A2为地址选择输入端。单片机与AT24LCO4间进行数据传递时,首先传送器件的从地址SLA,START为起始信号,1010为AT24LCO4的器件地址,AO和A1由芯片的AO、A1引脚上的电平决定。

图四所示为AT89S51单片机和AT24LCO4的接口图,分别用I/O口P1.6、P1.7连接SCL和SDA总线。通过控制P1.6口的高低电平得到I2C的虚拟时钟,P1.7口作为数据传输的双向端口,作为单片机和AT24LCO4之间的数据线。

四、虚拟I2C总线软件结构

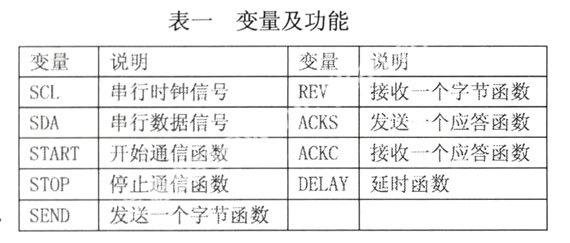

对于虚拟I2C总线来说要实现其功能主要是注意I2C器件的操作时序,总线的运行由主机控制。所谓主机即启动数据的传送即发出启动信号,发出时钟信号,传送结束时发出停止信号的设备,通常主机是微处理器。被主机寻访的设备都称为从机。这里AT89S51是I2C串行总线中的主器件;AT24LCO4是I2C串行总线的从器件。为了进行通讯,每个接到I2C总线的设备都有一个唯一的地址,以便于主机寻访。主机和从机的数据传送,可以由主机发送数据到从机,也可以是从机发到主机。凡是发送数据到总线的设备称为发送器,从总线上接收数据的设备被称为接受器。表一为程序中所使用的变量及功能。

为了保证严格的时序,需要采用汇编程序模拟12C串行时序。程序代码如下:

SCL EQU P1.6:定义端口

SDA EQU P1.7:

START:CLR SCL;开始信号的传递

SETB SDA;

ACALL DELAY;

SETB SCL;

ACALL DELAY;

CLR SDA;

ACALL DELAY;

CLR SCL;

RET;

STOP:CLR SCL;停止信号的传递

CLR SDA;

ACALL DELAY;

SETB SCL;

ACALL DELAY;

SETB SDA

ACALL DELAY;

RET;

SEND:MOV R0,#08H;发送一个字节

SENDO:RLC A:

MOV C SDA;

SETB SCL;

ACALL DELAY;

CLR SCL;

DJNZ R0.SENDO;

SETB SDA:

PET;

REV:MOV R0,#08H;接收一个字节

REVO:SETB SCL;

MOV C SDA;

RLC A:

CLR SCL;

DJNZ R7.REV0;

PET;

ACKC:SETB SCL;接收一个应答位

ACALL DELAY;

MOV C,SDA;

CLR SCL;

RET;

ACKS:SETB SCL;发送一个应答位

ACALL DELAY;

MOV C SDA;

CLR SCL;

PET;

DELAY:NOP;延时程序

NOP:

NOP;

RET;

五、结论

本文介绍了I2C总线的组成及时序,并以ATMEL公司的AT24LC04为例模拟I2C总线的时序的起始、停止及CPU向I2C总线的发送和接收数据。

基金项目:南校教研字(2007)第003号南宁师范高等专科学校科研项目经费资助。

作者简介:

黄灿胜,男,广西扶绥人,南宁师范高等专科学校,工程师,研究方向是单片机应用技术教学与研究。